1/0

INTERFACING

8.6.7.2

DECOUPLED

DUAL-PORT

MEMORY

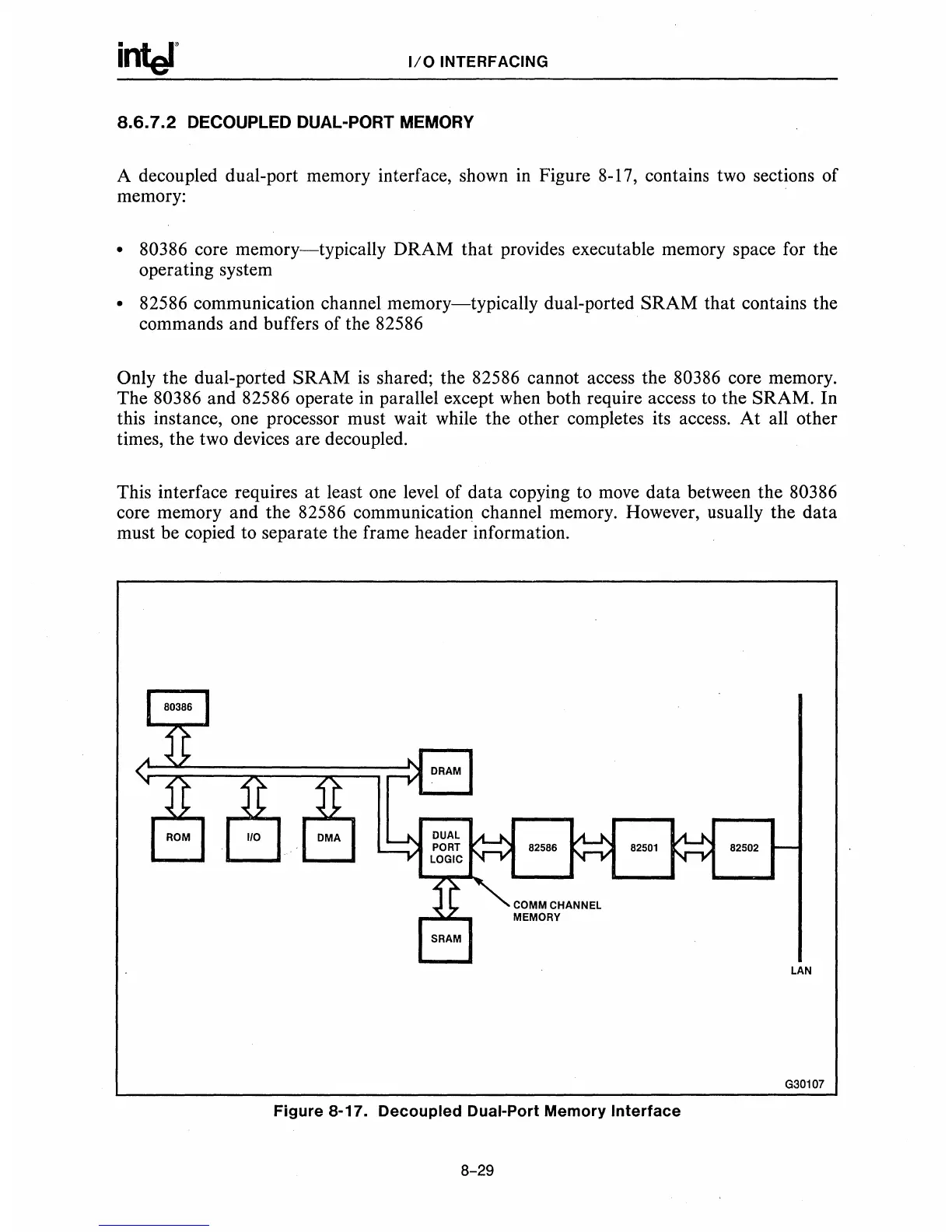

A decoupled dual-port memory interface, shown

in

Figure 8-17, contains two sections of

memory:

• 80386 core memory-typically DRAM that provides executable memory space for the

operating system

• 82586 communication channel memory-typically dual-ported SRAM that contains the

commands and buffers of the 82586

Only the dual-ported SRAM

is

shared; the 82586 cannot access the 80386 core memory.

The

80386 and 82586 operate

in

parallel except when both require access

to

the SRAM. In

this instance, one processor must wait while the other completes its access.

At

all other

times, the two devices are decoupled.

This interface requires

at

least one level of data copying to

move

data between the 80386

core memory and the 82586 communication channel memory. However, usually the data

must be copied to separate the frame header information.

82502

LAN

G30107

Figure

8-17.

Decoupled

Dual-Port Memory

Interface

8-29

Loading...

Loading...