CHAPTER 2

INTERNAL ARCHITECTURE

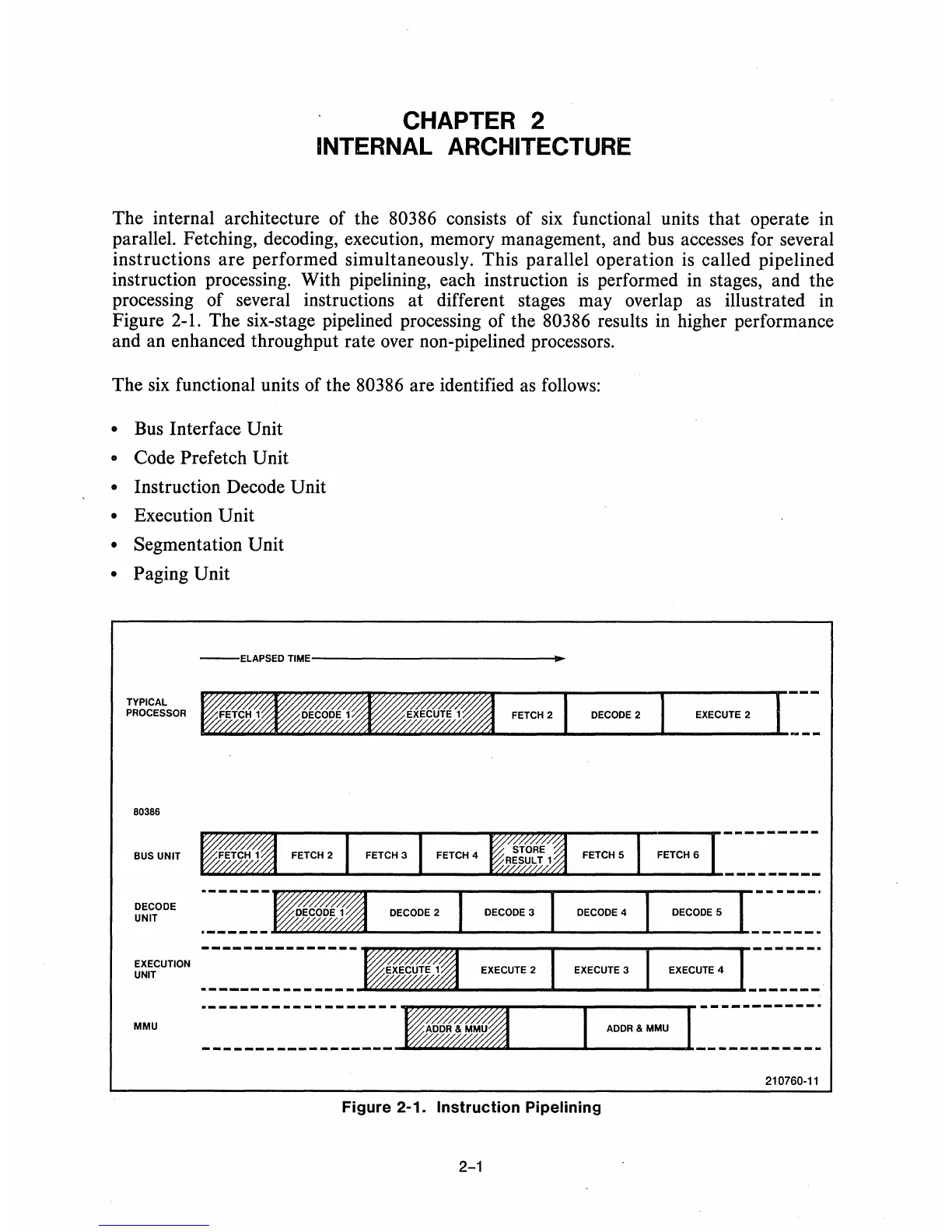

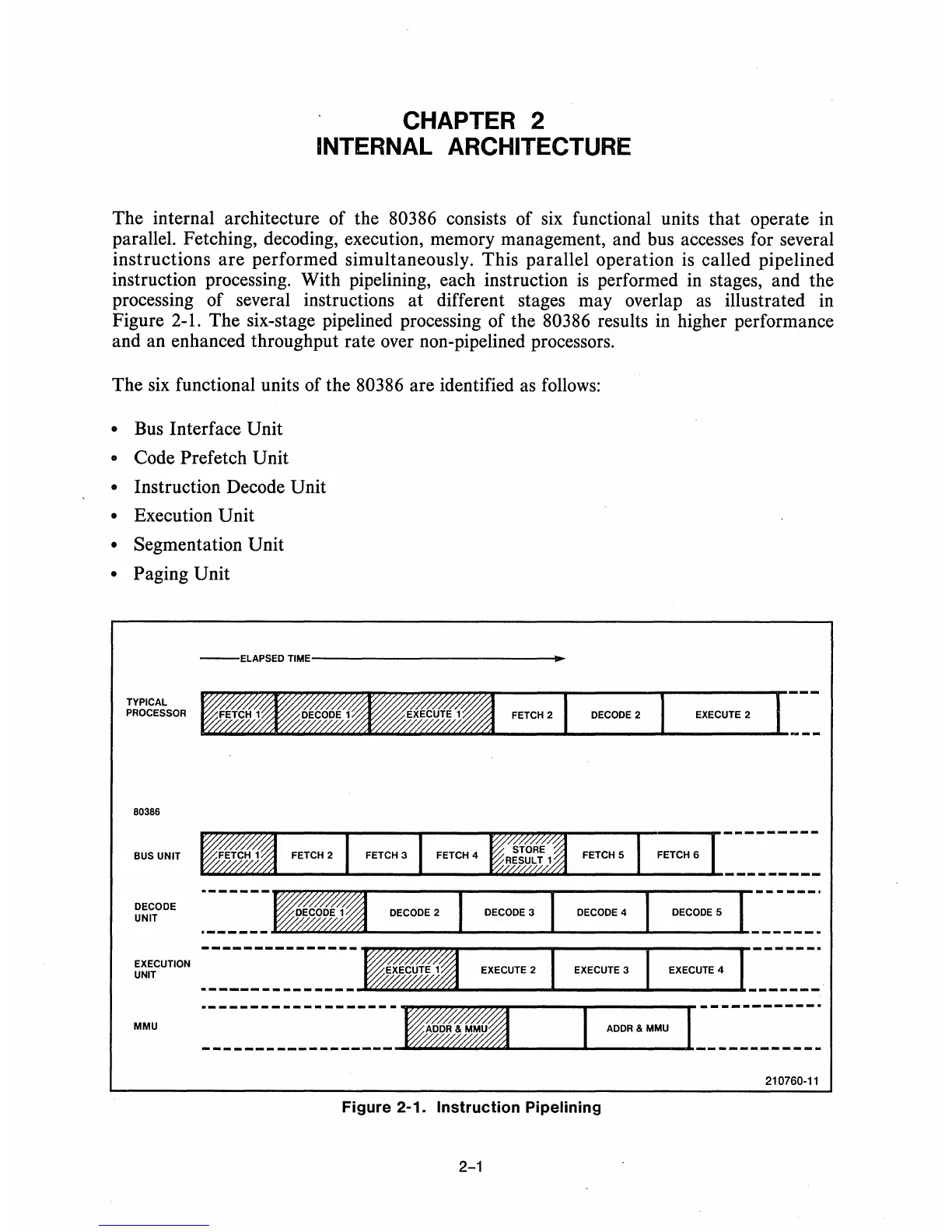

The internal architecture of the 80386 consists of

six

functional units that operate

in

parallel. Fetching, decoding, execution, memory management, and bus accesses for several

instructions are performed simultaneously. This parallel operation is called pipelined

instruction processing. With pipelining, each instruction

is

performed in stages, and the

processing of several instructions

at

different stages may overlap

as

illustrated

in

Figure 2-1. The six-stage pipelined processing of the 80386 results

in

higher performance

and an enhanced throughput rate over non-pipelined processors.

The

six

functional units of the 80386 are identified

as

follows:

• Bus Interface Unit

o Code Prefetch Unit

•

Instruction Decode Unit

o Execution Unit

•

Segmentation Unit

•

Paging Unit

TYPICAL

PROCESSOR

80386

BUS

UNIT

--ELAPSEDTIME------------

__

EXECUTE 2

~~~~~-------r-------,--------~------~------.

DECODE

UNIT

MMU

~~~

__

.l....-_

_1..

__

....l-_--L

______ .

EXECUTE 3

EXECUTE 4

I_-_-_-_-_-_-~

~-_-_-_-_-_-_~~~-_-_-_-_-_-_-_-_-

........

""'AD

..

~"R""&

..

M"M""U

....

_

__

.......

I--_AD_D_R_&_M_MU_

....

I

~~~~~~~~~~~~

210760-11

Figure 2-1. Instruction Pipelining

2-1

Loading...

Loading...