LOCAL

BUS

INTERFACE

32

DATA

BUS

(00-031)

80386

ADDRESS

BUS

(BEO#-BE3#.A2-A31)

JBSI6#

"HIGH"

32

DATA

BUS

(00-031)

ADDRESS

BUS

(BEO#-BE3#.

A2-A31)

16

DATA

BUS

(00-015)

32-BIT

MEMORY

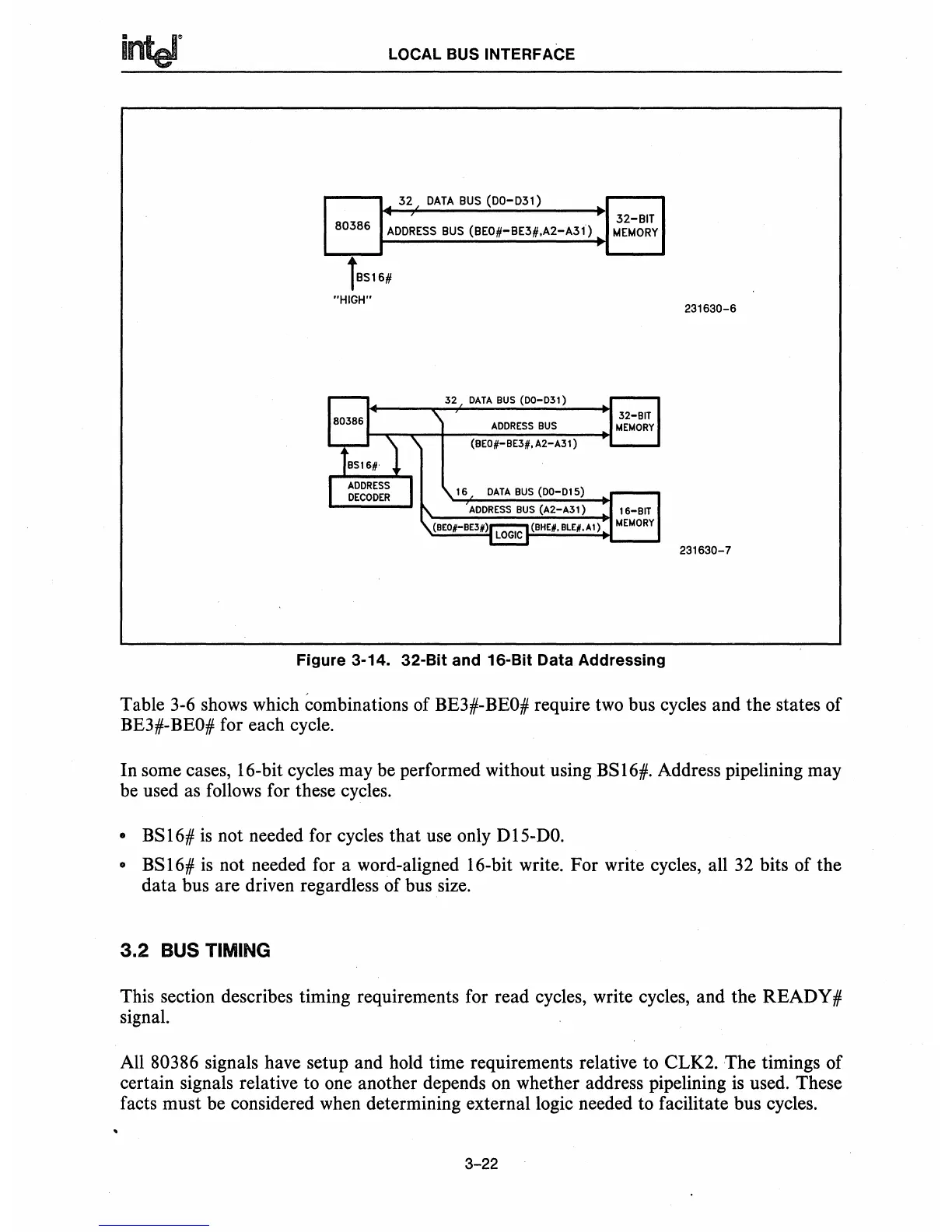

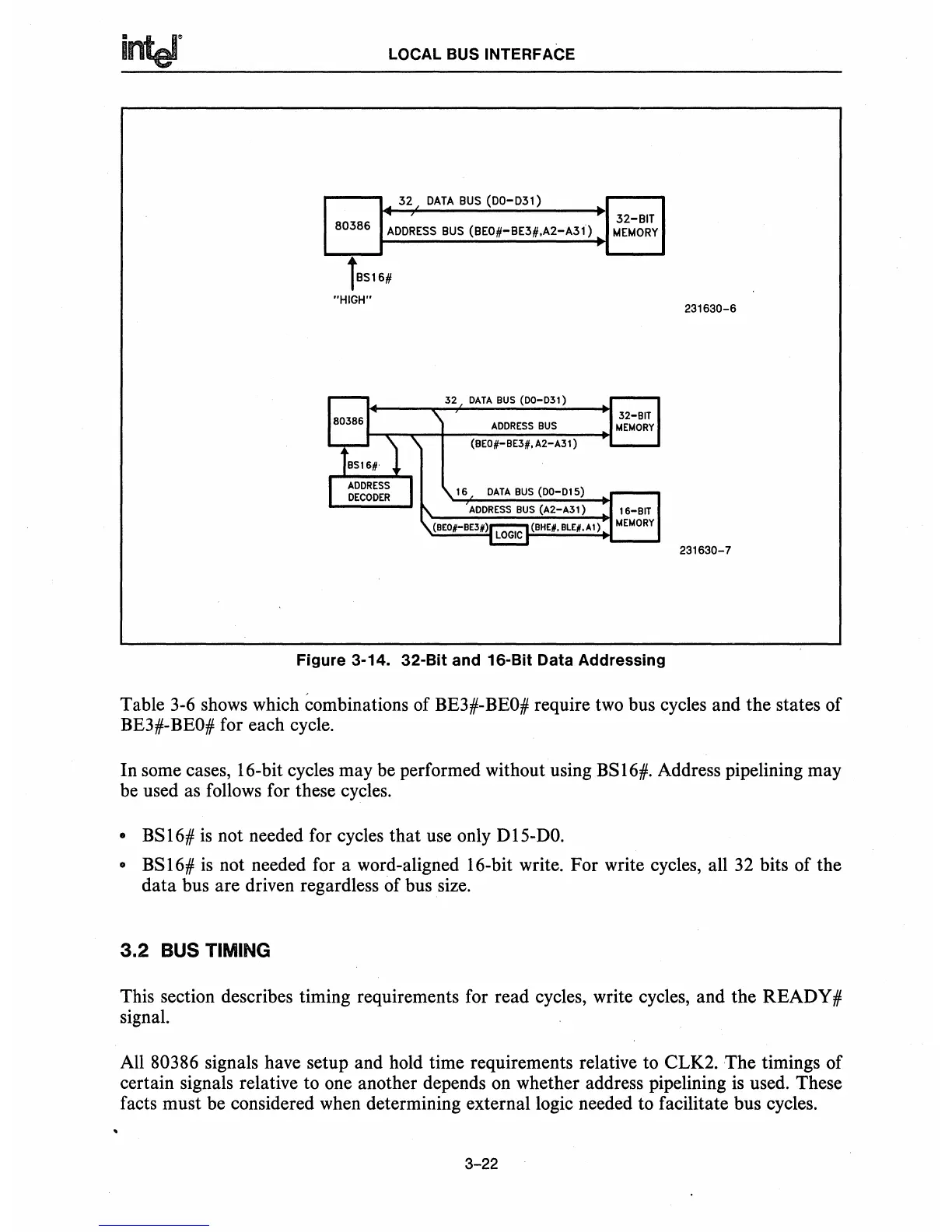

Figure 3-14. 32-Bit and 16-Bit Data Addressing

231630-6

231630-7

Table 3-6 shows which combinations of BE3#-BEO# require two bus cycles and the states of

BE3#-BEO# for each cycle.

In some cases,

I6-bit cycles may be performed without using BSI6#. Address pipelining may

be used as follows for these cycles.

•

BSI6#

is

not needed for cycles

that

use only DIS-DO.

G

BSI6#

is

not needed for a word-aligned I6-bit write. For write cycles, all

32

bits of the

data

bus are driven regardless of bus size.

3.2

BUS

TIMING

This section describes timing requirements for read cycles, write cycles, and the READY #

signal.

All

80386 signals have setup and hold time requirements relative to CLK2.

The

timings

of

certain signals relative to one another depends on whether address pipelining

is

used. These

facts must be considered when determining external logic needed to facilitate bus cycles.

3-22

Loading...

Loading...