Summary Tables of Changes

Intel

®

Core™2 Extreme Quad-Core Processor QX6000

Δ

Sequence and 15

Intel

®

Core™2 Quad Processor Q6000

Δ

Sequence

Specification Update

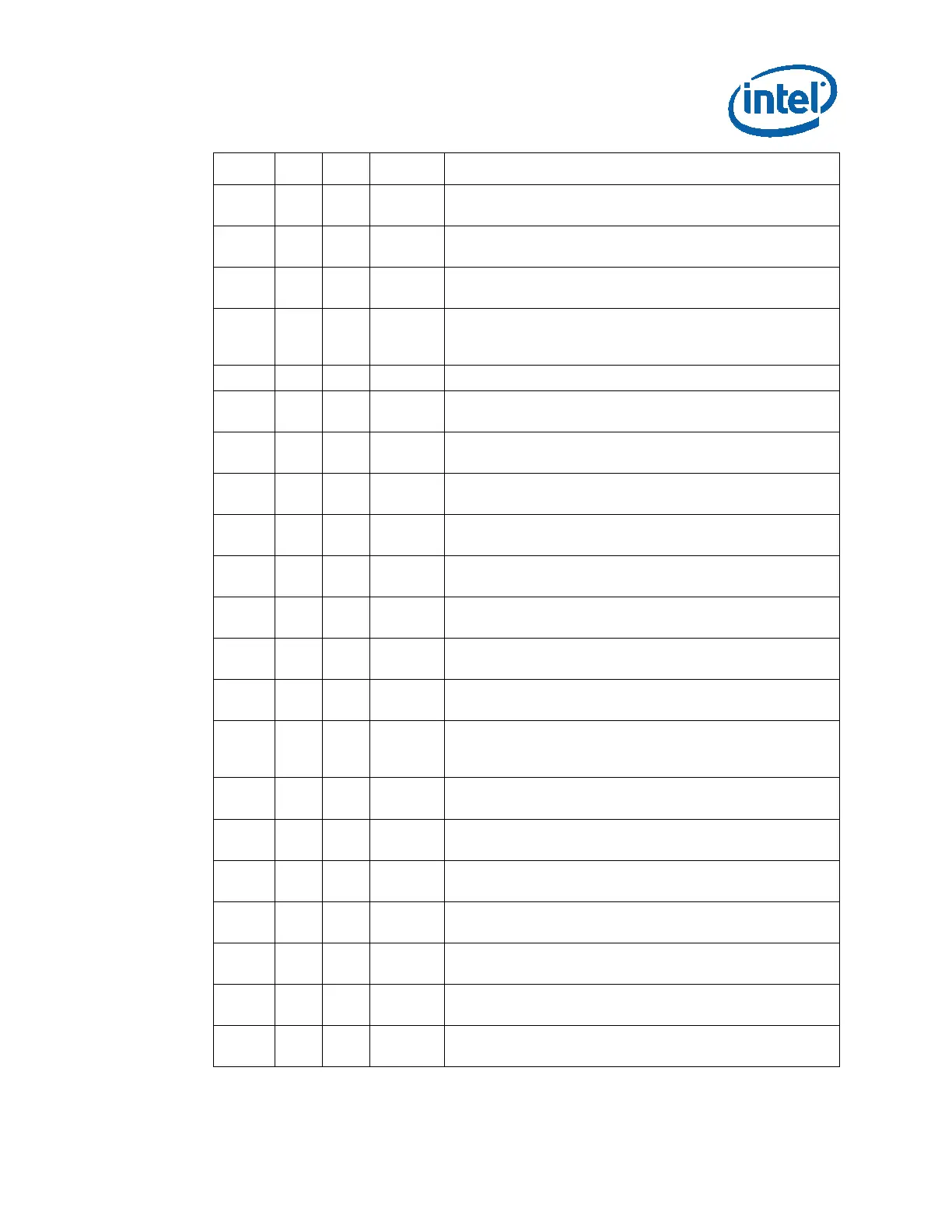

NO B3 G0 Plan ERRATA

AK88 X X No Fix

Microcode Updates Performed During VMX Non-root

Operation Could Result in Unexpected Behavior

AK89 X X No Fix

INVLPG Operation for Large (2M/4M) Pages May be

Incomplete under Certain Conditions

AK90 X X No Fix

Page Access Bit May be Set Prior to Signaling a Code

Segment Limit Fault

AK91 X Fixed

Update of Attribute Bits on Page Directories without

Immediate TLB Shootdown May Cause Unexpected

Processor Behavior

AK92 X Fixed Invalid Instructions May Lead to Unexpected Behavior

AK93 X X No Fix

EFLAGS, CR0, CR4 and the EXF4 Signal May be Incorrect

after Shutdown

AK94 X Fixed

Performance Monitoring Counter MACRO_INSTS.DECODED

May Not Count Some Decoded Instructions

AK95 X Fixed

The Stack Size May be Incorrect as a Result of VIP/VIF

Check on SYSEXIT and SYSRET

AK96 X X No Fix

Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL

is Counted Incorrectly for PMULUDQ Instruction

AK97 X X No Fix

Storage of PEBS Record Delayed Following Execution of

MOV SS or STI

AK98 X Fixed

Processor On Die Termination of BR1# and LOCK# Signals

are Incorrect

AK99 X X No Fix

Store Ordering May be Incorrect between WC and WP

Memory Types

AK100 X X No Fix

Updating Code Page Directory Attributes without TLB

Invalidation May Result in Improper Handling of Code #PF

AK101 X Fixed

Performance Monitoring Event CPU_CLK_UNHALTED.REF

May Not Count Clock Cycles According to the Processors

Operating Frequency

AK102 X Fixed

Performance Monitoring Event BR_INST_RETIRED May

Count CPUID Instructions as Branches

AK103 X X No Fix

Performance Monitoring Event MISALIGN_MEM_REF May

Over Count

AK104 X X No Fix

A REP STOS/MOVS to a MONITOR/MWAIT Address Range

May Prevent Triggering of the Monitoring Hardware

AK105 X Fixed

False Level One Data Cache Parity Machine-Check

Exceptions May be Signaled

AK106 X X No Fix

A Memory Access May Get a Wrong Memory Type Following

a #GP due to WRMSR to an MTRR Mask

AK107 X X No Fix

PMI While LBR Freeze Enabled May Result in Old/Out-of-

date LBR Information

AK108 X Fixed

Overlap of an Intel

®

VT APIC Access Page in a Guest with

the DS Save Area May Lead to Unpredictable Behavior

Loading...

Loading...