1-8 (No.YA263)

2.4 TECHNINAL INFORMATION

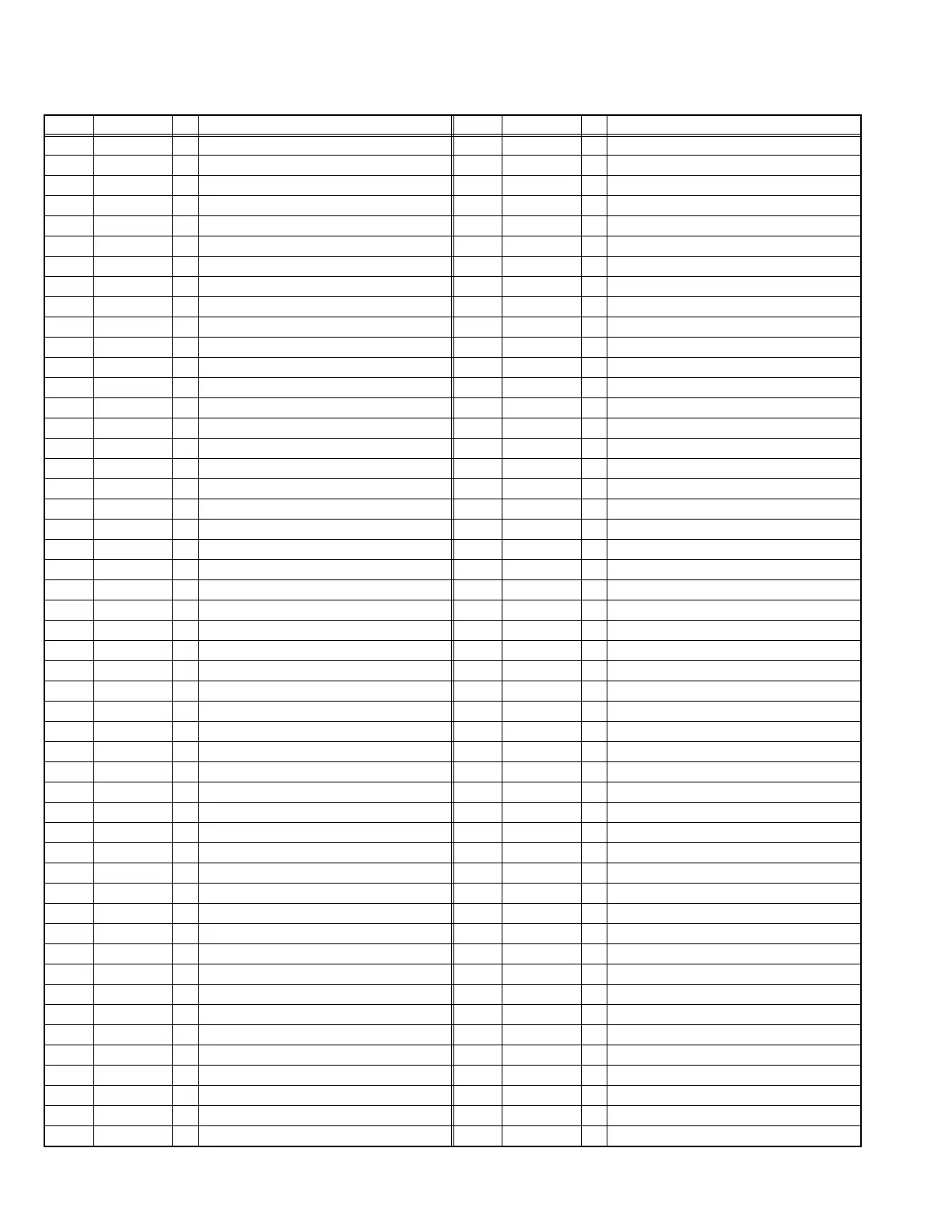

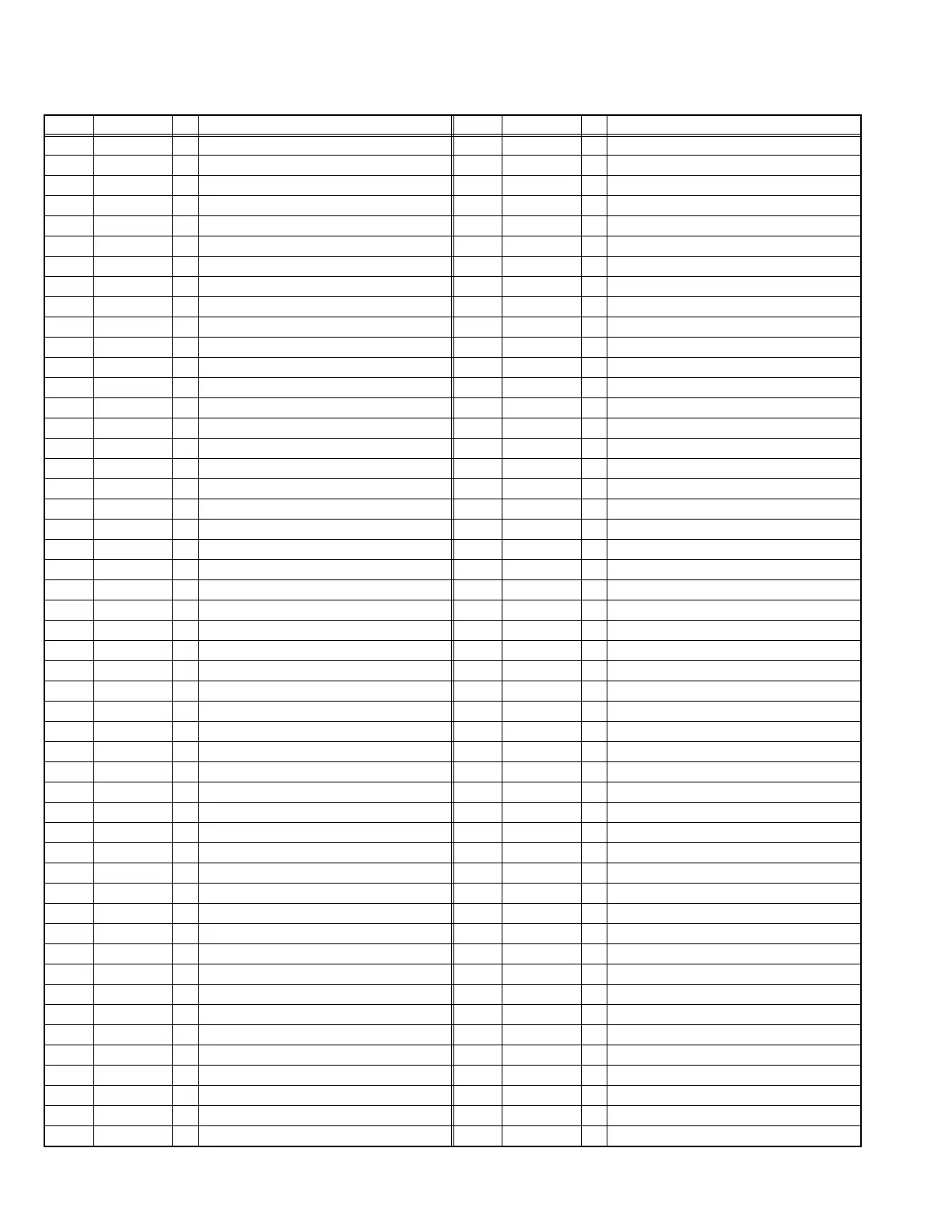

2.4.1 MAIN MI-COM (CPU) PIN FUNCTION

Pin No. Pin name I/O Function Pin No. Pin name I/O Function

1 D1 I/O Data bit for SRAM 51 NC -- Not used

2 D4 I/O Data bit for SRAM 52 XTAL2 I System clock (6MHz)

3 D2 I/O Data bit for SRAM 53 XTAL1 O System clock (6MHz)

4 D3 I/O Data bit for SRAM 54 NC -- Not used

5 XROM I External ROM access (Enable: L) 55 VSSA -- GND

6 VDD25 I 2.5V 56 VDDA25 I 2.5V

7 VSS25 -- GND 57 R O Red for OSD / Teletext

8 VDD33 I 3.3V 58 G O Green for OSD / Teletext

9 P0.0 O I2C bus clock for E2PROM 59 B O Blue for OSD / Teletext

10 P0.1 I/O I2C bus data for E2PROM 60 BLANK/COR O Output for blanking and contrast reduction

11 P0.2 O I2C bus clock for generally 61 NC -- Not used

12 P0.3 I/O I2C bus data for generally 62 P1.7 O Not used

13 P0.4 O Not used 63 NC -- Not used

14 P0.5 O Not used 64 WR O External memory write strobe for SRAM

15 P0.6 O Audio muting (Muting: H) 65 RD O External memory read strobe for SRAM

16 P0.7 O Power on/off control (ON: L) 66 NC -- Not used

17 ENE I Not used 67 A19 O Address bit for SRAM

18 STOP I Not used 68 A18 O Address bit for SRAM

19 OCF I Not used 69 A17 O Address bit for SRAM

20 EXTIF I Extended memory interface (Enable: L) 70 A16 O Address bit for SRAM

21 CVBS I Composite video signal input 71 A15 O Address bit for SRAM

22 VDDA25 I 2.5V 72 FL_RGM I Not used

23 VSSA -- GND 73 VDD25 I 2.5V

24 P2.0 I AFC voltage from tuner 74 VSS -- GND

25 P2.1 I Key scan from front control CH+ CH- MENU 75 VDD33 I 3.3V

26 P2.2 I AGC voltage from tuner 76 A14 O Address bit for SRAM

27 P2.3 O Not used 77 A12 O Address bit for SRAM

28 NC -- Not used 78 A13 O Address bit for SRAM

29 HS/SSC I Horizontal sync 79 A7 O Address bit for SRAM

30 VS I Vertical sync 80 FL_RST I Not used

31 P3.0 O Not used 81 A8 O Address bit for SRAM

32 P3.1 O Not used 82 A6 O Address bit for SRAM

33 P3.2 I Remote control 83 A9 O Address bit for SRAM

34 P3.3 I Receive data from TV_LINK 84 A5 O Address bit for SRAM

35 P3.4 O DDP reset (Reset: H) 85 A11 O Address bit for SRAM

36 P3.5 I

X-ray HB LB EW correction Protection detection (Normal: H)

86 A4 O Address bit for SRAM

37 P3.6 I/O Not used 87 ALE O Enable for address latch

38 P3.7 I Not used 88 PSEN O Enable for program store

39 VSS -- GND 89 A3 O Address bit for SRAM

40 VDD33 I 3.3V 90 A10 O Address bit for SRAM

41 P1.0 O Not used 91 VSS -- GND

42 P1.1 O Not used 92 VDD33 I 3.3V

43 P1.2 O Not used 93 A2 O Address bit for SRAM

44 P1.3 O Output data for TV_LINK 94 A1 O Address bit for SRAM

45 P1.4 O MSP reset (Reset: H) 95 FL_CE I Not used

46 P1.5 O Not used 96 D7 I/O Data bit for SRAM

47 P1.6 O Power indication control (ON: L) 97 A0 O Address bit for SRAM

48 P4.2 O Not used 98 D6 I/O Data bit for SRAM

49 P4.3 O Not used 99 D0 I/O Data bit for SRAM

50 RST I Reset for main CPU 100 D5 I/O Data bit for SRAM

Loading...

Loading...