Kirisun Communications Co.,Ltd

of

Page:

REV:

File NO.:

Filename:

Model:

Check:

Approve:

DATE:

Designer:

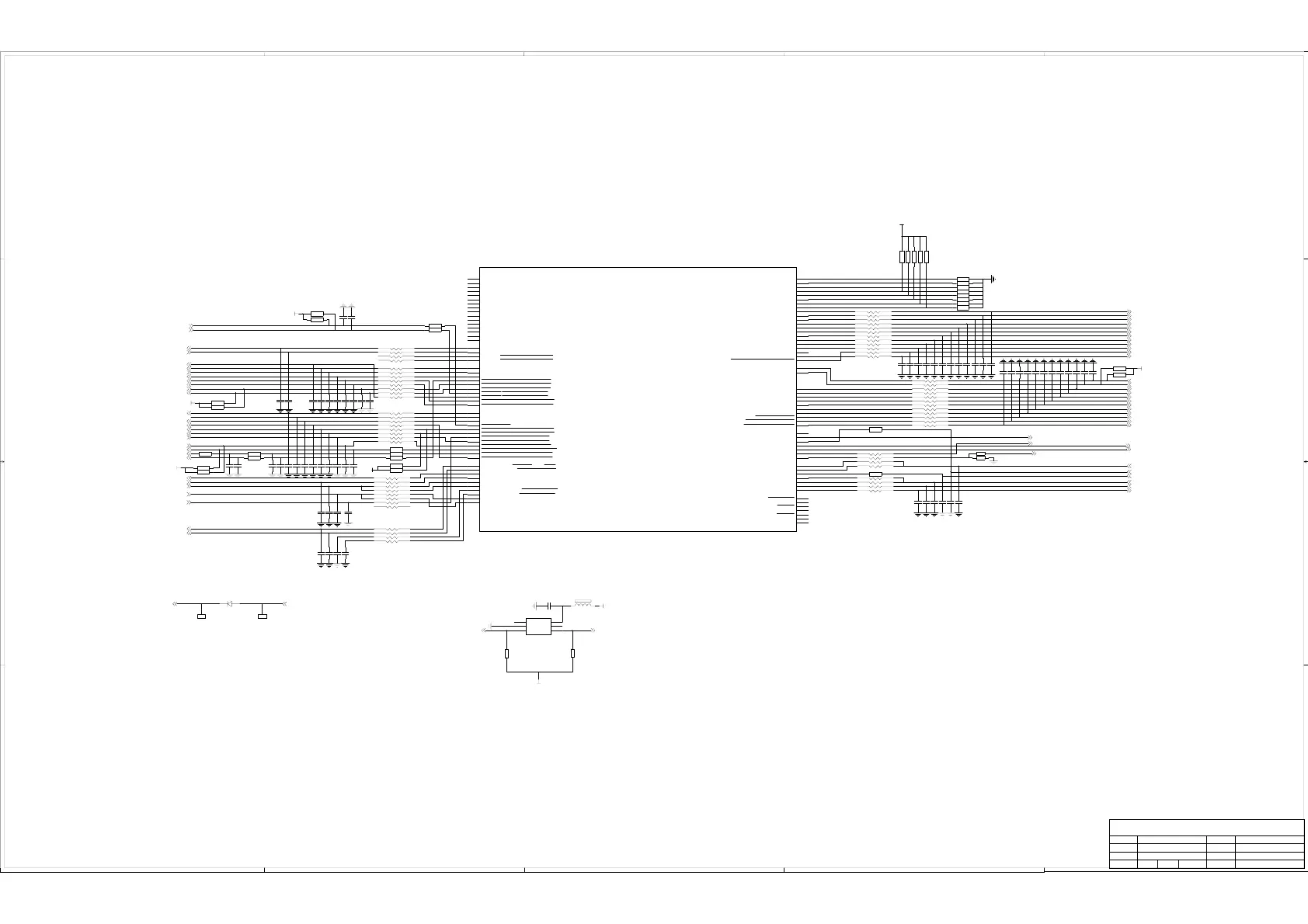

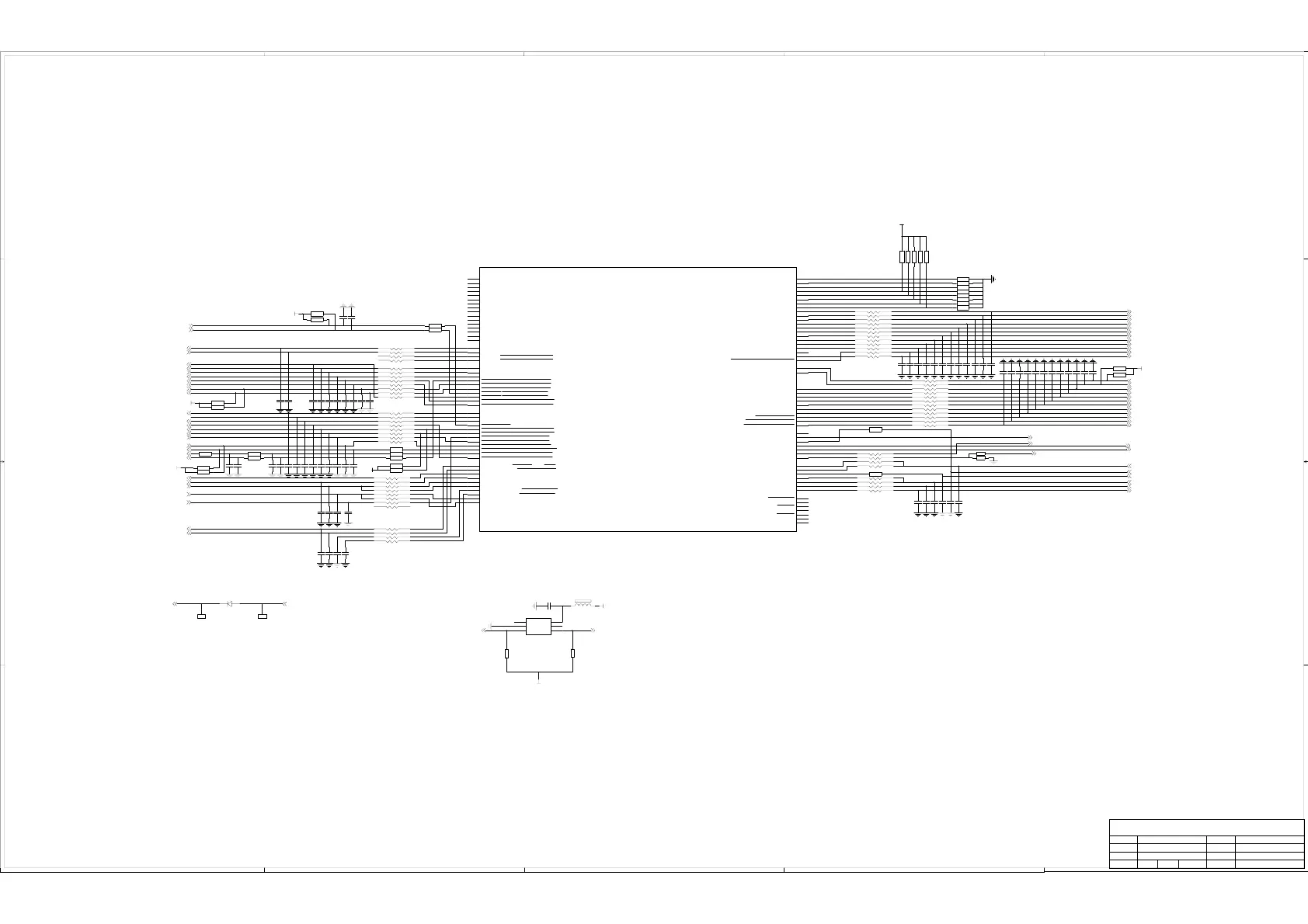

0XX01110 NANDFLASH 8BIT

00011110 DEBUG MODEL

A

B

C

D

5 4 3 2 1

D

C

B

A

12345

TP634

TXD

R273 1K

R200 NC

R268 100R

R26047K

C105133pF

C111433pF

R199 0R

RN1 100R*4

R25947K

C103533pF

C103333pF

C105633pF

C103133pF

RN16100R*4

C108433pF

C103833pF

R288 47K

C105433pF

C107233pF

C104833pF

C104633pF

C108233pF

R197 0R

R286 100R

R271 100R

RN27 100R*4

RN29 100R*4

C1111100pF

C108033pF

R280 47K

C104333pF

C107833pF

C110933pF

R269 10K

12

D506 MA2S111

RN18100R*4

C109133pF

C108933pF

R262NC

C104133pF

C107633pF

C105333pF

RN2 100R*4

R296 100R

C1113100pF

TP635

RXD

C108733pF

R29847K

C103633pF

C113833pF

RN8 100R*4

C114533pF

1

RSTO

2

GND

3

GP1

4

GP0

5

VPP

6

VDD

U910 QINGHUA

R274 100R

C1063 102

C102833pF

R283 47K

C105233pF

R267 1K

RN17100R*4

C103433pF

C107533pF

C105033pF

V18

VP_DIN[15]_VSYNC/UHPI_HD[7]/UPP_D[7]/PRU

V19

VP_DIN[14]_HSYNC/UHPI_HD[6]/UPP_D[6]/PRU

U19

VP_DIN[13]_FIELD/UHPI_HD[5]/UPP_D[5]/PRU

T16

VP_DIN[12]/UHPI_HD[4]/UPP_D[4]/PRU0_R30[

R18

VP_DIN[11]/UHPI_HD[3]/UPP_D[3]/PRU0_R30[

R19

VP_DIN[10]/UHPI_HD[2]/UPP_D[2]/PRU0_R30[

R15

VP_DIN[9]/UHPI_HD[1]/UPP_D[1]/PRU0_R30[9

P17

VP_DIN[8]/UHPI_HD[0]/UPP_D[0]/GP6[5]/PRU

U18

VP_DIN[7]/UHPI_HD[15]/UPP_D[15]/RMII_TXD

V16

VP_DIN[6]/UHPI_HD[14]/UPP_D[14]/RMII_TXD

R14

VP_DIN[5]/UHPI_HD[13]/UPP_D[13]/RMII_TXE

W16

VP_DIN[4]/UHPI_HD[12]/UPP_D[12]/RMII_RXD

V17

VP_DIN[3]/UHPI_HD[11]/UPP_D[11]/RMII_RXD

W17

VP_DIN[2]/UHPI_HD[10]/UPP_D[10]/RMII_RXE

W18

VP_DIN[1]/UHPI_HD[9]/UPP_D[9]/RMII_MHZ_5

W19

VP_DIN[0]/UHPI_HD[8]/UPP_D[8]/RMII_CRS_D

J3

VP_CLKIN3/MMCSD1_DAT[1]/PRU1_R30[1]/GP6[

H3

VP_CLKIN2/MMCSD1_DAT[3]/PRU1_R30[3]/GP6[

V15

VP_CLKIN1/UHPI_HDS1/PRU1_R30[9]/GP6[6]/

W14

VP_CLKIN0/UHPI_HCS/PRU1_R30[10]/GP6[7]/

D19

SPI0_CLK/EPWM0A/GP1[8]/MII_RXCLK

C16

SPI0_SOMI/EPWMSYNCI/GP8[6]/MII_RXER

C18

SPI0_SIMO/EPWMSYNCO/GP8[5]/MII_CRS

C17

SPI0_ENA/EPWM0B/PRU0_R30[6]/MII_RXDV

C19

SPI0_SCS[5]/UART0_RXD/GP8[4]/MII_RXD[3]

D18

SPI0_SCS[4]/UART0_TXD/GP8[3]/MII_RXD[2]

E17

SPI0_SCS[3]/UART0_CTS/GP8[2]/MII_RXD[

D16

SPI0_SCS[2]/UART0_RTS/GP8[1]/MII_RXD[

E16

SPI0_SCS[1]/TM64P0_OUT12/GP1[7]/MDIO_CL

D17

SPI0_SCS[0]/TM64P1_OUT12/GP1[6]/MDIO_D/

G19

SPI1_CLK/GP2[13]

H17

SPI1_SOMI/GP2[11]

G17

SPI1_SIMO/GP2[10]

H16

SPI1_ENA/GP2[12]

G16

SPI1_SCS[7]/I2C0_SCL/TM64P2_OUT12/GP1[5

G18

SPI1_SCS[6]/I2C0_SDA/TM64P3_OUT12/GP1[4

F17

SPI1_SCS[5]/UART2_RXD/I2C1_SCL/GP1[3]

F16

SPI1_SCS[4]/UART2_TXD/I2C1_SDA/GP1[2]

E18

SPI1_SCS[3]/UART1_RXD/SATA_LED/GP1[1]

F19

SPI1_SCS[2]/UART1_TXD/SATA_CP_POD/GP1[0

F18

SPI1_SCS[1]/EPWM1A/PRU0_R30[7]/GP2[15]/

E19

SPI1_SCS[0]/EPWM1B/PRU0_R30[8]/GP2[14]/

F4

RSVD/RTC_ALARM/UART2_CTS/GP0[8]/DEEPS

D5

AMUTE/PRU0_R30[16]/UART2_RTS/GP0[9]/PRU

D2

AXR7/EPWM1TZ[0]/PRU0_R30[17]/GP1[15]/PRU

A4

AXR15/EPWM0TZ[0]/ECAP2_APWM2/GP0[7]

B2

AFSX/GP0[12]/PRU0_R31[19]

C2

AFSR/GP0[13]/PRU0_R31[20]

A3

AHCLKX/USB_REFCLKIN/UART1_CTS/GP0[10]/P

A2

AHCLKR/PRU0_R30[18]/UART1_RTS/GP0[11]/P

B1

ACLKX/PRU0_R30[19]/GP0[14]/PRU0_R31[21]

A1

ACLKR/PRU0_R30[20]/GP0[15]/PRU0_R31[22]

P4

VP_DOUT[15]/LCD_D[15]/UPP_XD[7]/GP7[7]/B

R3

VP_DOUT[14]/LCD_D[14]/UPP_XD[6]/GP7[6]/B

R2

VP_DOUT[13]/LCD_D[13]/UPP_XD[5]/GP7[5]/B

R1

VP_DOUT[12]/LCD_D[12]/UPP_XD[4]/GP7[4]/B

T3

VP_DOUT[11]/LCD_D[11]/UPP_XD[3]/GP7[3]/B

T2

VP_DOUT[10]/LCD_D[10]/UPP_XD[2]/GP7[2]/B

T1

VP_DOUT[9]/LCD_D[9]/UPP_XD[1]/GP7[1]/BOO

U3

VP_DOUT[8]/LCD_D[8]/UPP_XD[0]/GP7[0]/BOO

U2

VP_DOUT[7]/LCD_D[7]/UPP_XD[15]/GP7[15]/P

U1

VP_DOUT[6]/LCD_D[6]/UPP_XD[14]/GP7[14]/P

V3

VP_DOUT[5]/LCD_D[5]/UPP_XD[13]/GP7[13]/P

V2

VP_DOUT[4]/LCD_D[4]/UPP_XD[12]/GP7[12]/P

V1

VP_DOUT[3]/LCD_D[3]/UPP_XD[11]/GP7[11]/P

W3

VP_DOUT[2]/LCD_D[2]/UPP_XD[10]/GP7[10]/P

W2

VP_DOUT[1]/LCD_D[1]/UPP_XD[9]/GP7[9]/PRU

W1

VP_DOUT[0]/LCD_D[0]/UPP_XD[8]/GP7[8]/PRU

H4

MMCSD1_DAT[5]/LCD_HSYNC/PRU1_R30[5]/GP8[

G4

MMCSD1_DAT[4]/LCD_VSYNC/PRU1_R30[4]/GP8[

F2

MMCSD1_DAT[6]/LCD_MCLK/PRU1_R30[6]/GP8[1

K3

VP_CLKOUT2/MMCSD1_DAT[2]/PRU1_R30[2]/GP6

K4

VP_CLKOUT3/PRU1_R30[0]/GP6[1]/PRU1_R31[1

R5

LCD_AC_ENB_CS/GP6[0]/PRU1_R31[28]

G1

PRU0_R30[25]/MMCSD1_DAT[0]/UPP_CHB_CLOCK

G2

PRU0_R30[24]/MMCSD1_CLK/UPP_CHB_START/GP

J4

PRU0_R30[23]/MMCSD1_CMD/UPP_CHB_ENABLE/G

G3

PRU0_R30[22]/PRU1_R30[8]/UPP_CHB_WAIT/GP

U17

PRU0_R30[29]/UHPI_HCNTL0/UPP_CHA_CLOCK/G

W15

PRU0_R30[28]/UHPI_HCNTL1/UPP_CHA_START/G

U16

PRU0_R30[27]/UHPI_HHWIL/UPP_CHA_ENABLE/G

T15

PRU0_R30[26]/UHPI_HRW/UPP_CHA_WAIT/GP6[

R16

PRU0_R30[30]/UHPI_HINT/PRU1_R30[11]/GP6

R17

PRU0_R30[31]/UHPI_HRDY/PRU1_R30[12]/GP6

C1

AXR6/CLKR0/GP1[14]/MII_TXEN/PRU0_R31[6]

D3

AXR5/CLKX0/GP1[13]/MII_TXCLK

F3

AXR0/ECAP0_APWM0/GP8[7]/MII_TXD[0]/CLKS0

D1

AXR4/FSR0/GP1[12]/MII_COL

E3

AXR3/FSX0/GP1[11]/MII_TXD[3]

E2

AXR2/DR0/GP1[10]/MII_TXD[2]

E1

AXR1/DX0/GP1[9]/MII_TXD[1]

B4

AXR14/CLKR1/GP0[6]

B3

AXR13/CLKX1/GP0[5]

E4

AXR8/CLKS1/ECAP1_APWM1/GP0[0]/PRU0_R31[8

C4

AXR12/FSR1/GP0[4]

C5

AXR11/FSX1/GP0[3]

D4

AXR10/DR1/GP0[2]

C3

AXR9/DX1/GP0[1]

N1

SATA_REFCLKN

N2

SATA_REFCLKP

J2

SATA_TXN

J1

SATA_TXP

L2

SATA_RXN

L1

SATA_RXP

M3

NC_M3

F1

MMCSD1_DAT[7]/LCD_PCLK/PRU1_R30[7]/GP8[1

U906-C

OMAP-L138ZWT

SYM 2 OF 3

C103933pF

R25847K

C103233pF

C105533pF

C102733pF

C103033pF

C107333pF

C104933pF

C108333pF

R198 0R

C103733pF

C111633pF

C11120.1uF

R287 47K

R272 100R

C104733pF

C104533pF

C108133pF

C104433pF

C11100.1uF

C107933pF

RN6 100R*4

C111533pF

R270 10K

RN4 100R*4

C102933pF

R277 100R

RN3 100R*4

R257 0R

RN5 100R*4

RN28 100R*4

R279 47K

C104233pF

C107733pF

C109233pF

R256 NC

C109033pF

R255 NC

C108833pF

C104033pF

R285 47K

RN15 100R*4

R254 NC

C108633pF

R29747K

RN14 100R*4

R26147K

C108533pF

C113733pF

RN9 100R*4

R284 47K

FB922

BLM21PG221SN1D

C114433pF

R9 10K

R10

10K

R24

4.7k

R25

4.7k

C106233pF

CPU_3V3

CPU_3V3

CPU_3V3

CPU_3V3

CPU_3V3

CPU_3V3

CPU_3V3

AD9864_SKY72310_CLK

SKY72310_CS

AD9864_CS

TLV5614_CLK

TLV5614_DATE

AD9864_SKY72310_DATE

TLV5614_FS

AD9864_DOUTB

AIC_DIN

AIC_FS

AIC_SCLK

I2C0_SCL

I2C0_SDA

LCD_D0

LCD_D1

LCD_D2

LCD_D3

LCD_D4

LCD_D5

LCD_D6

LCD_D7

LCD_CS

LCD_WR

LCD_RS

LCD_RD

AD9864_CLKOUT

AD9864_FS

AD9864_DOUTA

POWER_CTL

POWER_KEY_DET

AUCON1_PA

AUCON2_PA

CH_AC

CH_BC

STANDBY

IDLE

RUN

TX-RQST

TX_RDY

STDBY_ENABLE

AMBE/REST

IFSELECT0

PTT

EMERGENCY

ACCELEROMETER_X

ACCELEROMETER_Y

BL_DIM

OUTPUTPA+

I2C1_SDA

UART_TXD

UART_RXD

UART_TXDUART_RXD

GPS_TXD

GPS_RXD

AIC_DOUT

SPILCD_CS

I2C1_SCL

KB_C1

KB_C0

TCA8418_RESET

I2C1_SCL I2C1_SDA

USB_VBUS

TX_CONTROL

AIC_PWRDN

KEYBORAD_INT

ALERTN

CPU_3V3

Loading...

Loading...