- 14 -

Copyright © LG Electronics Inc. All rights reserved.

Only training and service purposes.

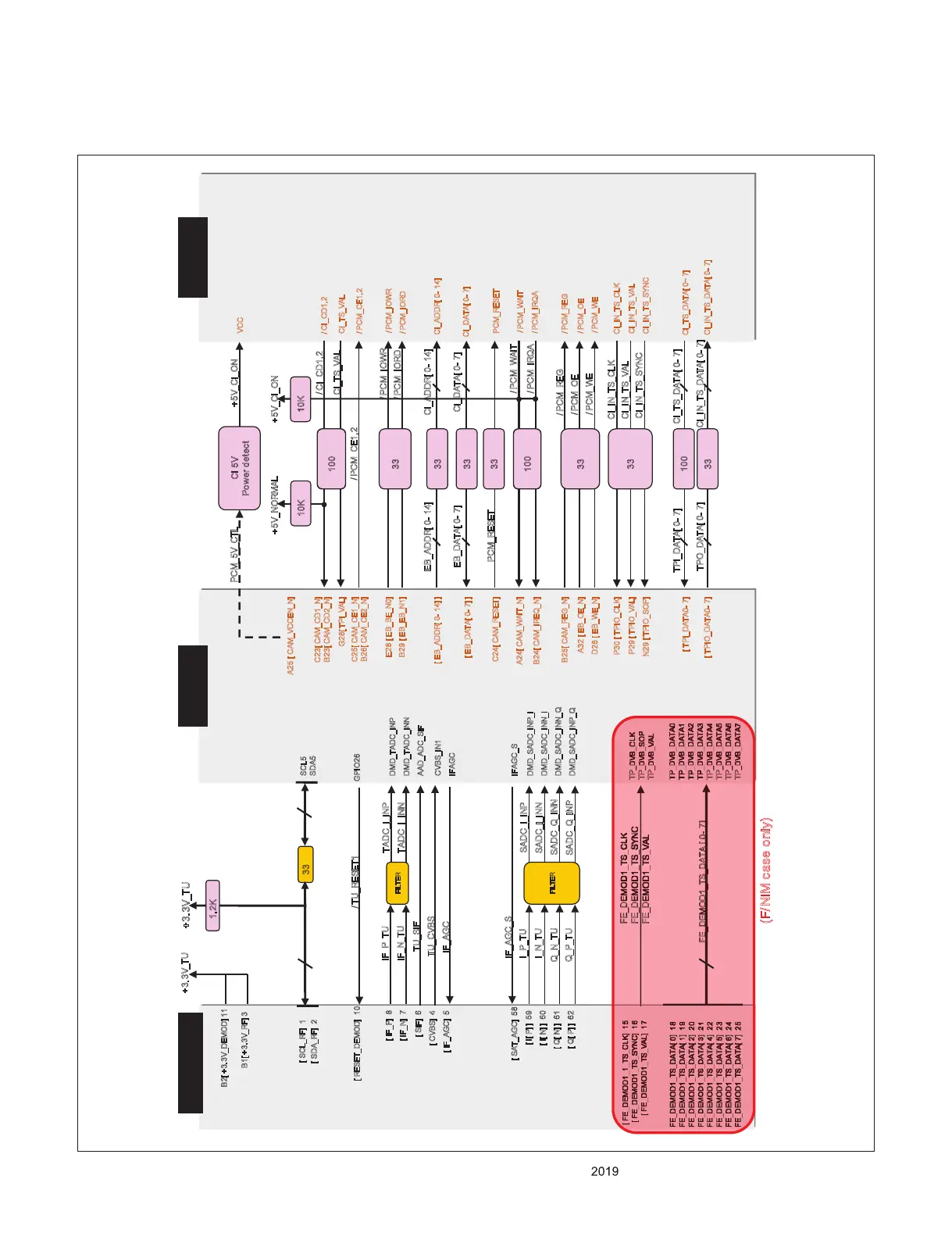

SCL5

S

DA5

D

MD_TADC_INP

DMD_TADC_INN

A

AD_ADC_SIF

TUNER

B2[ +3.3V_DEMOD] 11

[

IF_P] 8

[ IF_N] 7

+3.3V_TU

[ SCL_RF] 1

[

SDA_RF] 2

[

SIF] 6

[

CVBS] 4

[

IF_AGC] 5

[

RESET_DEMOD] 10

FILTER

33 Ω

IF_P_TU

I

F_N_TU

T

U_CVBS

I

F_AGC

T

ADC_I_INP

T

ADC_I_INN

/ TU_RESET1

GPIO26

C

VBS_IN1

I

FAGC

+3.3V_TU

1.2KΩ

Main IC

B1[ +3.3V_RF] 3

TU_SIF

FE_D

FE_D

FE_D

FE_DEMOD1_TS_DATA [ 0- 7]

TP_

TP_

TP_

TP_

TP_

TP_

TP_

(F/ NIM case only)

[ I[ P] ] 59

[ I[ N] ] 60

[ Q[ N] ] 61

[

Q[ P] ] 62

DMD_SADC_INP_I

DMD_SADC_INN_I

DMD_SADC_INN_Q

D

MD_SADC_INP_Q

FILTER

I_P_TU

I

_N_TU

Q

_P_TU

I

F_AGC_S

S

ADC_I_INP

S

ADC_I_INN

IFAGC_S

Q_N_TU

S

ADC_Q_INN

S

ADC_Q_INP

[ SAT_AGC] 58

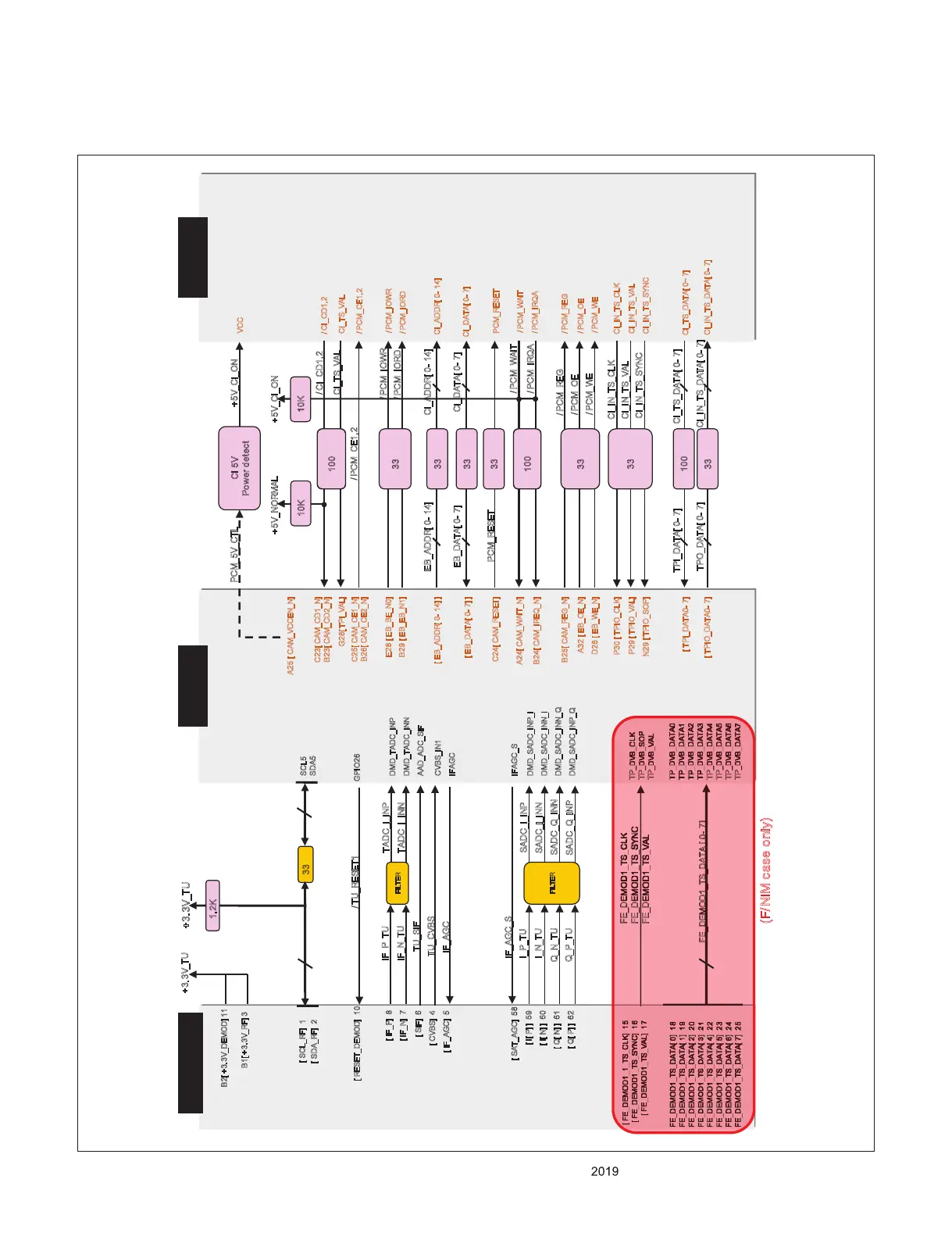

CI Slot

33 Ω

T

PO_DATA[ 0- 7] CI_IN_TS_DATA[ 0- 7]

100 Ω

T

PI_DATA[ 0- 7] CI_TS_DATA[ 0- 7]

/ PCM_WE

/

PCM_OE

/ PCM_IRQA

/ PCM_WAIT

PCM_RESET

EB_ADDR[ 0- 14]

/ PCM_IORD

/ PCM_IOWR

/ PCM_CE1,2

CI_TS_VAL

/ CI_CD1,2

CI 5V

P

ower detect

PCM_5V_CTL

+

5V_CI_ON

CI_IN_TS_SYNC

CI_IN_TS_VAL

CI_IN_TS_CLK

[ TPIO_DATA0- 7] CI_IN_TS_DATA[ 0- 7]

[

TPI_DATA0- 7] CI_TS_DATA[ 0~ 7]

/

CI_CD1,2

C

23[ CAM_CD1_N]

B23[ CAM_CD2_N]

C

I_TS_VAL G28[ TPI_VAL]

C

25[ CAM_CE1_N]

B

26[ CAM_CE2_N]

/

PCM_CE1,2

10K Ω

E28 [ EB_BE_N0]

B

29 [ EB_EB_N1]

/

PCM_IOWR

/

PCM_IORD

[

EB_ADDR[ 0- 14] ]

[

EB_DATA[ 0- 7] ]

C

I_ADDR[ 0- 14]

C

I_DATA[ 0- 7]

C

24[ CAM_RESET]

A

24[ CAM_WAIT_N]

B

24[ CAM_IREQ_N]

A

32 [ EB_OE_N]

D

28 [ EB_WE_N]

P

30 [ TPIO_CLK]

P

29 [ TPIO_VAL]

N

29 [ TPIO_SOP]

C

I_IN_TS_CLK

C

I_IN_TS_VAL

C

I_IN_TS_SYNC

P

CM_RESET

/

PCM_WAIT

/ PCM_IRQA

/

PCM_OE

/

PCM_WE

V

CC

A

25 [ CAM_VCCEN_N]

+5V_NORMAL +5V_CI_ON

10K Ω

33 Ω

C

I_ADDR[ 0- 14]

EB_DATA[ 0- 7]

33 Ω

C

I_DATA[ 0- 7]

33 Ω

33 Ω

/ PCM_REG

B25[ CAM_REG_N] / PCM_REG

33 Ω

100 Ω

33 `

100 Ω

4. TUNER

Loading...

Loading...