3 - 22 3 - 22

MELSEC-Q

3 SPECIFICATIONS

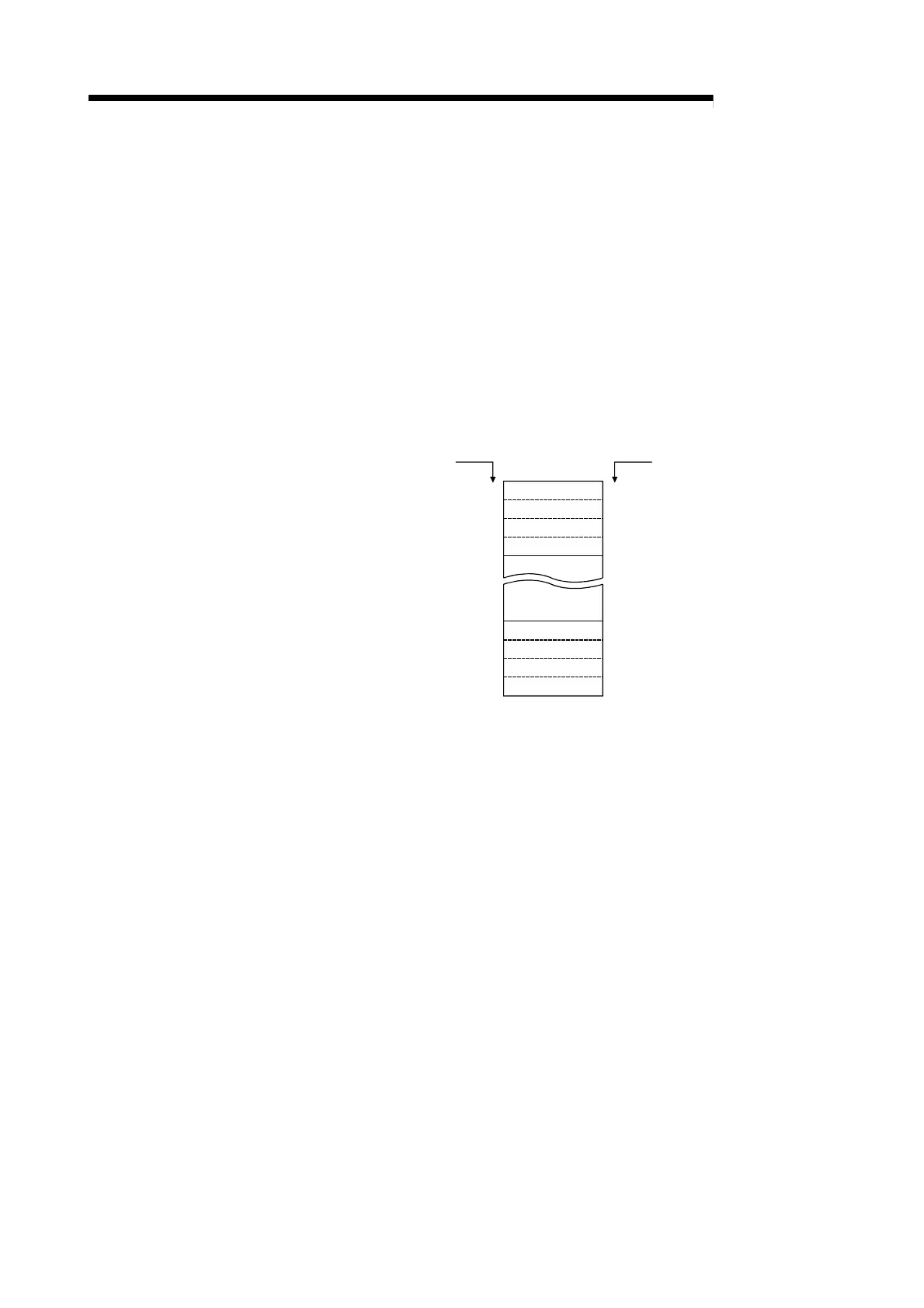

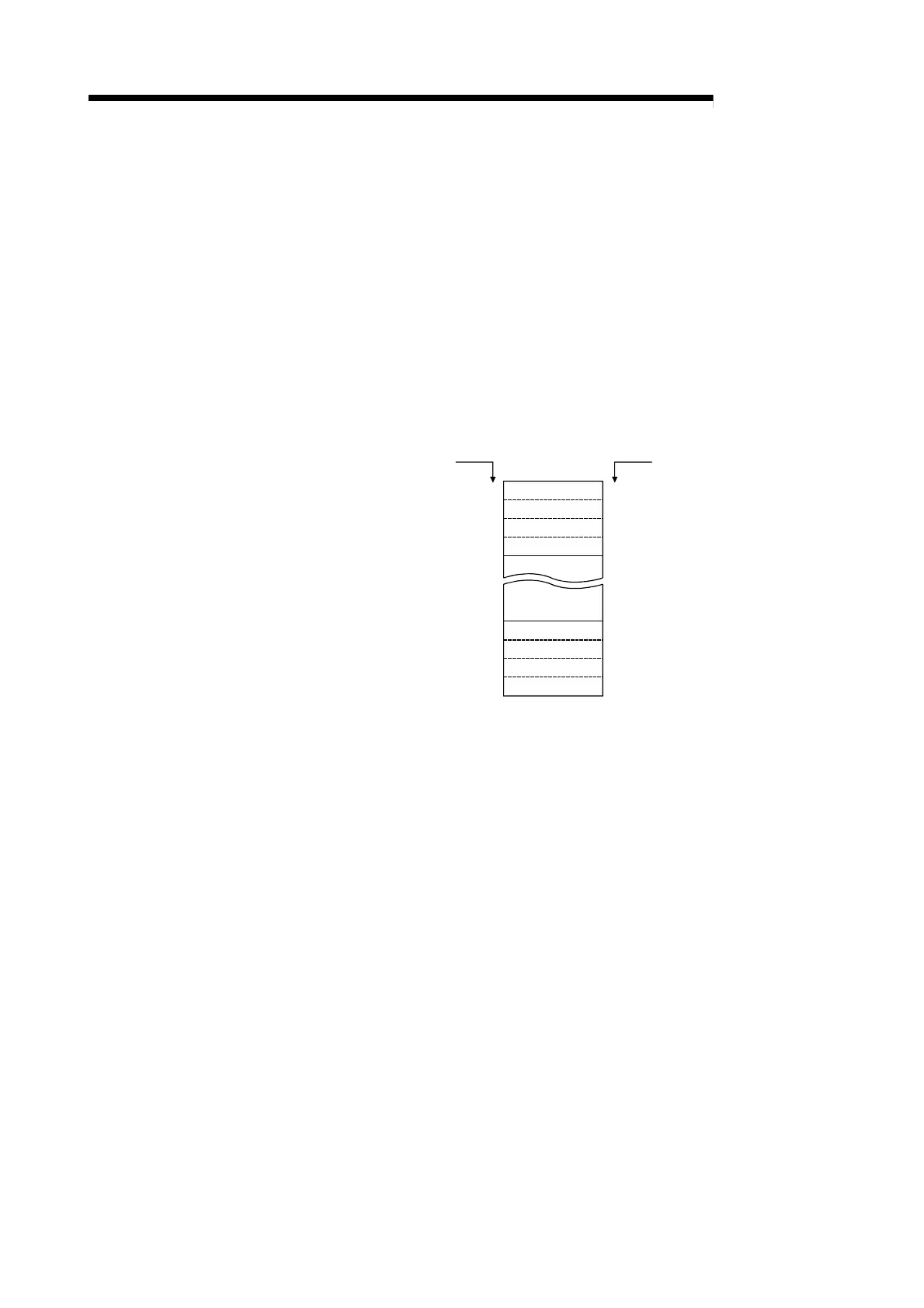

(4) Buffer Memory Addresses

Addresses in buffer memory differ depending on whether they are designated by

the programmable controller CPU or by a BASIC program, and are as follows.

(a) If designated from the programmable controller CPU

If designated by the programmable controller CPU, addresses are in 1-

word units.

Also, buffer memory addresses are designated from 0

H to BFFH in

hexadecimal notation.

(b) If designated by a BASIC program

If designated by a BASIC program, addresses are in 1-byte units.

Also, buffer memory addresses are designated from 0

H to 17FFH in

hexadecimal notation.

Designated from the

programmable

controller CPU using

a FROM/TO command.

(1-word units)

Address designated by

GETMEM / PUTMEM

in a BASIC program.

(1-byte units)

Buffer Memory

Lower order 8 bits

Higher order 8 bits

17FC

H

17FDH

17FE

H

17FFH

BFEH

BFFH

0

H

1H

2

H

3H

0

H

1H

Lower order 8 bits

Higher order 8 bits

Lower order 8 bits

Higher order 8 bits

Lower order 8 bits

Higher order 8 bits

Loading...

Loading...