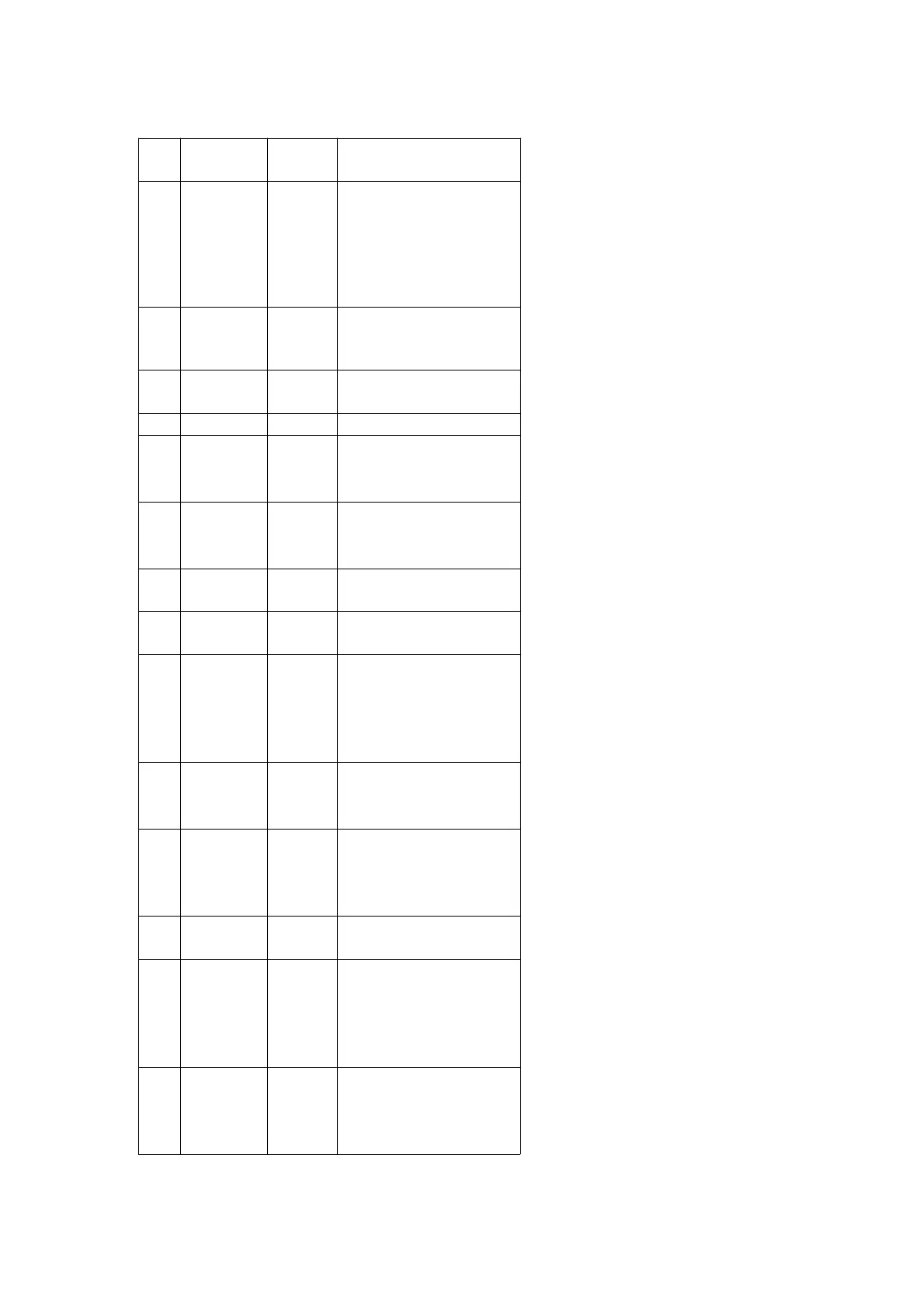

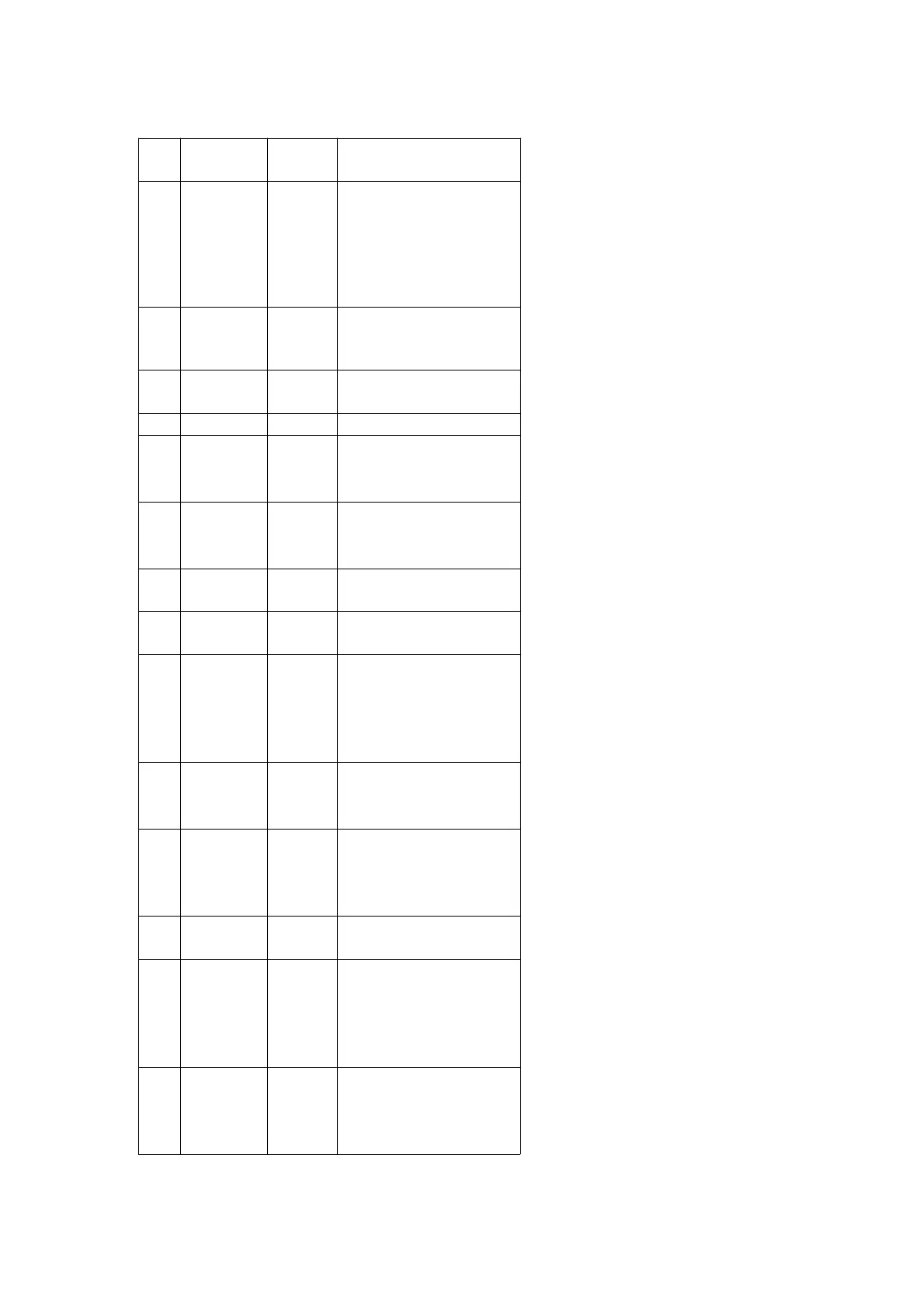

Pin

No.

Mark I/O Function

54 VCOF2 I/O VCO loop Filter for

33.8688 MHz

Conversion Terminal

for 16.9344 Mhz Crystal

mode, Must use other

Circuit)

55 SUBC O Sub-Code Serial Data

Output (Not Used,

Open)

56 SBCK I Clock Input for Sub-

Code Serial Data)

57 VSS I GND

58 X1 IN I

Crystal Oscillating

Circuit Input

(f= 16.9344 MHz)

59 X2 OUT O

Crystal Oscillating

Circuit Input

(f= 16.9344 MHz)

60 VDD I Power Supply Input

(For Oscillating Circuit)

61 BYTCK O Byte Clock Output (Not

Used, Open)

62 /CLDCK O

Sub-Code Frame Clock

Signal Output

(fCLDCK= 7.35 kHz

During Normal

Playback)

63 FCLK O

Crystal Frame Clock

Signal Output)

(fCLDCK= 7.35 kHz)

64 IPFLAG O

Interpolation Flag

Output

(“H”: Interpolation)

(Not Used, Open)

65 FLAG O Flag Output (Not Ised,

Open)

66 CLVS O

Spindle Servo Phase

Synchronizing Signal

Output

(“H”: CLV, “L”: Rough

Servo) (Not used, Open)

67 CRC O

Sub-Code CRC

Checked Output

(“H”: OK, “L” NG) (Not

Used, Open)

54

Loading...

Loading...