User Manual P09

HD101 Processor loading with BP3

This document is valid for Evision system with:

Processor rmware: FPGA: 2.63 / ARM 3.07 / LCD 1.15

Tile rmware: FPGA 9.60

Input resolutions for the processor:

1024 x 768

1280 x 720

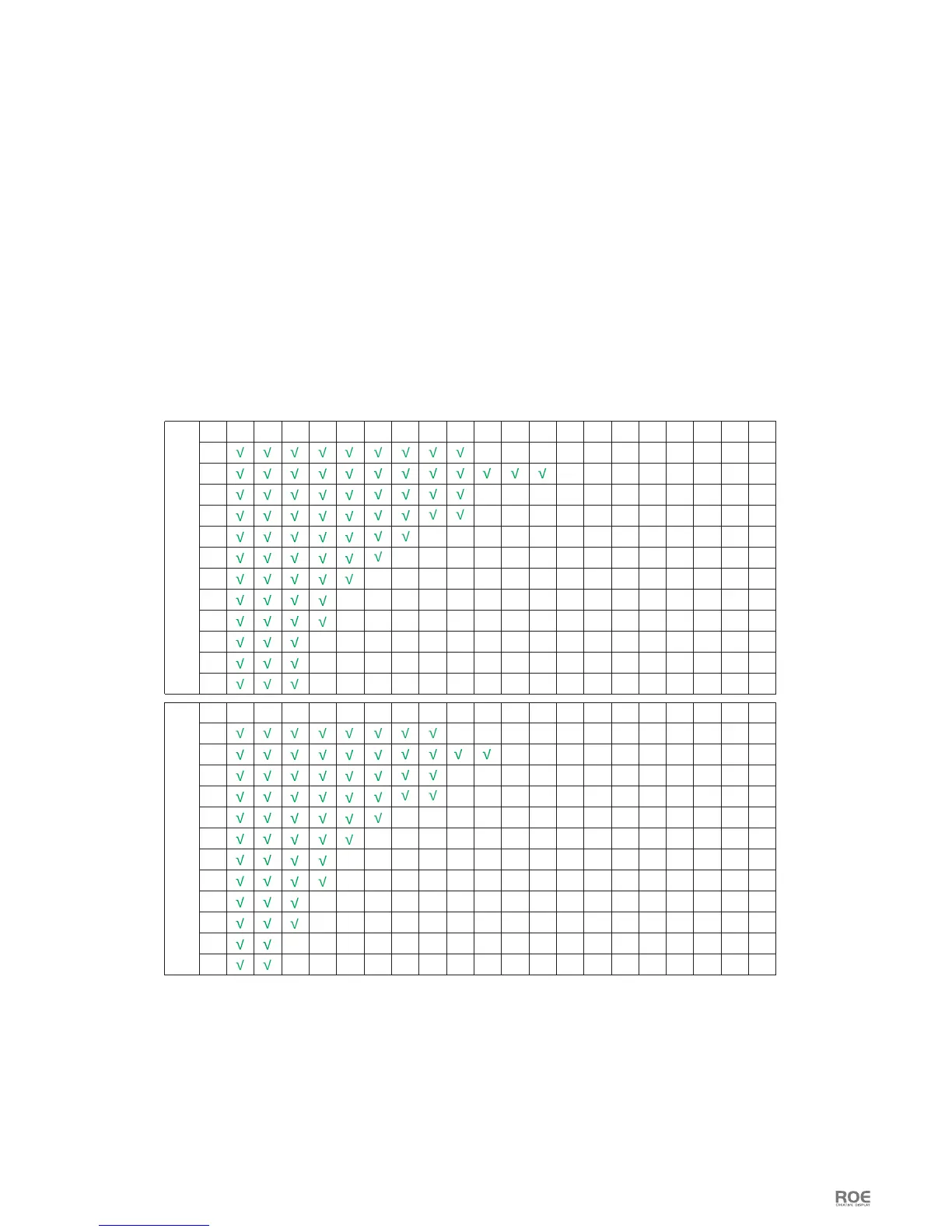

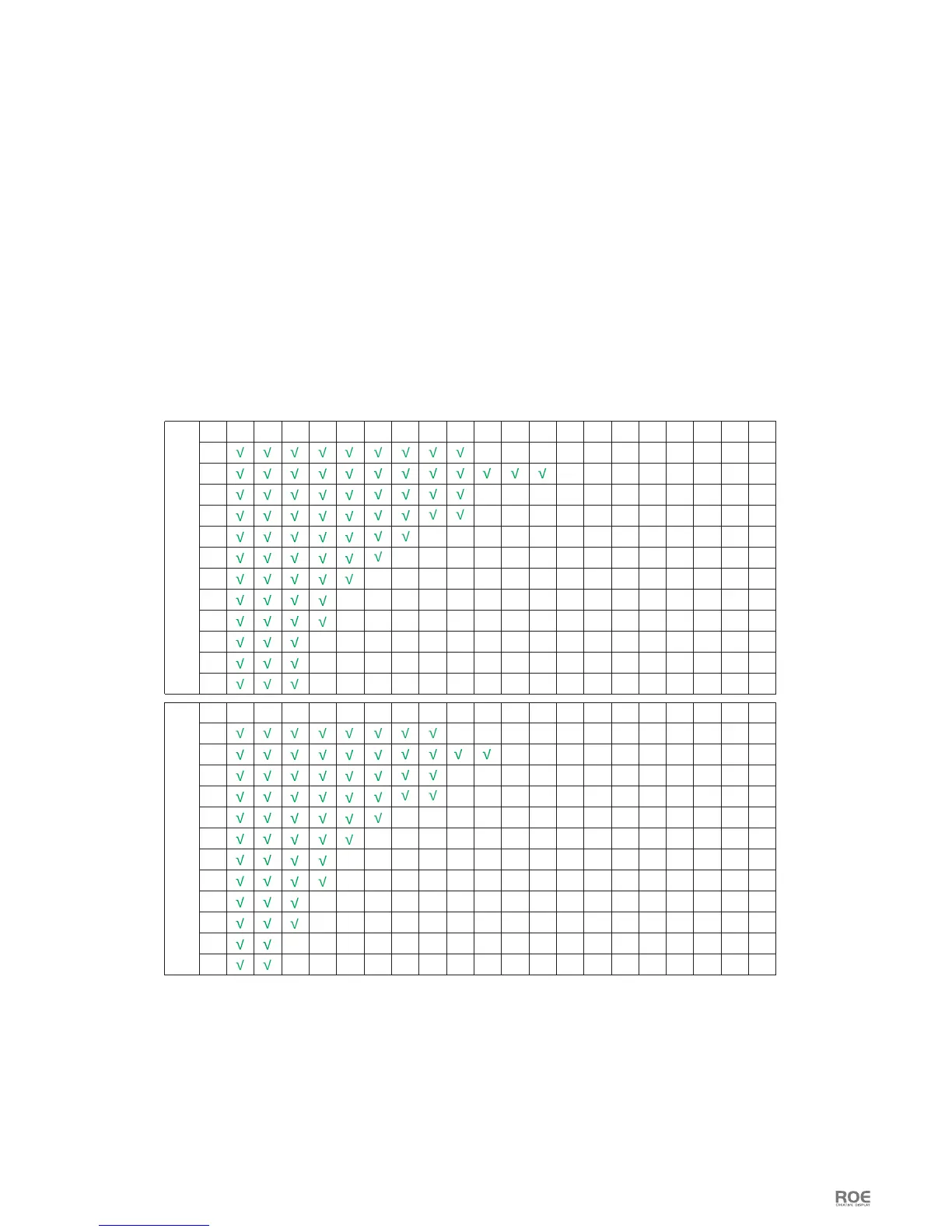

Every port supports a rectangular area, below tables show the possible number of tiles high and wide

(for 50 and 60Hz). If in a creative setup there are gaps or missing tiles, the supported rectangular area

stays the same as if there would be tiles.

1440 x 900

1680 x 1050

50Hz: 38 tiles 60Hz: 32 tiles

50Hz

Tile resolution:

Max tiles per processor output

Recommended mapping for standard frame delay (1 frames @ processor, 1 frame @ receiver card):

Recommended mapping for minimum frame delay (0 frames @ processor, 1 frame @ receiver card):

128 x 128 pixels (500mm x 500mm)

1

1

H\W

2

3

4

5

6

7

8

9

10

11

12

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×

×××

××××

×

×

√

√

√

√

××

√

√

√

√

√

√

√

√

√ √ √ √√

√

√

√

1366 x 768

1400 x 1536 (max height)

1920 x 1080

2560 x 820 (max width)

Example 1: 50Hz, 9 tiles wide, 4 tiles high → OK

Example 2: 50Hz, 9 tiles wide, 5 tiles high → not OK

Example 3: 60Hz, 9 tiles wide, 4 tiles high →not OK

Example 1: 50Hz, 9 tiles wide, 4 tiles high → not OK, too wide

Example 2: 50Hz, 4 tiles wide, 9 tiles high → OK

Example 3: 60Hz, 4 tiles wide, 9 tiles high → not OK

Max width per port is 512 pixels.

According tables for standard frame delay, but max 4 tiles wide.

Loading...

Loading...