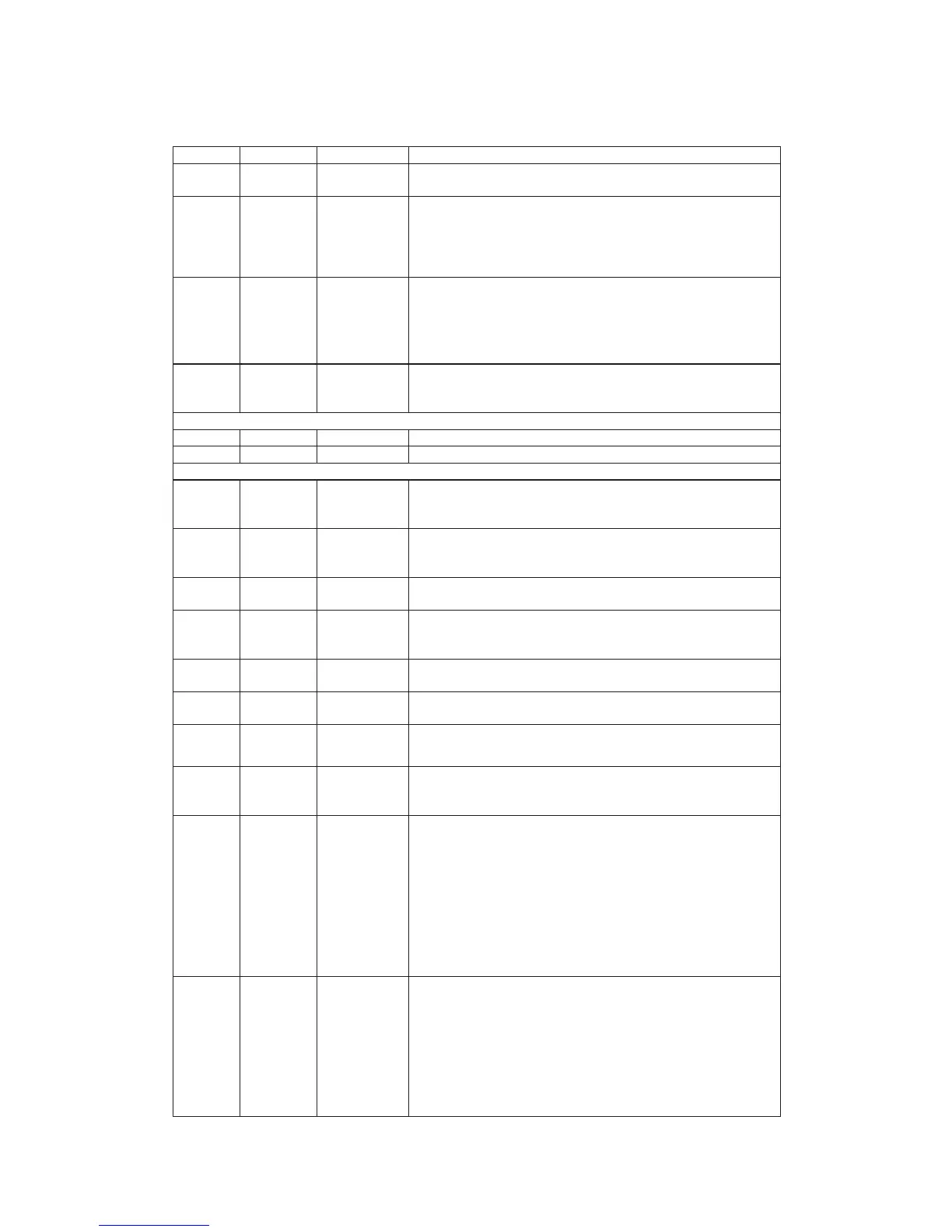

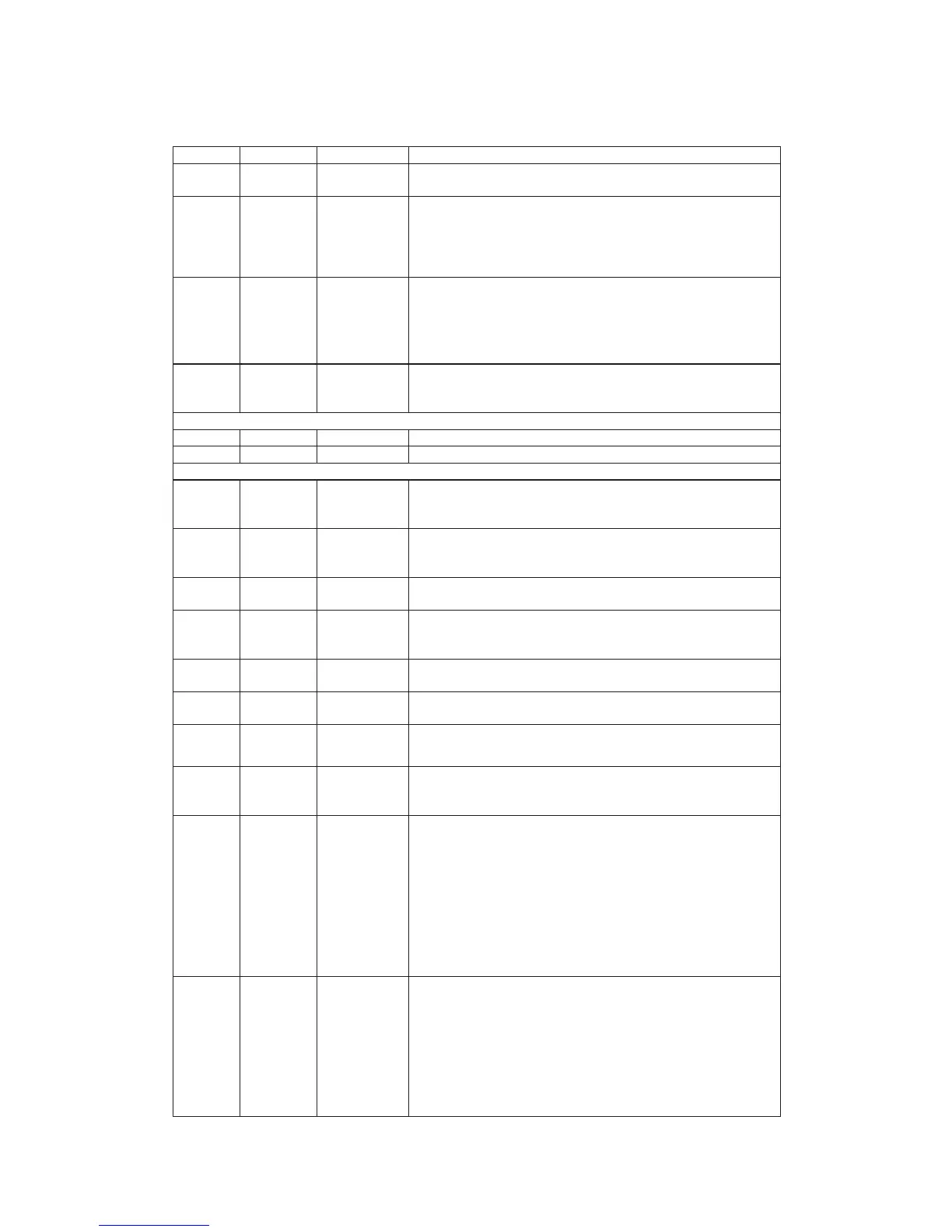

Pin Numbers Pin NAME Type Description

72 RW E# TTL Output

RAM write enable, low active. When two write enable pins are used, it only

for low byte.

73

CASH#/RWE

H#

TTL Output

High column address strobe: W rite enable High Byte

Multi-function pin: low active

RAM column address strobe for high byte, when two column address

strobe pins are used.

W rite enable for high byte, when two write enable pins are used.

74 CAS# TTL O utput

W orld RAM column address strobe: Low colum n address strobe

Multi-function pin: low active

RAM column address strobe for a word, when two column address strobe

pins are not used.

It is used only for low byte, when two column address strobe pins are used.

76-83,

85-87

90-94

RD[15:0] TTL I/O RAM data bus

System Clock Interface

88 IPLLVDD Power Power pin for system varipitch circuitry.

89 IPLLVSS Ground G round pin for system varipitch circuitry.

Host Interface

101 DASP#

TTL I/O

50K pull up

Drive active/Slave present

This is the time-multiplexed signal that indicates that a device is active, or

that slave is present.

102 CS3FX#

TTL Input

50K pull up

Host chip select 2(for 3FXH/37xh)

The CX3FX# and CS1FX# are chip select signals from the host used to

select the Com mand Block registers.

103 CS1FX#

TTL Input

50K pull up

Host chip select 1 (for 1Fxh/17xh)

105,108,10

6

HA[2:0]

TTL Input

50K pull up

Host address bus

This is the 3-bit binary coded address asserted by the host to access a

register or data port in the device.

107 PDIAG#

TTL I/O

50K pull up

Passed diagnostics

110 IO CS16#

TTL Output

Open drain

I/O 16-bit chip select

111 INTRQ TTL O utput

Host interrupt.

The MT1368 uses this signal to interrupt the host system .

112 DMACK#

TTL Input

50K pull up

DMA acknowledge.

This signal shall be used by the host in response to DMAREQ to initiate

DMA transfers.

113 IO RDY TTL Output

I/O channel ready: Ultra DMA ready: Ultra DMA data strobe.

This is a multi-function pin.

For i/o channel Ready, this signal is negated to extend the host transfer

cycle of any register read or write when the device is not able to complete

the transfer.

For Ultra DMA Ready, this signal is asserted by the device to indicate to the

host that the device is ready to receive Ultra DMA data out bursts from the

host.

For Ultra DMA data strobe, this is the data in strobe signal from device for

Ultra DMA data in burst to host.

114 DIOR#

TTL Input

50K pull up

Device I/O read: Ultra DMA ready: Ultra DMA data strobe.

This is m ulti-function pin.

For Device I/O Read, this signal is the strobe signal asserted by the host to

read device registers or the data port.

For Ultra DMA read, this is asserted by the host to indicate to the device

that the host is ready to receive Ultra DMA data in burst to host

For Ultra DMA data strobe, this signal is the data out strobe signal from the

host for an Ultra DMA data out burst.

11

Loading...

Loading...