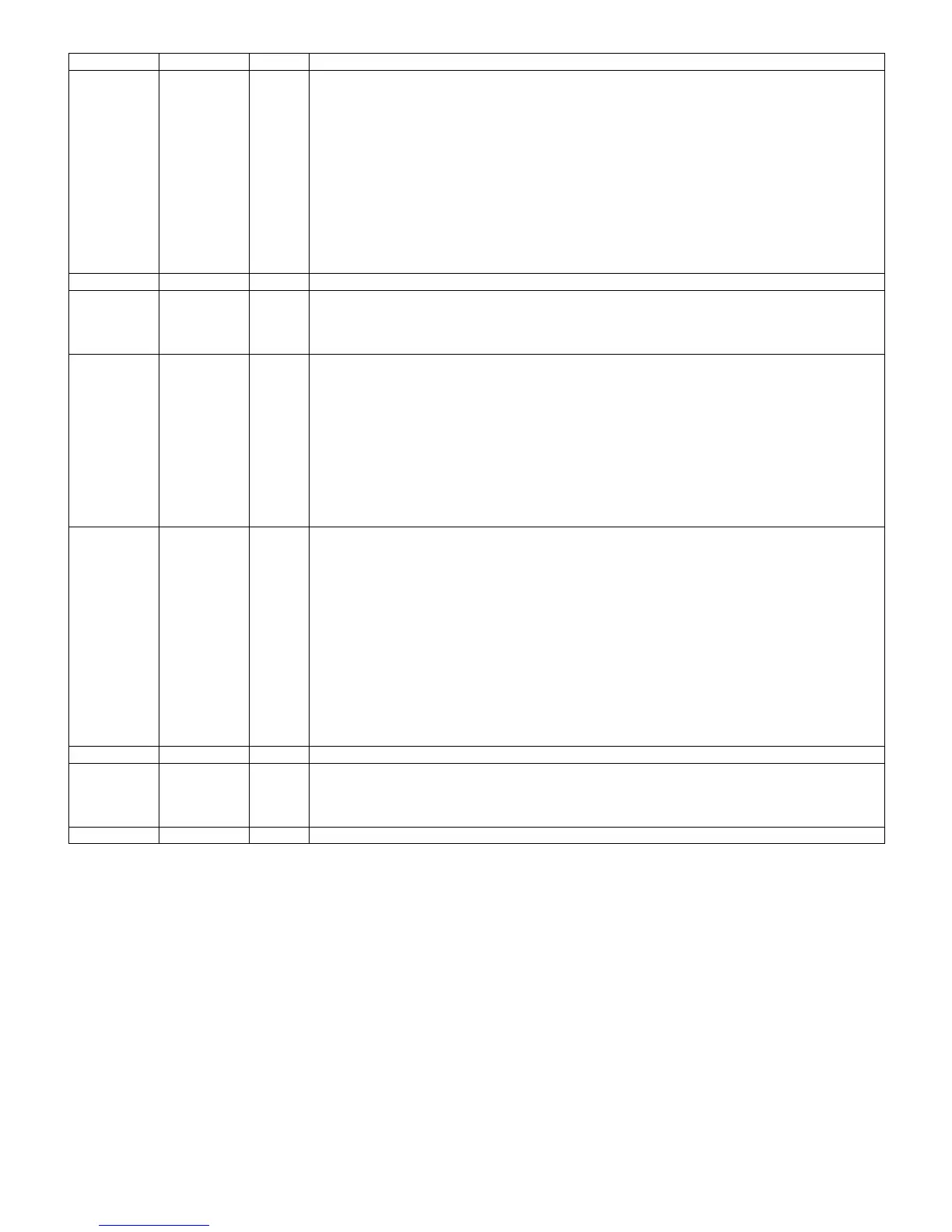

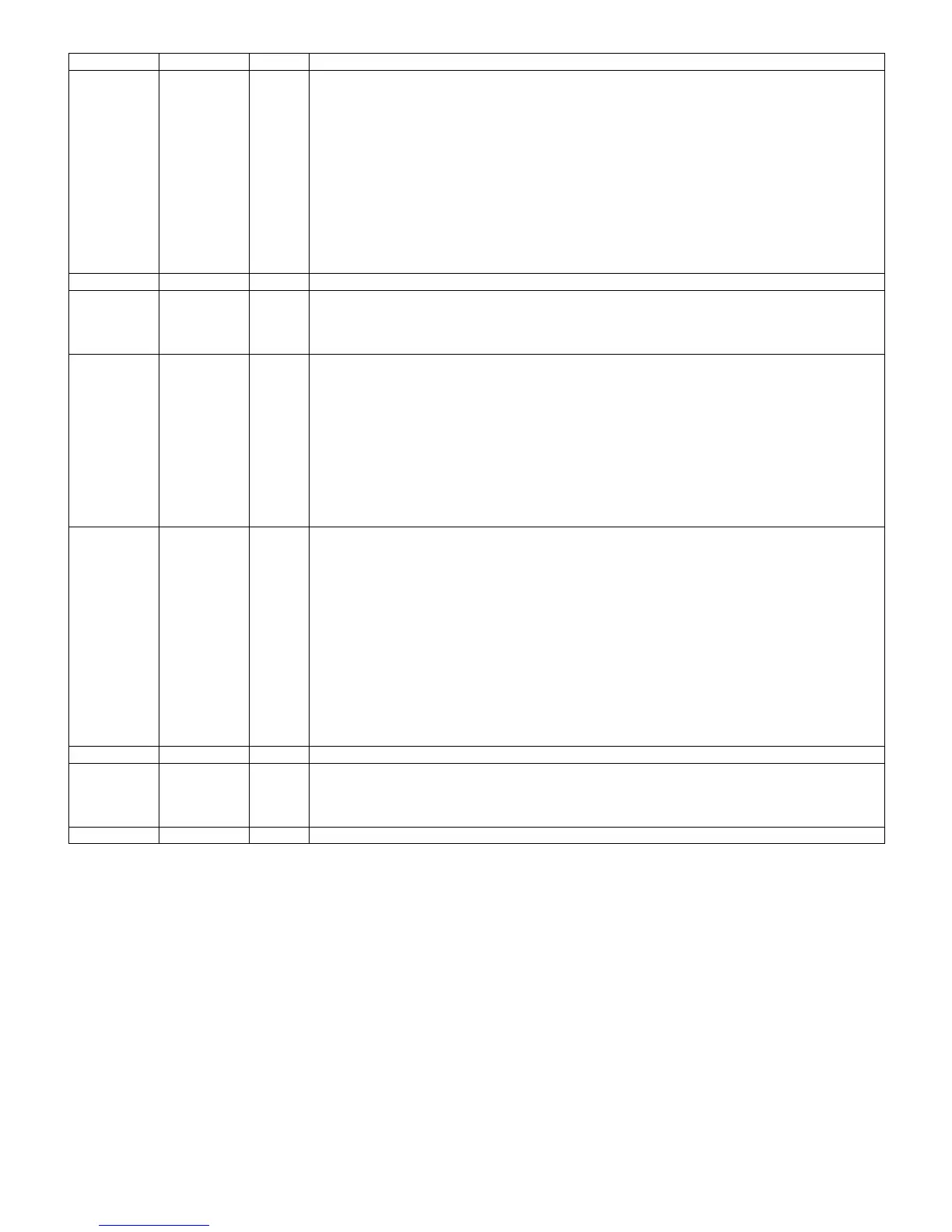

LC-37D90U

5 – 36

*1 : The timing reference point for the differential clocking is the cross point of CK and CK.

For any applications using the single ended clocking, apply VREF to CK pin.

7B, 6C, 6B,

5B, 2C, 3D,

2D, 2E, 13K,

12K, 13J,

12J, 13G,

12G, 13F,

12F, 3F, 2F,

3G, 2G, 3J,

2J, 3K, 2K,

13E, 13D,

12D, 13C,

10B, 9B, 9C,

8B

DQ0 - DQ31 I/O Data inputs/Outputs are multiplexed on the same pins.

4N, 5M BA0, BA1 I Selects which bank is to be active.

5N, 6N, 6M,

7N, 8N, 9M,

9N, 10N, 11N,

8M, 6L, 7M

A0 - A11 I Row/Column addresses are multiplexed on the same pins.

Row addresses : RA0 - RA11, Column addresses : CA0 - CA7.

Column address CA8 is used for auto precharge.

4E, 4L, 7D,

7L, 8D, 8L,

11E, 11L, 5E,

5L, 6F, 6G,

6H, 6J, 6K,

7E, 7F, 7G,

7H, 7J, 7K,

8E, 8F, 8G,

8H, 8J, 8K,

9F, 9G, 9J,

9K, 10E, 10L

VDD/VSS --- Power and ground for the input buffers and core logic.

3C, 3E, 4F,

4G, 4J, 4K,

5C, 7C, 8C,

10C, 11F,

11G, 11J,

11K, 12C,

12E, 4B, 4D,

5D, 5F, 5G,

5H, 5J, 5K,

6D, 6E, 9D,

9E, 10F, 10G,

10H, 10J,

10K, 11B,

11D

VDDQ/VSSQ --- Isolated power supply and ground for the output buffers to provide improved noise immunity.

13N VREF --- Reference voltage for inputs, used for SSTL interface.

3M, 3N, 4C,

4H, 4M, 11C,

11H, 12L,

13L, 9L, 10L

NC/RFU --- This pin is recommended to be left “No connection” on the device.

13M MCL --- Must connect low.

Pin No. Pin Name I/O Pin Function

Loading...

Loading...