LC-37D90U

5 – 39

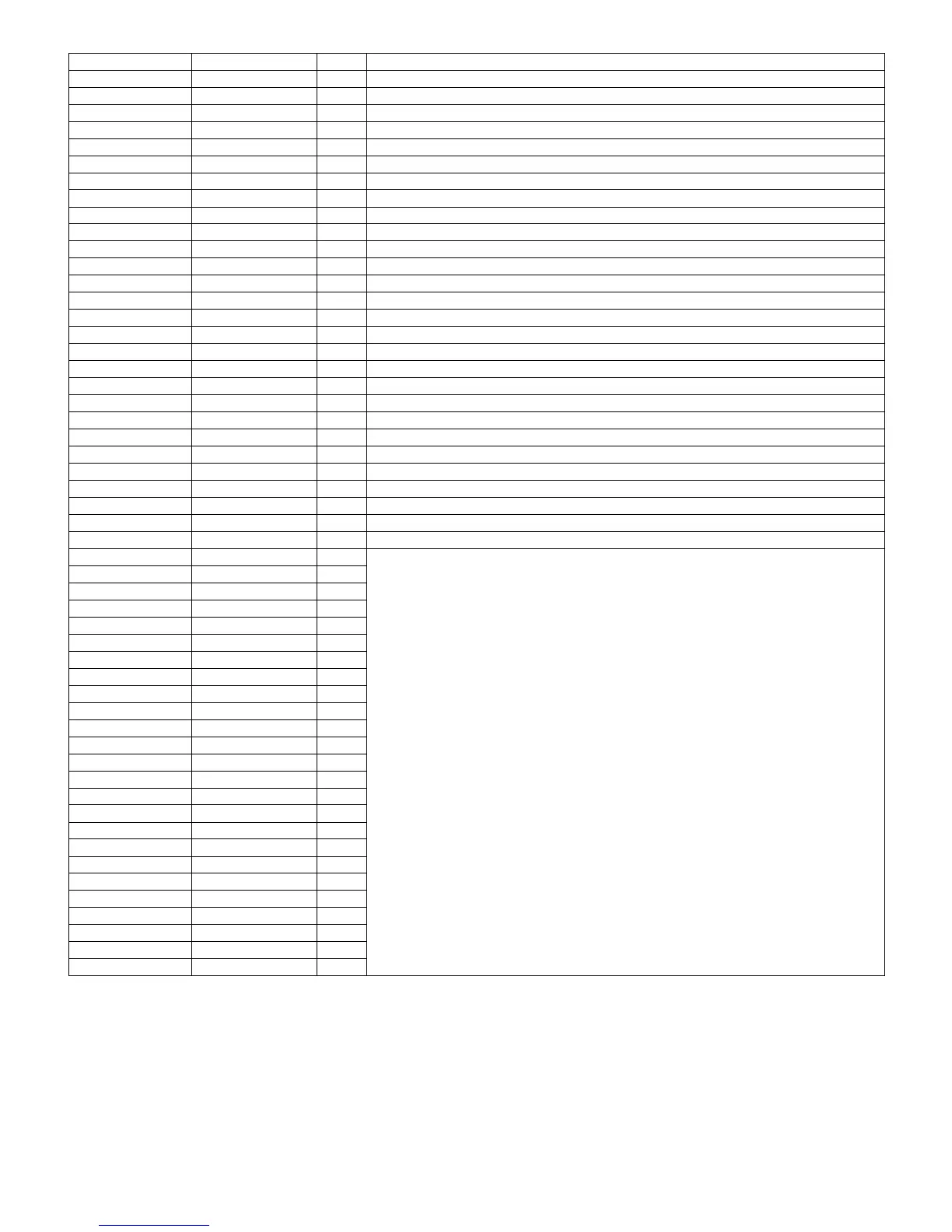

AD3 SDCLK1 O SDRAM clock1.

J3 SDCLK0 O SDRAM clock0.

AC4 SDBCLK1 O SDRAM clock1 for DDR.

K4 SDBCLK0 O SDRAM clock0 for DDR.

V1 SDCKE O SDRAM clock enable.

AD4 SDCS1_N O SDRAM chip select1.

K3 SDCS0_N O SDRAM chip select0.

U2 SDRAS_N O SDRAM row address strobe.

U1 SDCAS_N O SDRAM column address strobe.

V2 SDWE_N O SDRAM write enable.

AH2 SDDM7 O SDRAM I/O mask7.

AD2 SDDM6 O SDRAM I/O mask6.

Y4 SDDM5 O SDRAM I/O mask5.

AC3 SDDM4 O SDRAM I/O mask4.

N4 SDDM3 O SDRAM I/O mask3.

L4 SDDM2 O SDRAM I/O mask2.

G4 SDDM1 O SDRAM I/O mask1.

J4 SDDM0 O SDRAM I/O mask0.

T2 SDBA1 O SDRAM bank address select1.

T1 SDBA0 O SDRAM bank address select0.

AJ1 SDDQS7 I/O SDRAM data strobe7 for DDR.

AD1 SDDQS6 I/O SDRAM data strobe6 for DDR.

Y3 SDDQS5 I/O SDRAM data strobe5 for DDR.

AB4 SDDQS4 I/O SDRAM data strobe4 for DDR.

P4 SDDQS3 I/O SDRAM data strobe3 for DDR.

L3 SDDQS2 I/O SDRAM data strobe2 for DDR.

F4 SDDQS1 I/O SDRAM data strobe1 for DDR.

H3 SDDQS0 I/O SDRAM data strobe0 for DDR.

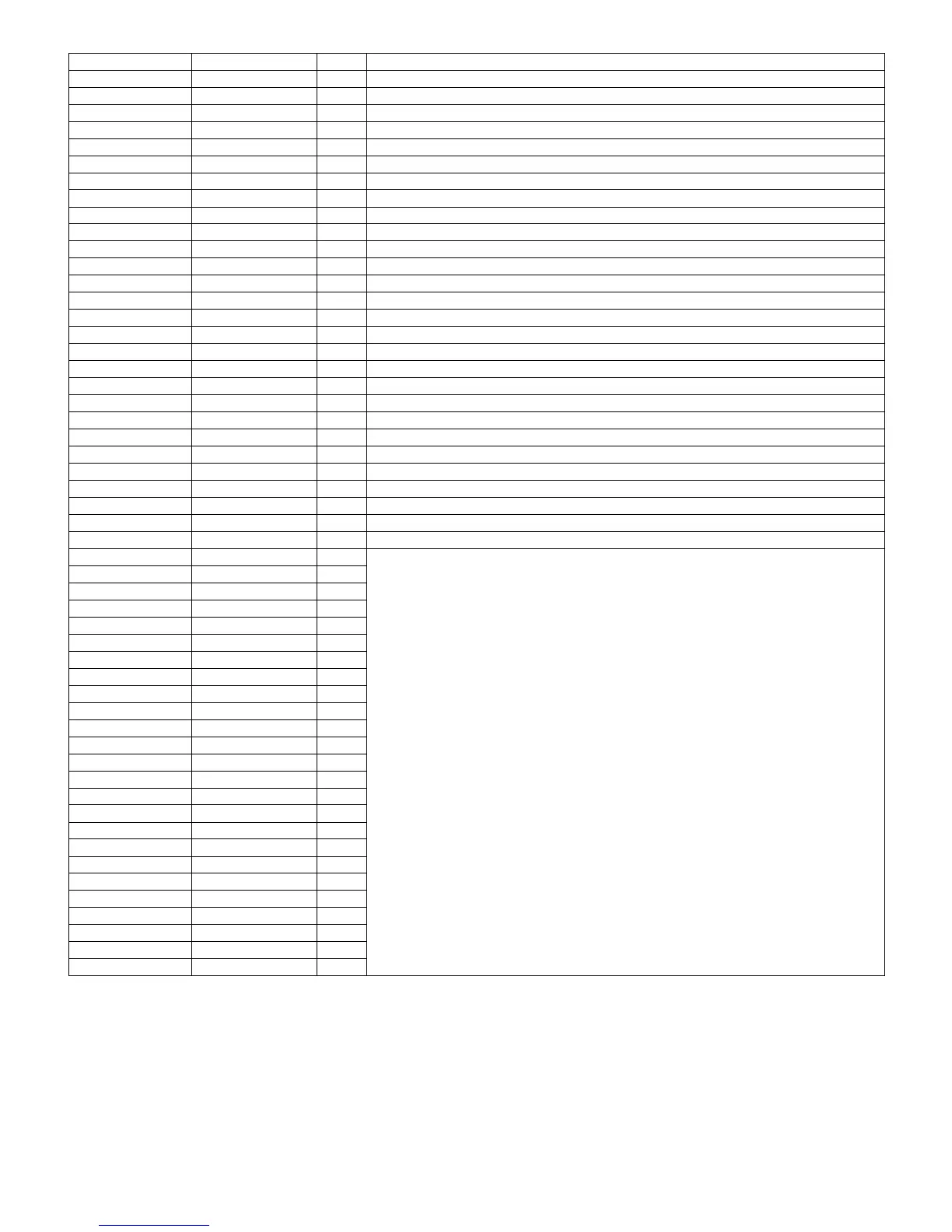

A32 SBADD25 I/O Address.

B33 SBADD24 I/O

B32 SBADD23 I/O

B31 SBADD22 I/O

C30 SBADD21 I/O

C31 SBADD20 I/O

C32 SBADD19 I/O

C33 SBADD18 I/O

D33 SBADD17 I/O

D32 SBADD16 I/O

D31 SBADD15 I/O

D30 SBADD14 I/O

E29 SBADD13 I/O

E30 SBADD12 I/O

E31 SBADD11 I/O

E32 SBADD10 I/O

E33 SBADD9 I/O

F33 SBADD8 I/O

F32 SBADD7 I/O

F31 SBADD6 I/O

F30 SBADD5 I/O

F29 SBADD4 I/O

G30 SBADD3 I/O

G31 SBADD2 I/O

G32 SBADD1 I/O

Pin No. Pin Name I/O Pin Function

Loading...

Loading...