LC-37D90U

5 – 51

P9 JTAG_TCK I JTAG Test Clock pin.

N9 JTAG_TRSTn I JTAG Reset pin. Active Low only.

MCIF Interface (PCI, 68K and SRAM-Like Interface

A14 MCIF_SEL1 I Microcontroller Interface Select. This pin is sampled at power-up and reset.

MCIF_SEL [1: 0].

00: SRAM-like I/F with fixed wait.

01: SRAM-like I/F with handshake.

10: 68k I/F.

11: PCI interface.

E9 MCIF_SEL0

F4 PCI_CLK I PCI Clock. Max frequency is 33MHz.

F2 PCI_INTAn

(MCIF_INTn)

O PCI Interrupt A. Open drain signal.

SRAM-like Interface Interrupt. (Active low)

68k-I/F Interrupt. (Active low)

K6 PCI_C/BE0n I/O PCI Bus Command/Byte Enable 0.

L5 PCI_C/BE1n I/O PCI Bus Command/Byte Enable 1.

M1 PCI_C/BE2n I/O PCI Bus Command/Byte Enable 2.

H4 PCI_C/BE3n I/O PCI Bus Command/Byte Enable 3.

P1 PCI_DEVSELn

(MCIF_ACKn)

I/O PCI Device Select. (Active low)

SRAM-like Interface Acknowledge. (Active low)

68k-I/F Acknowledge. (Active low)

M2 PCI_FRAMEn

(MCIF_REn/

MCIF_R_nW)

I/O PCI Cycle Frame. (Active low)

SRAM-like Interface Read Enable. (Active low)

68k-I/F Read/Write enable. Ex-CPU drives this signal to 1 for aread operation and 0 for a write oper-

ation.

G2 PCI_GNTn I PCI Grant. (Active low)

J3 PCI_IDSEL I PCI Initialization Device Select.

N1 PCI_IRDYn I/O PCI Initiator Ready. (Active low)

N5 PCI_PERRn I/O PCI Parity Error. (Active low)

M4 PCI_PAR

(MCIF_LITTLE_ENDIA

N)

I/O PCI Parity.

SRAM-like Interface Endianness setting. When set to 1, the interface will be byte swapped (based

on 4 bytes). When set to 0, the interface byte order will not be changed.

68k-I/F Endianness setting. When set to 1, the interface will be byte swapped (based on 4 bytes).

When set to 0, the interface byte order will not be changed.

F1 PCI_REQn O PCI Request. (Active low)

P4 PCI_SERRn O PCI System Error. (Active low)

P2 PCI_STOPn

(MCIF_CSn)

I/O PCI Stop. (Active low)

SRAM-like Interface Chip Select. (Active low)

68k-I/F Chip Select. (Active low)

M3 PCI_TRDYn

(MCIF_Wen/

MCIF_STRBn)

I/O PCI Target Ready. (Active low)

SRAM-like Interface Chip Select. (Active low)

68k-I/F Strobe Signal. (Active low)

Note: Please note that PCI address/data line sequencing does not match SRAM or 68K mode. For example PCI_AD [6] is multiplexed with MCIF_D

[7]. Signals with mismatching sequence are highlighted in RED.

Please be extra cautious with routing data/address line correctly on PCB.

F5 PCI_AD [31] I/O PCI Address/Data 31.

G3 PCI_AD [30] I/O PCI Address/Data 30.

G1 PCI_AD [29] I/O PCI Address/Data 29.

H3 PCI_AD [28] I/O PCI Address/Data 28.

H1 PCI_AD [27] I/O PCI Address/Data 27.

H5 PCI_AD [26] I/O PCI Address/Data 26.

H2,J4,

J1, K4,

J2, K1,

L1, L3

PCI_AD [25-16]

(MCIF_A [11-2])

I/O PCI Address/Data 25-16.

SRAM-Like or 68k-I/F Address 11-2.

P3, M5,

P5, N6,

P6, L6,

M6, N7,

P7, L7,

M8, K7,

P8, L8,

N8, K8

PCI_AD [15-0]

(MCIF_D [15-0])

I/O PCI Address/Data 15-0.

SRAM-Like or 68k-I/F Data 15-0.

Note: Please note that PCI address/data line sequencing does not match SRAM or 68K mode. For example PCI_AD [6] is multiplexed with MCIF_D

[7].

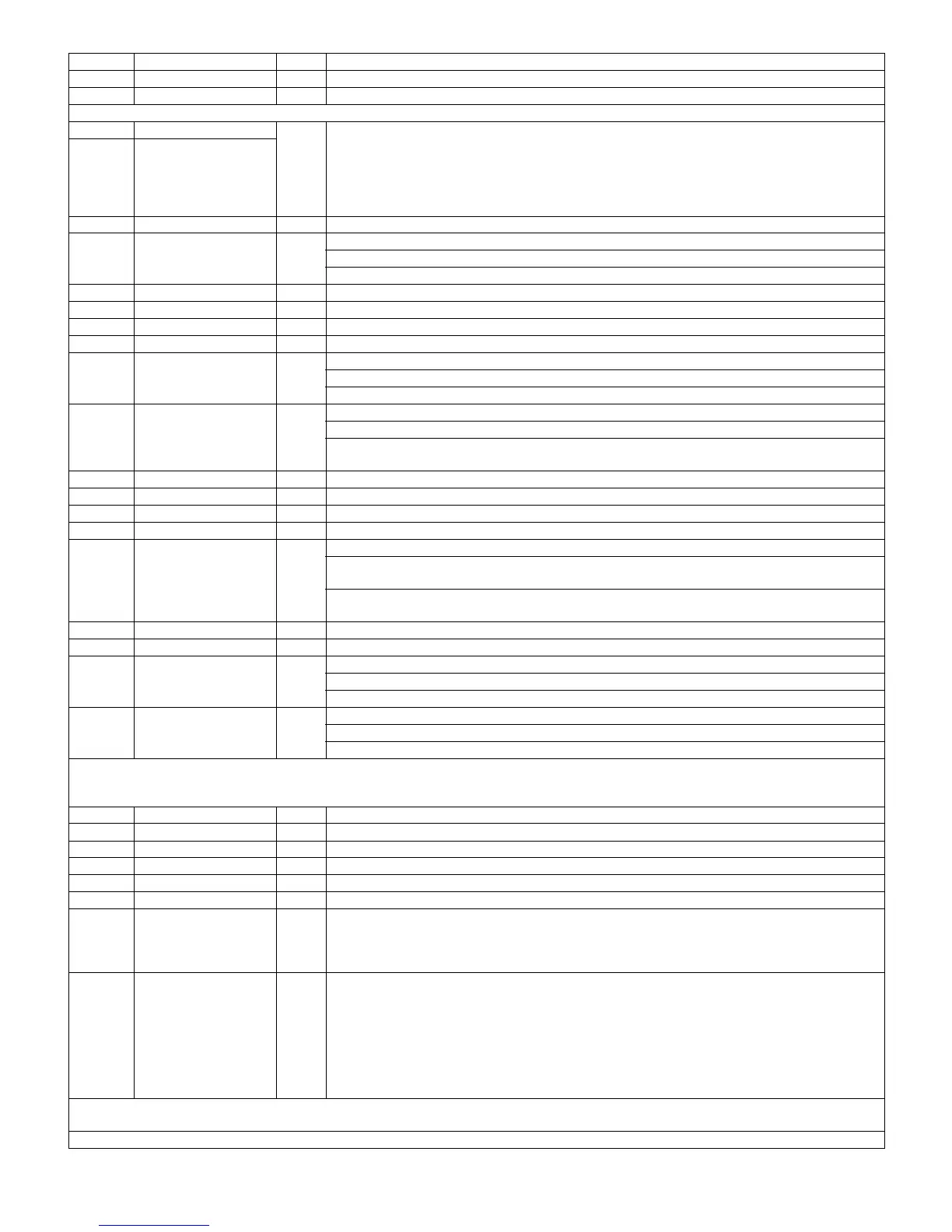

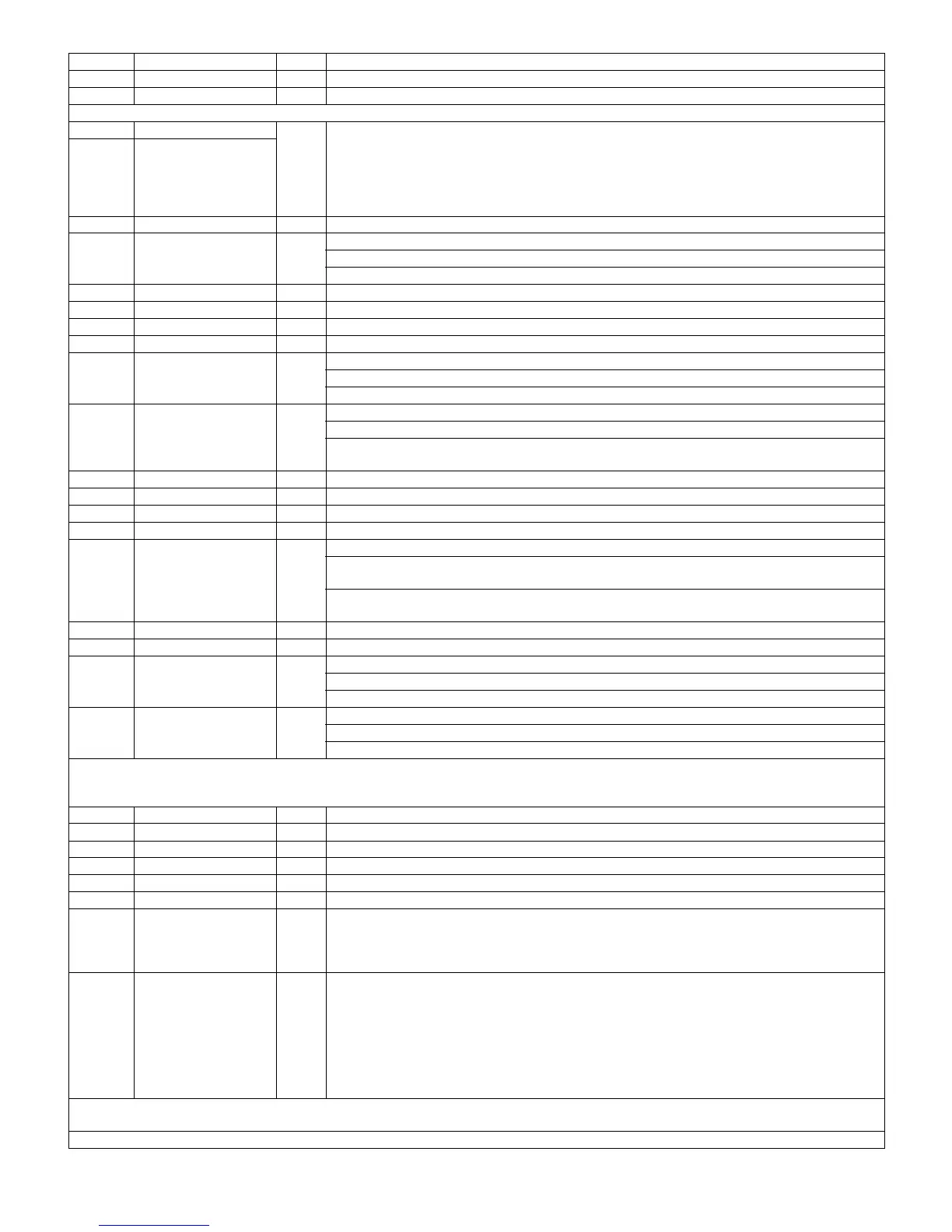

External DMA

Pin No. Pin Name I/O Pin Function

Loading...

Loading...