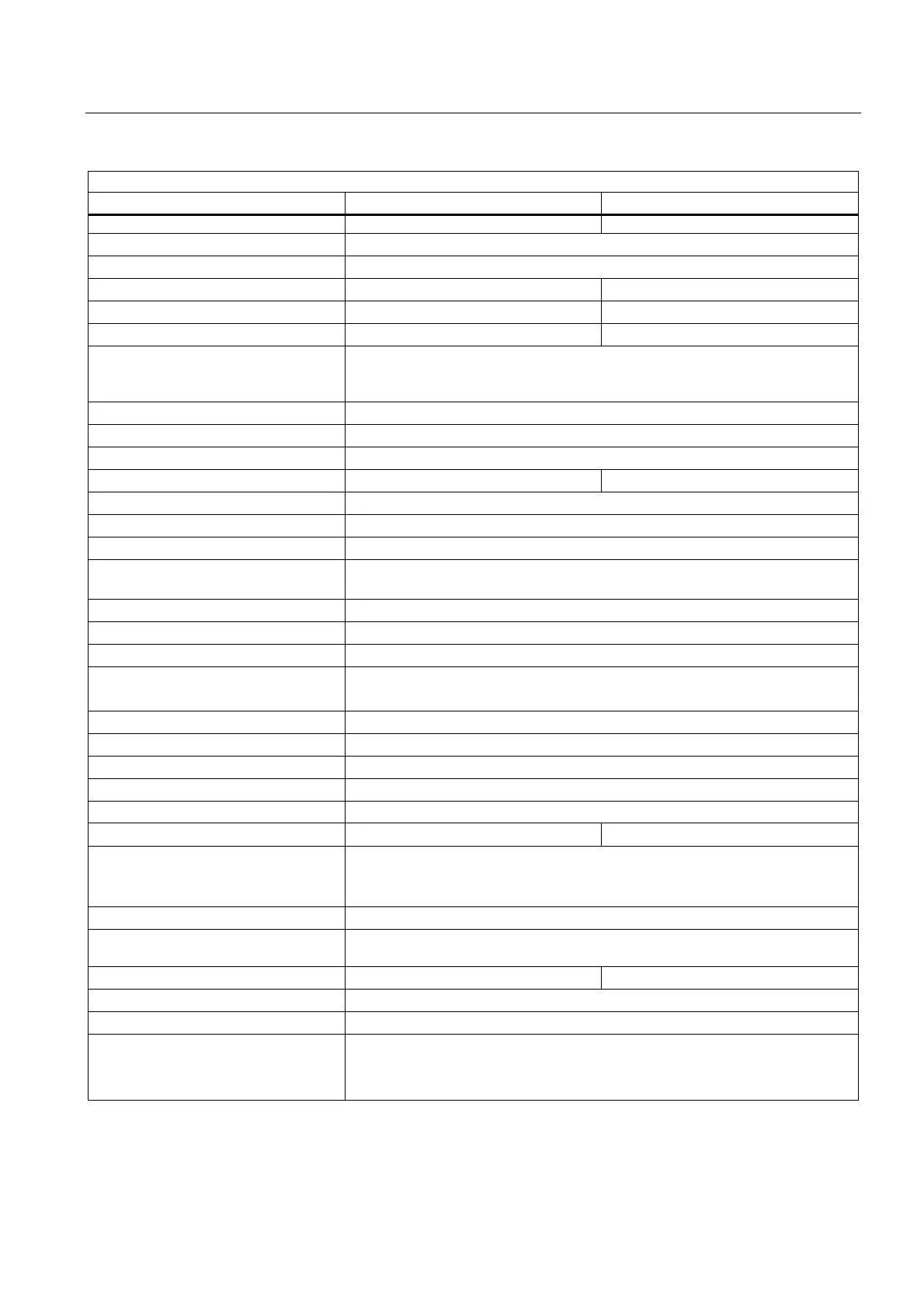

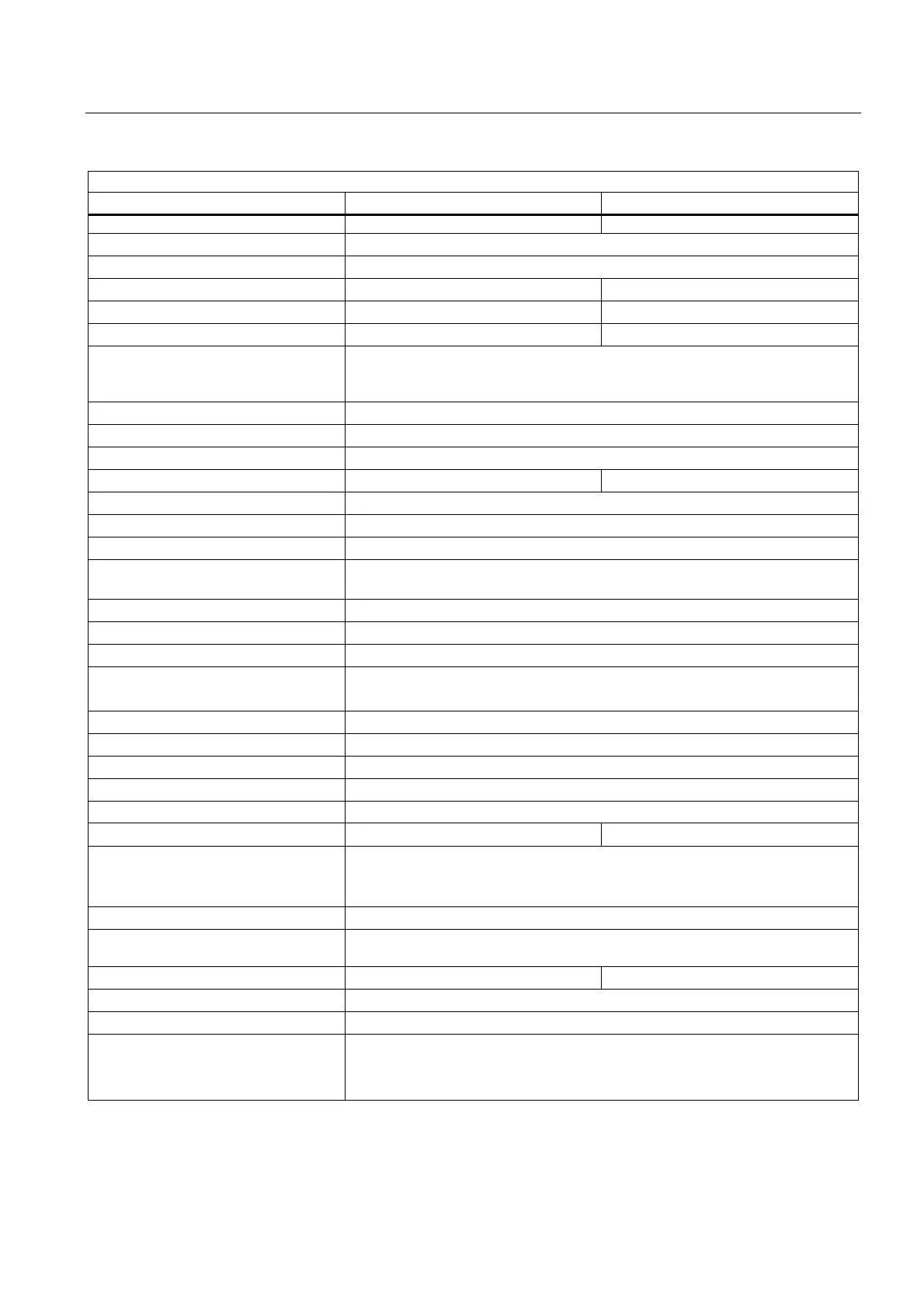

Technical data of CPU 31xC

6.5 CPU 314C-2 PtP and CPU 314C-2 DP

CPU 31xC and CPU 31x, Technical Data

Manual, 01/2006 Edition, A5E00105475-06

6-23

Technical data

CPU 314C-2 PtP CPU 314C-2 DP

Assembly CPU 314C-2 PtP CPU 314C-2 DP

Racks Max. 4

Modules per rack Max. 8; Max. 7 in rack 3

Number of DP masters

• Integrated

No 1

• via CP

4 4

Number of function modules and

communication processors you can

operate

• FM

Max. 8

• CP (PtP)

Max. 8

• CP (LAN)

Max. 10

Time-of-day CPU 314C-2 PtP CPU 314C-2 DP

Real-time clock Yes (HW clock)

• Buffered

Yes

• Buffered period

Typically 6 weeks (at an ambient temperature of 40 °C)

• Behavior of the clock on expiration

of the buffered period

The clock keeps running, continuing at the time-of-day it had when power was

switched off.

• Accuracy

Deviation per day < 10 s

Operating hours counter 1

• Number

0

• Value range

2

31

hours

(if SFC 101 is used)

• Granularity

1 hour

• Retentive

Yes; must be manually restarted after every restart

Clock synchronization Yes

• In the PLC

Master

• On MPI

Master/slave

S7 signaling functions CPU 314C-2 PtP CPU 314C-2 DP

Number of stations that can log in for

signaling functions (e.g. OS)

Max. 12

(depends on the number of connections configured for PG / OP and S7 basic

communication)

Process diagnostics messages Yes

• Simultaneously enabled interrupt S

blocks

Max. 40

Testing and commissioning functions CPU 314C-2 PtP CPU 314C-2 DP

Status/control variables Yes

• Variables

Inputs, outputs, memory bits, DBs, timers, counters

• Number of variables

– of those as status variable

– of those as control variable

Max. 30

Max. 30

Max. 14

Loading...

Loading...