– 17 – – 8 –– 15 – – 16 –

CFD-S33

r

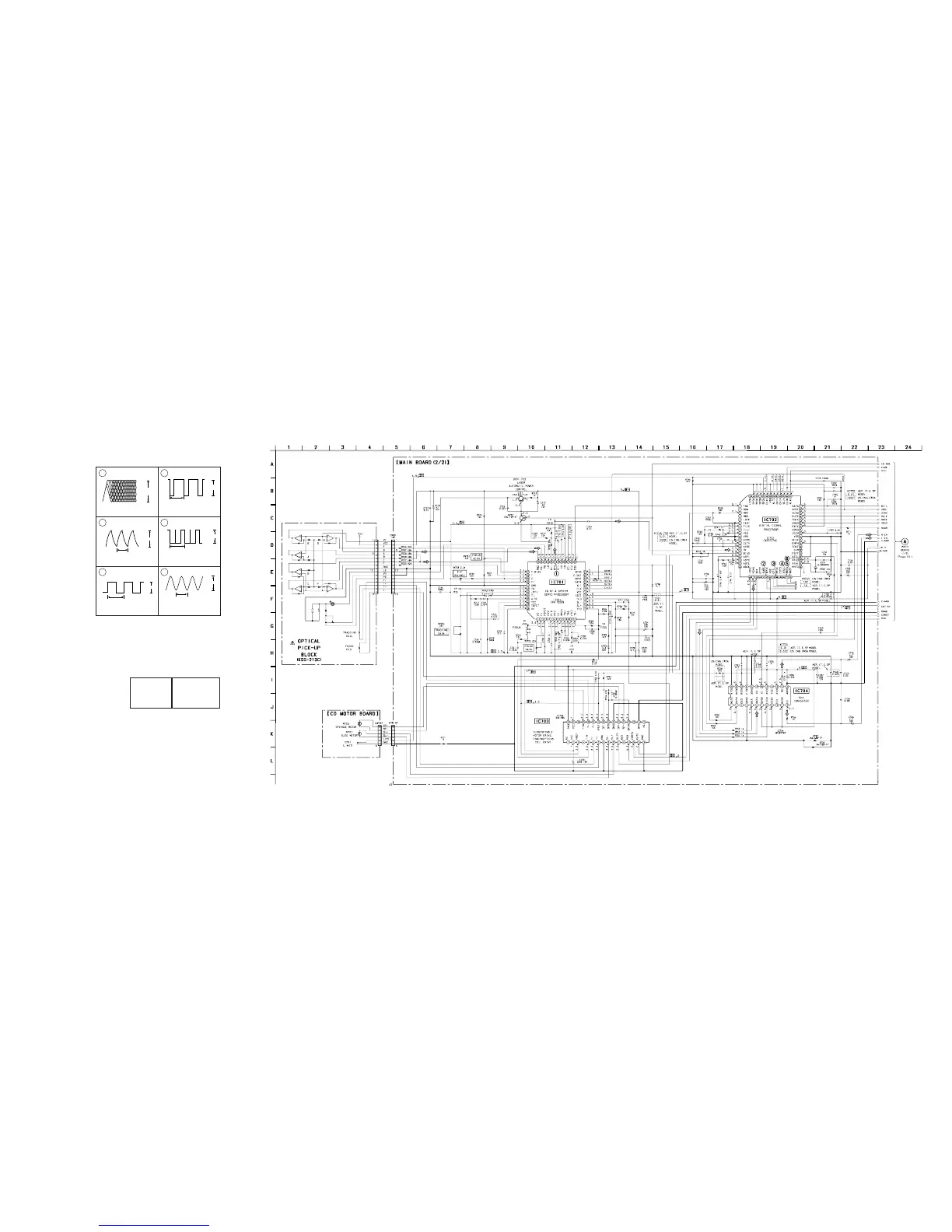

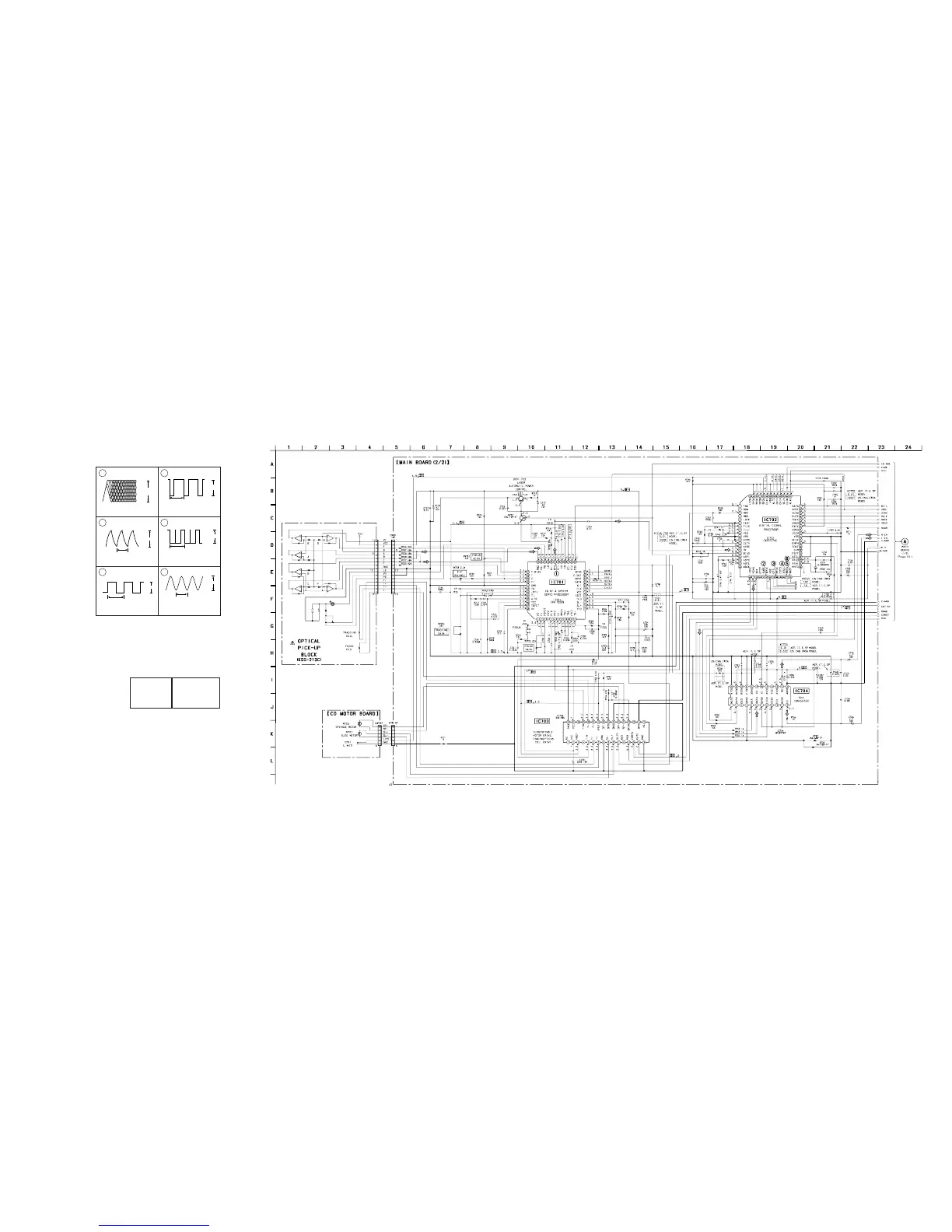

SCHEMATIC DIAGRAM – MAIN SECTION (2/2) –

Note:

• All capacitors are in µF unless otherwise noted. pF: µµF

50 WV or less are not indicated except for electrolytics

and tantalums.

• All resistors are in Ω and

1

/

4

W or less unless otherwise

specified.

Note: Note:

The components identi- Les composants identifiés

fied by mark ! or dotted par une marque ! sont cri-

line with mark ! are cri- tiques pour la sécurité.

tical for safety. Ne les remplacer que par

Replace only with part une piéce portant le

number specified. numéro spécifié.

• U : B+ Line.

• H : adjustment for repair.

• Power voltage is dc 9 V and fed with regulated dc power

supply from external power voltage jack.

• Voltages and waveforms are dc with respect to ground

under no-signal (detuned) conditions.

no mark : CD STOP

• Voltages are taken with a VOM (Input impedance 10 MΩ).

Voltage variations may be noted due to normal produc-

tion tolerances.

• Waveforms are taken with a oscilloscope.

Voltage variations may be noted due to normal produc-

tion tolerances.

• Circled numbers refer to waveforms.

• Signal path.

J : CD

r

Waveforms

1

IC701 #¡

(RFO)

4

2 5

3 6

(PLAY MODE)

VOLT/DIV : 0.2 V AC

TIME/DIV : 0.5 µsec

IC702 @∞

(XPCK)

VOLT/DIV : 1 V AC

TIME/DIV : 0.1 msec

VOLT/DIV : 1 V AC

TIME/DIV : 50 µsec

VOLT/DIV : 1 V AC

TIME/DIV : 50 µsec

VOLT/DIV : 1 V AC

TIME/DIV : 50 µsec

VOLT/DIV : 0.2 V AC

TIME/DIV : 50 nsec

IC702 @•

(RFCK)

IC702 #¡

(MNT3)

IC702 #™

(MNT1)

IC702 #∞

(XTAO)

1.0 – 1.4

Vp-p

4.8 Vp-

Loading...

Loading...