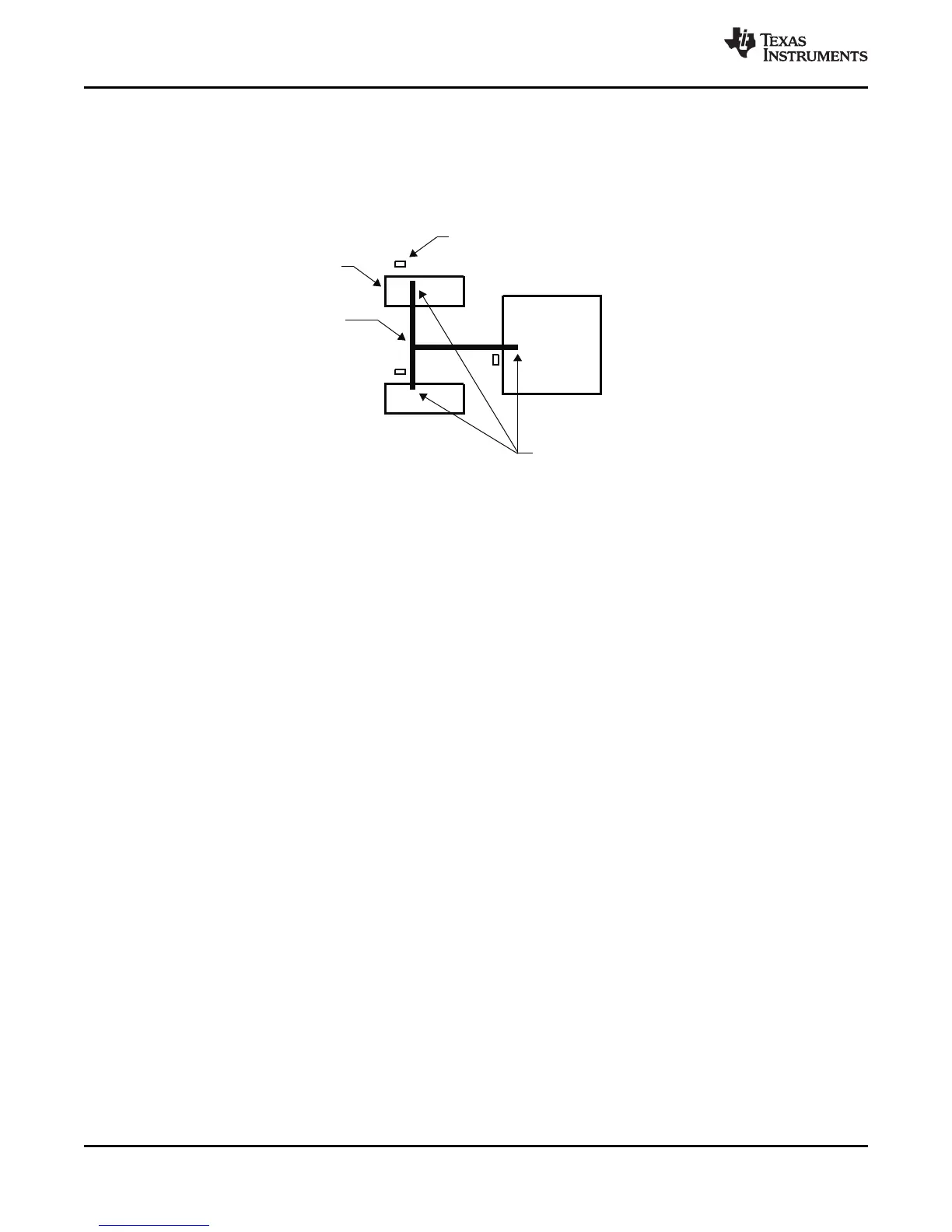

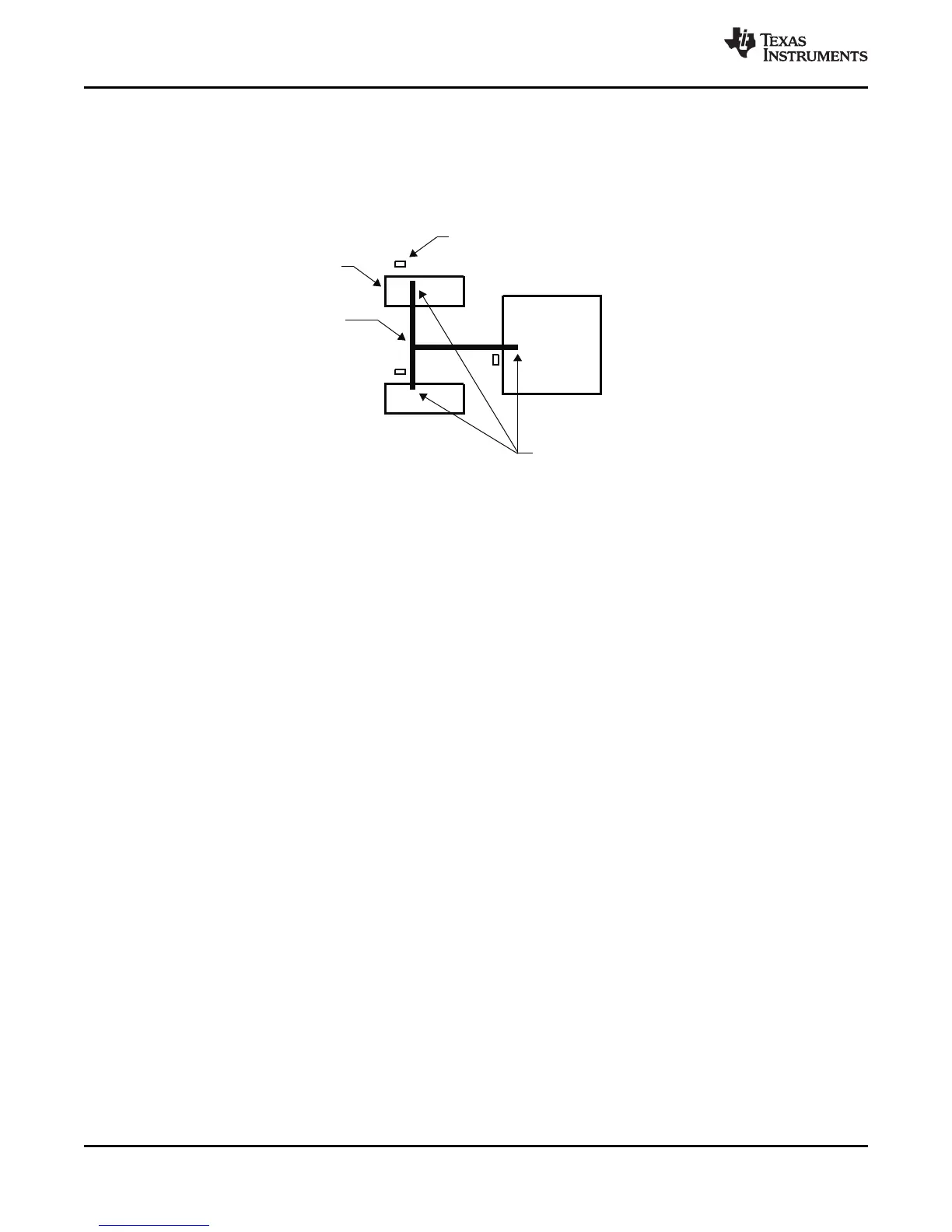

A1

A1

DDR2/mDDRDevice

VREFNominalMinimum

TraceWidthis20Mils

VREFBypassCapacitor

NeckdowntominimuminBGA escape

regionsisacceptable.Narrowingto

accomodateviacongestionforshort

distancesisalsoacceptable.Best

performanceisobtainedifthewidth

ofVREFismaximized.

DDR2/mDDR

AM1808

SPRS653E –FEBRUARY 2010–REVISED MARCH 2014

www.ti.com

6.11.3.10 VREF Routing

VREF is used as a reference by the input buffers of the DDR2/mDDR memories as well as the device.

VREF is intended to be half the DDR2/mDDR power supply voltage and should be created using a

resistive divider as shown in Figure 6-16. Other methods of creating VREF are not recommended.

Figure 6-20 shows the layout guidelines for VREF.

Figure 6-20. VREF Routing and Topology

118 Peripheral Information and Electrical Specifications Copyright © 2010–2014, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM1808

Loading...

Loading...