AM1808

SPRS653E –FEBRUARY 2010–REVISED MARCH 2014

www.ti.com

6.18.3 I2C Electrical Data/Timing

6.18.3.1 Inter-Integrated Circuit (I2C) Timing

Table 6-85 and Table 6-86 assume testing over recommended operating conditions (see Figure 6-41 and

Figure 6-42).

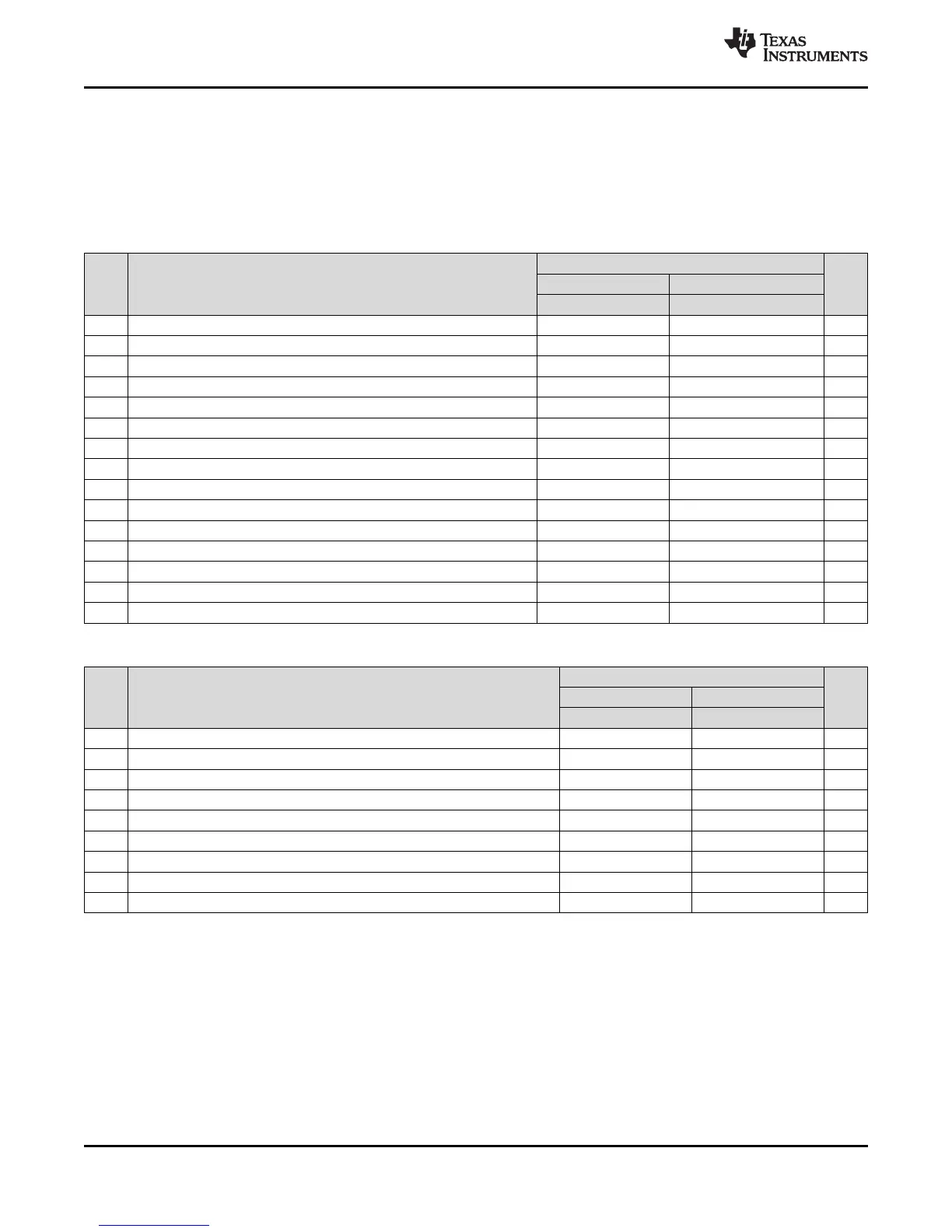

Table 6-85. Timing Requirements for I2C Input

1.3V, 1.2V, 1.1V, 1.0V

NO. Standard Mode Fast Mode UNIT

MIN MAX MIN MAX

1 t

c(SCL)

Cycle time, I2Cx_SCL 10 2.5 μs

2 t

su(SCLH-SDAL)

Setup time, I2Cx_SCL high before I2Cx_SDA low 4.7 0.6 μs

3 t

h(SCLL-SDAL)

Hold time, I2Cx_SCL low after I2Cx_SDA low 4 0.6 μs

4 t

w(SCLL)

Pulse duration, I2Cx_SCL low 4.7 1.3 μs

5 t

w(SCLH)

Pulse duration, I2Cx_SCL high 4 0.6 μs

6 t

su(SDA-SCLH)

Setup time, I2Cx_SDA before I2Cx_SCL high 250 100 ns

7 t

h(SDA-SCLL)

Hold time, I2Cx_SDA after I2Cx_SCL low 0 0 0.9 μs

8 t

w(SDAH)

Pulse duration, I2Cx_SDA high 4.7 1.3 μs

9 t

r(SDA)

Rise time, I2Cx_SDA 1000 20 + 0.1C

b

300 ns

10 t

r(SCL)

Rise time, I2Cx_SCL 1000 20 + 0.1C

b

300 ns

11 t

f(SDA)

Fall time, I2Cx_SDA 300 20 + 0.1C

b

300 ns

12 t

f(SCL)

Fall time, I2Cx_SCL 300 20 + 0.1C

b

300 ns

13 t

su(SCLH-SDAH)

Setup time, I2Cx_SCL high before I2Cx_SDA high 4 0.6 μs

14 t

w(SP)

Pulse duration, spike (must be suppressed) N/A 0 50 ns

15 C

b

Capacitive load for each bus line 400 400 pF

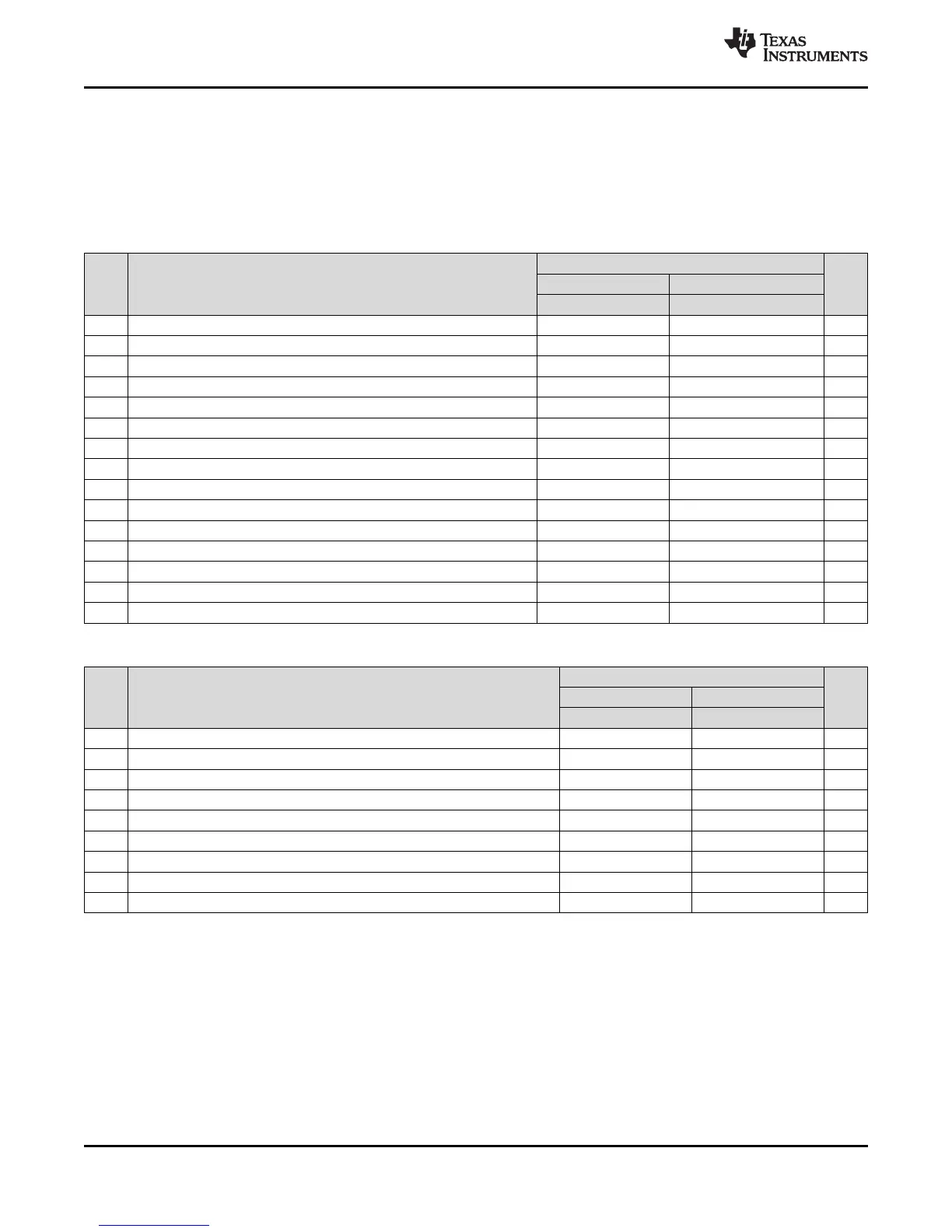

Table 6-86. Switching Characteristics for I2C

(1)

1.3V, 1.2V, 1.1V, 1.0V

NO. PARAMETER Standard Mode Fast Mode UNIT

MIN MAX MIN MAX

16 t

c(SCL)

Cycle time, I2Cx_SCL 10 2.5 μs

17 t

su(SCLH-SDAL)

Setup time, I2Cx_SCL high before I2Cx_SDA low 4.7 0.6 μs

18 t

h(SDAL-SCLL)

Hold time, I2Cx_SCL low after I2Cx_SDA low 4 0.6 μs

19 t

w(SCLL)

Pulse duration, I2Cx_SCL low 4.7 1.3 μs

20 t

w(SCLH)

Pulse duration, I2Cx_SCL high 4 0.6 μs

21 t

su(SDAV-SCLH)

Setup time, I2Cx_SDA valid before I2Cx_SCL high 250 100 ns

22 t

h(SCLL-SDAV)

Hold time, I2Cx_SDA valid after I2Cx_SCL low 0 0 0.9 μs

23 t

w(SDAH)

Pulse duration, I2Cx_SDA high 4.7 1.3 μs

28 t

su(SCLH-SDAH)

Setup time, I2Cx_SCL high before I2Cx_SDA high 4 0.6 μs

(1) I2C must be configured correctly to meet the timings in Table 6-86.

174 Peripheral Information and Electrical Specifications Copyright © 2010–2014, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM1808

Loading...

Loading...