AM1808

SPRS653E –FEBRUARY 2010–REVISED MARCH 2014

www.ti.com

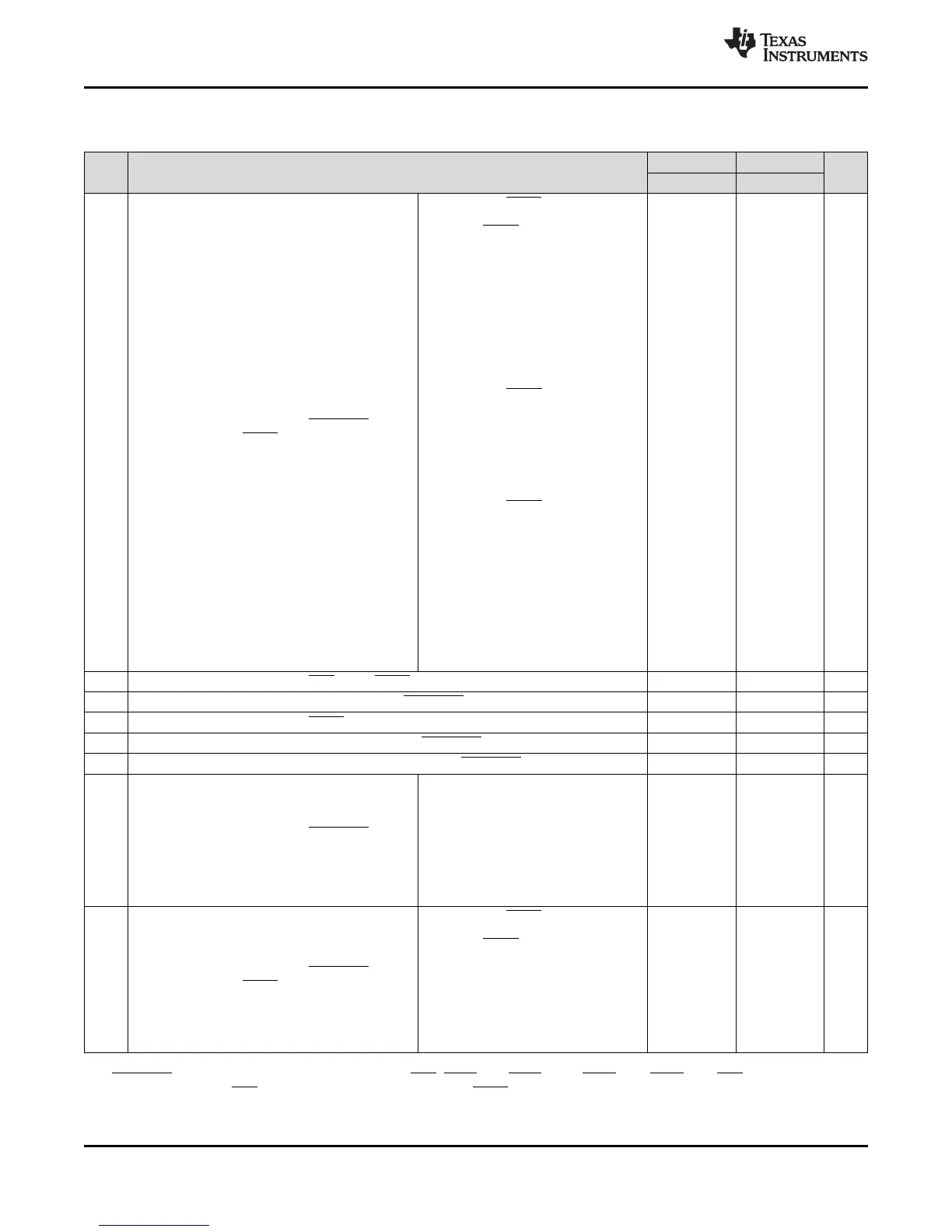

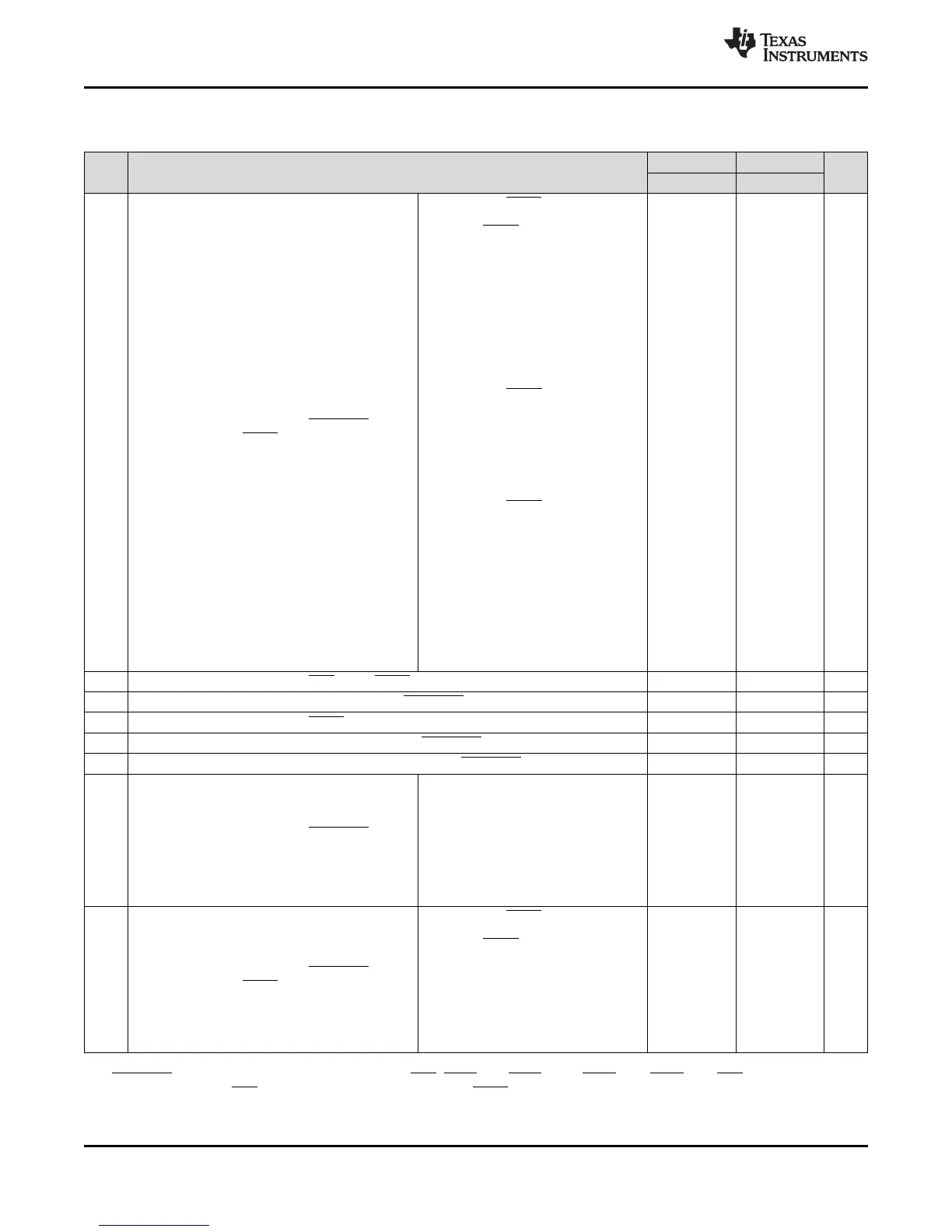

Table 6-113. Switching Characteristics Over Recommended Operating Conditions for Host-Port Interface

[1.3V, 1.2V, 1.1V]

(1) (2) (3)

1.3V, 1.2V 1.1V

NO. PARAMETER UNIT

MIN MAX MIN MAX

For HPI Write, HRDY can go high (not

ready) for these HPI Write conditions;

otherwise, HRDY stays low (ready):

Case 1: Back-to-back HPIA writes (can

be either first or second half-word)

Case 2: HPIA write following a

PREFETCH command (can be either

first or second half-word)

Case 3: HPID write when FIFO is full or

flushing (can be either first or second

half-word)

Case 4: HPIA write and Write FIFO not

empty

For HPI Read, HRDY can go high (not

ready) for these HPI Read conditions:

Case 1: HPID read (with auto-

Delay time, HSTROBE low to

5 t

d(HSTBL-HRDYV)

15 17 ns

increment) and data not in Read FIFO

HRDY valid

(can only happen to first half-word of

HPID access)

Case 2: First half-word access of HPID

Read without auto-increment

For HPI Read, HRDY stays low (ready)

for these HPI Read conditions:

Case 1: HPID read with auto-increment

and data is already in Read FIFO

(applies to either half-word of HPID

access)

Case 2: HPID read without auto-

increment and data is already in Read

FIFO (always applies to second half-

word of HPID access)

Case 3: HPIC or HPIA read (applies to

either half-word access)

5a t

d(HASL-HRDYV)

Delay time, HAS low to HRDY valid 15 17 ns

6 t

en(HSTBL-HDLZ)

Enable time, HD driven from HSTROBE low 1.5 1.5 ns

7 t

d(HRDYL-HDV)

Delay time, HRDY low to HD valid 0 0 ns

8 t

oh(HSTBH-HDV)

Output hold time, HD valid after HSTROBE high 1.5 1.5 ns

14 t

dis(HSTBH-HDHZ)

Disable time, HD high-impedance from HSTROBE high 15 17 ns

For HPI Read. Applies to conditions

where data is already residing in

HPID/FIFO:

Case 1: HPIC or HPIA read

Delay time, HSTROBE low to

15 t

d(HSTBL-HDV)

Case 2: First half-word of HPID read 15 17 ns

HD valid

with auto-increment and data is already

in Read FIFO

Case 3: Second half-word of HPID

read with or without auto-increment

For HPI Write, HRDY can go high (not

ready) for these HPI Write conditions;

otherwise, HRDY stays low (ready):

Case 1: HPID write when Write FIFO is

Delay time, HSTROBE high to full (can happen to either half-word)

18 t

d(HSTBH-HRDYV)

15 17 ns

HRDY valid Case 2: HPIA write (can happen to

either half-word)

Case 3: HPID write without auto-

increment (only happens to second

half-word)

(1) M=SYSCLK2 period in ns.

(2) HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

(3) By design, whenever HCS is driven inactive (high), HPI will drive HRDY active (low).

212 Peripheral Information and Electrical Specifications Copyright © 2010–2014, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM1808

Loading...

Loading...