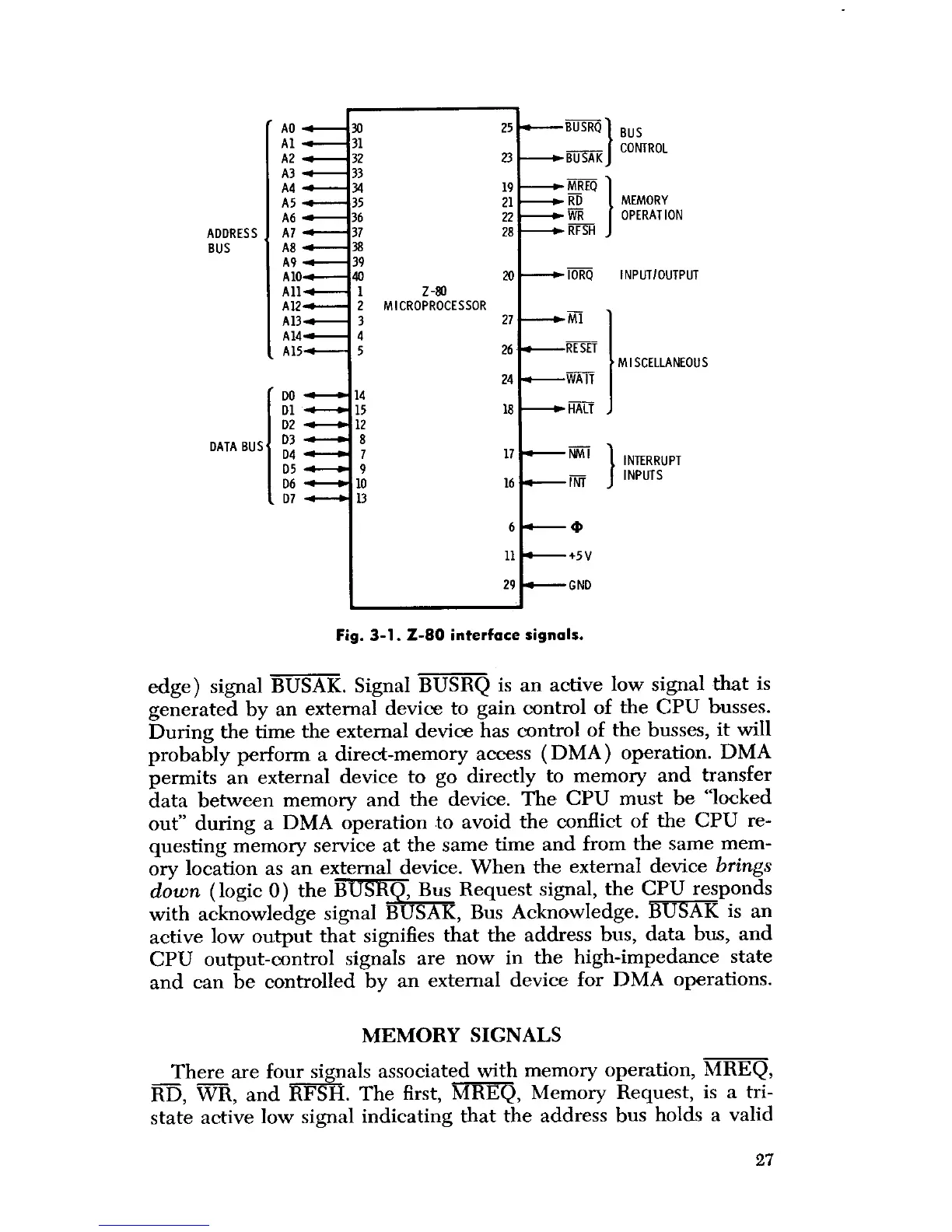

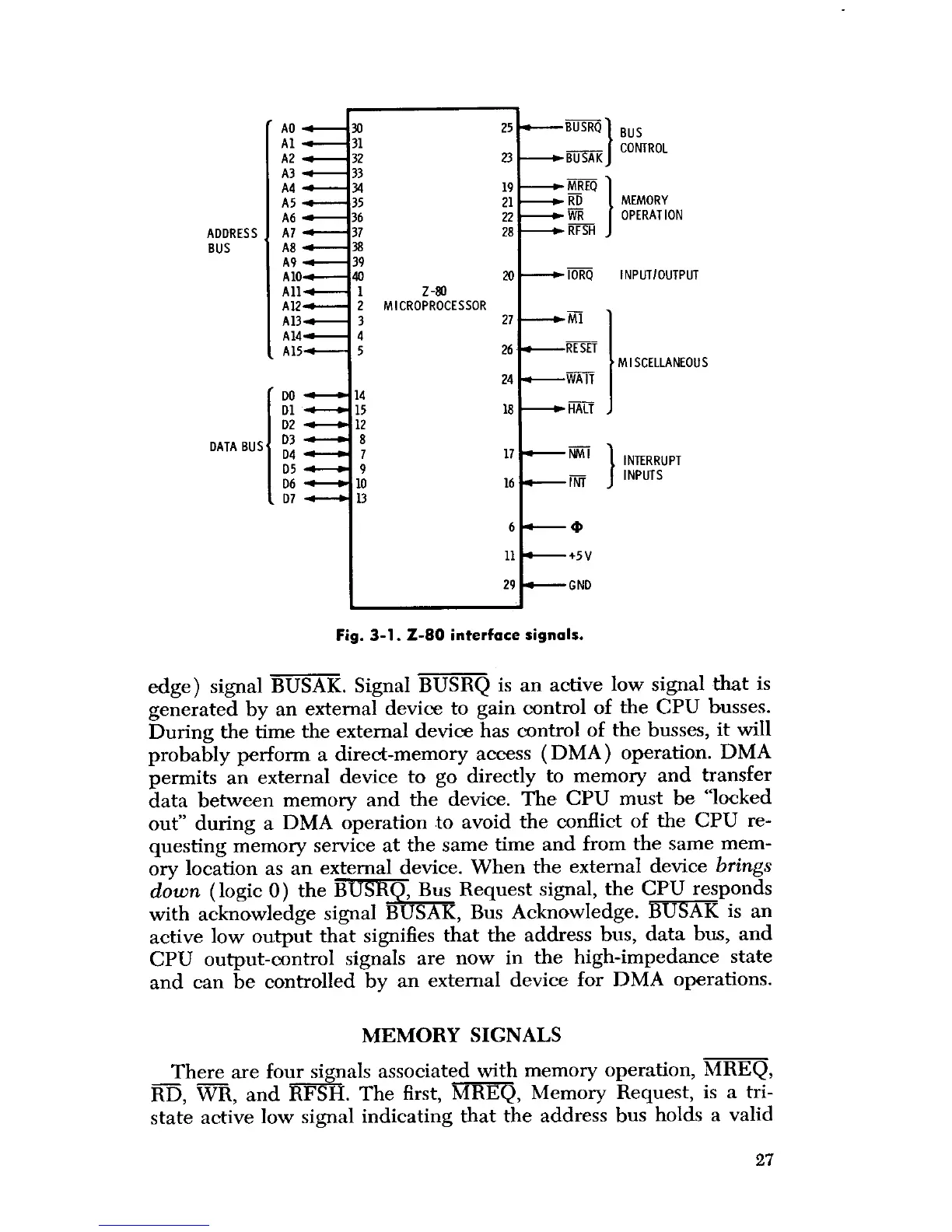

AO

Al

A2

A3

A4

AS

A6

ADDRESS A7

BUS AS

A9

A 10

All

A12

A13

A14

A15

D4

D5

D6

D7

30 25 BUSRQ I BUS

31 Jt CONTROL

32 23 BUAK

33

34 19 WHO 1

35 21 RD

1

MEMORY

36 22 WR OPERATION

37 28 RFSH

38

39

40 20

FUR INPUT/OUTPUT

1 Z-80

2 MICROPROCESSOR

3 27 Ml

4

5 26 RES

MISCELLANEOUS

24 WAIET

T

14

15 18 HALT J

12

8 _

7 17 NMI

1

INTERRUPT

9

10 16 IN-T

1

INPUTS

13

6

0

11 Fe -+5V

29 F+----GND

Fig. 3-1. Z-80 interface

signals.

edge) signal BUSAK. Signal BUSRQ is an active low signal that is

generated by an external device to gain control of the CPU busses.

During the time the external device has control of the busses, it will

probably perform a direct-memory access (DMA) operation. DMA

permits an external device to go directly to memory and transfer

data between memory and the device. The CPU must be "locked

out" during a DMA operation to avoid the conflict of the CPU re-

questing memory service at the same time and from the same mem-

ory location as an external device. When the external device

brings

down

(logic 0) the B-L77TFQ-, Bus

Bus Request signal, the CPU responds

with acknowledge signal BUSAK, Bus Acknowledge. J AK is an

active low output that signifies that the address bus, data bus, and

CPU output-control signals are now in the high-impedance state

and can be controlled by an external device for DMA operations.

MEMORY SIGNALS

There are four signals associated with memory operation, MREQ,

RD, WR, and RFSH. The first, MREQ, Memory Request, is a tri-

state active low signal indicating that the address bus holds a valid

27

Loading...

Loading...