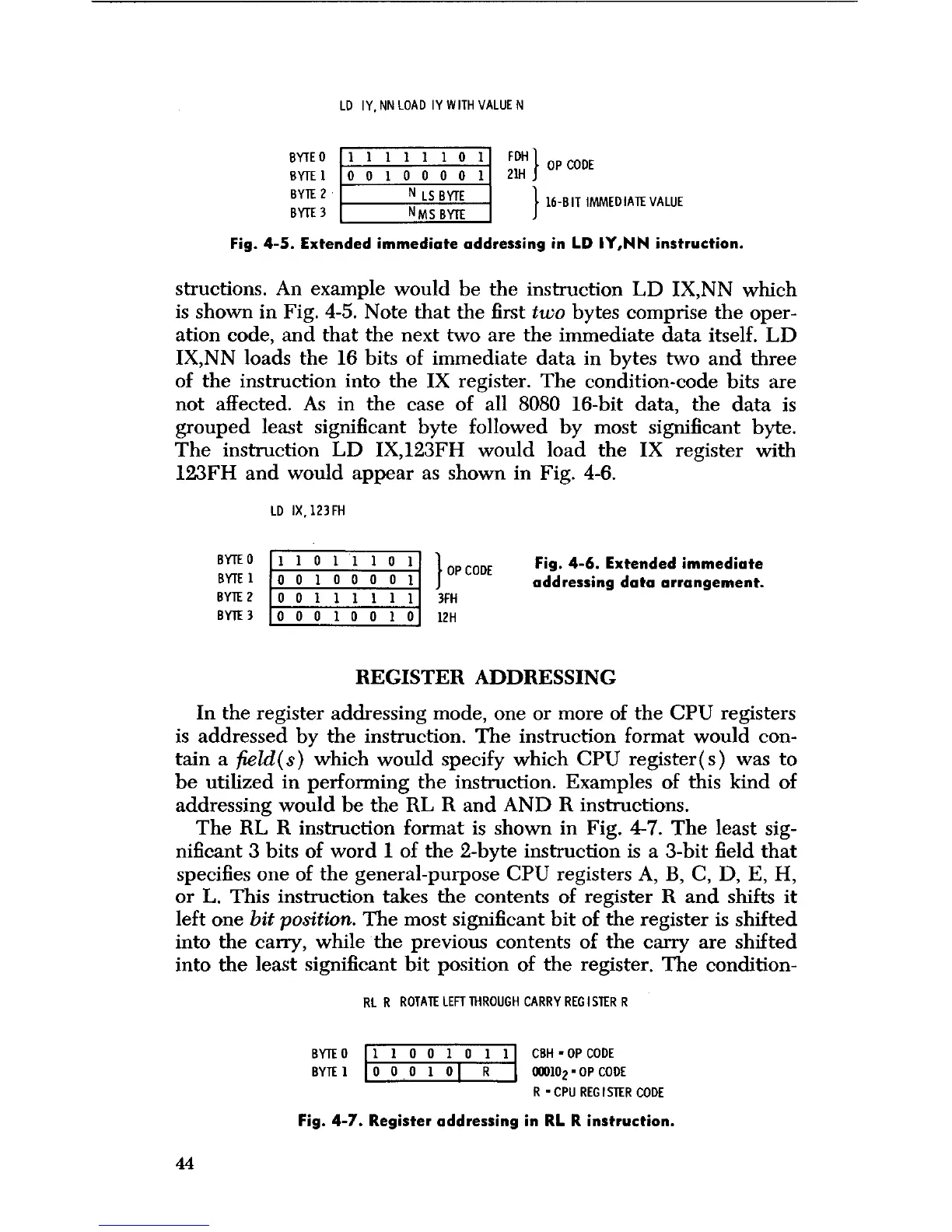

LD IY, NN LOAD IY WITH VALUE N

N LS BYTE

BYTE 2 16-BIT IMMEDIATE VALUE

BYTE 3 1

N MS BYTE }

1 1 1 1 1 1 0 1

BYTE

0 FDH

1 OP CODE

BYTE 1 21H J

0 0 1 0 0 0 0 1

Fig. 4-5. Extended

immediate addressing

in LD IY,NN instruction.

structions. An example would be the instruction LD IX,NN which

is shown in Fig. 4-5. Note that the first

two

bytes comprise the oper-

ation code, and that the next two are the immediate data itself. LD

IX,NN loads the 16 bits of immediate data in bytes two and three

of the instruction into the IX register. The condition-code bits are

not affected. As in the case of all 8080 16-bit data, the data is

grouped least significant byte followed by most significant byte.

The instruction LD IX,123FH would load the IX register with

123FH and would appear as shown in Fig. 4-6.

LD IX,123FH

BYTE 0

BYTE 1

BYTE 2

BYTE 3

1 1 0 1 1 1 0 1

0 0 1

0 0

0 0 1

0 0 1

1 1

1 1 1

0 0 0

1 0

0 1 0

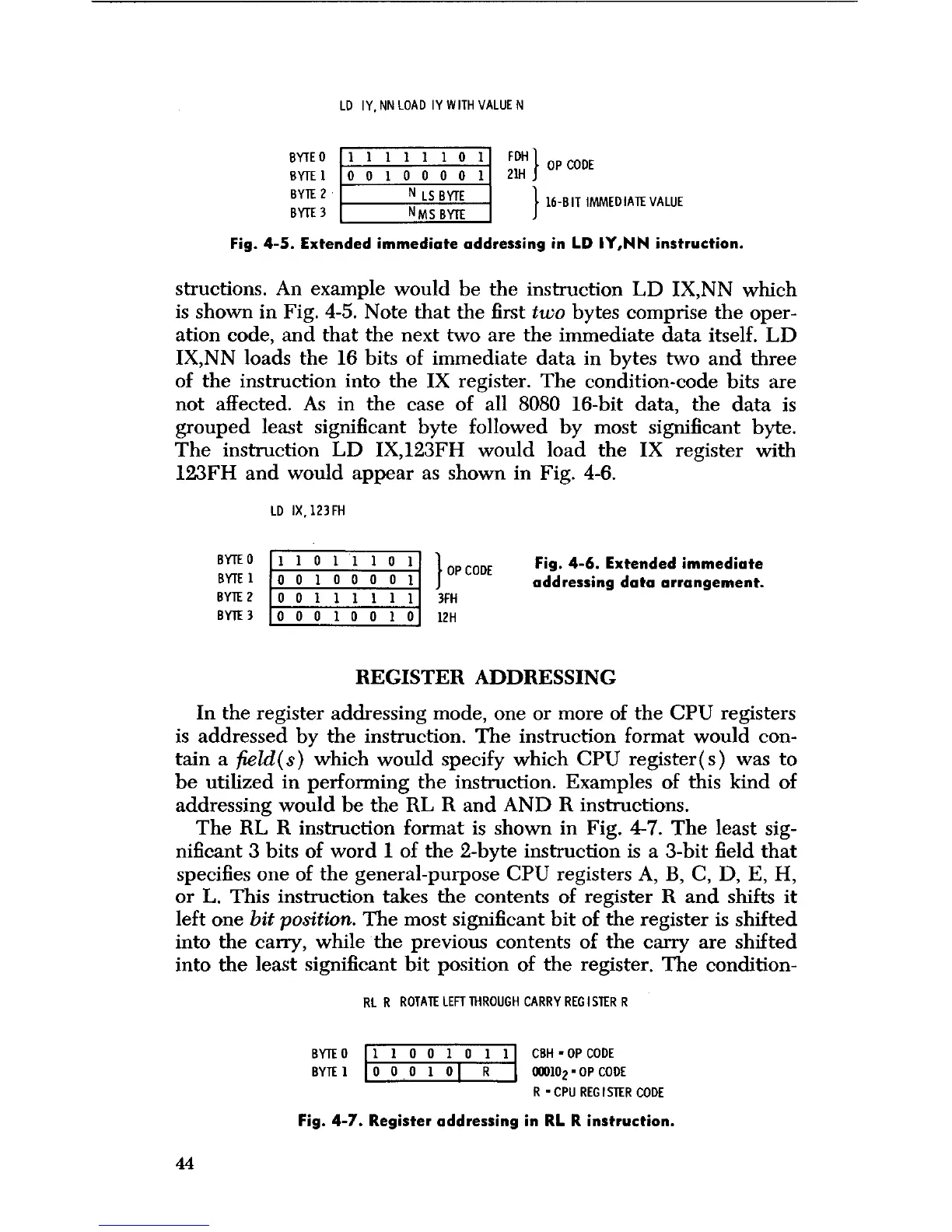

In the register addressing mode, one or more of the CPU registers

is addressed by the

instruction

. The instruction format would con-

tain

a field (s)

which would specify which CPU register

(s) was to

be utilized in performing the instruction. Examples of this kind of

addressing would be the RL R and AND R instructions.

The RL R instruction format is shown in Fig. 4-7. The

least sig-

nificant 3 bits of word 1 of the 2-byte instruction is a 3-bit field that

specifies one of the general-purpose CPU registers A, B, C, D, E, H,

or L. This instruction takes the contents of register R and shifts it

left one

bit

position

.

The most

significant

bit of the

register

is shifted

into the carry, while the previous contents of the carry are shifted

into the

least significant

bit position of the register. The condition-

RL R ROTATE

LEFT

THROUGH CARRY REGISTER R

BYTE 0

BYTE 1

} OP CODE

3FH

12H

Fig. 4-6. Extended

immediate

addressing data arrangement.

REGISTER ADDRESSING

1 1 0 0 1 0 1 1

1

0 0 0 1 0 R

CBH - OP CODE

000102.OP CODE

R - CPU REGISTER CODE

Fig. 4-7.

Register addressing

in RL R

instruction.

44

Loading...

Loading...