18 PowerLab Owner’s Guide

digital converter). The ADC can sample at a maximum rate of 100,000

samples per second. The sampling process is handled independently

of the processor core through a sampling control engine using direct

memory access. The CPU assembles groups of samples into blocks

and then transmits them to the computer, where the software

receives, records, and displays the data.

The external trigger input (marked ‘Trigger’ on the front panel)

allows either a voltage level or a contact closure to trigger recording.

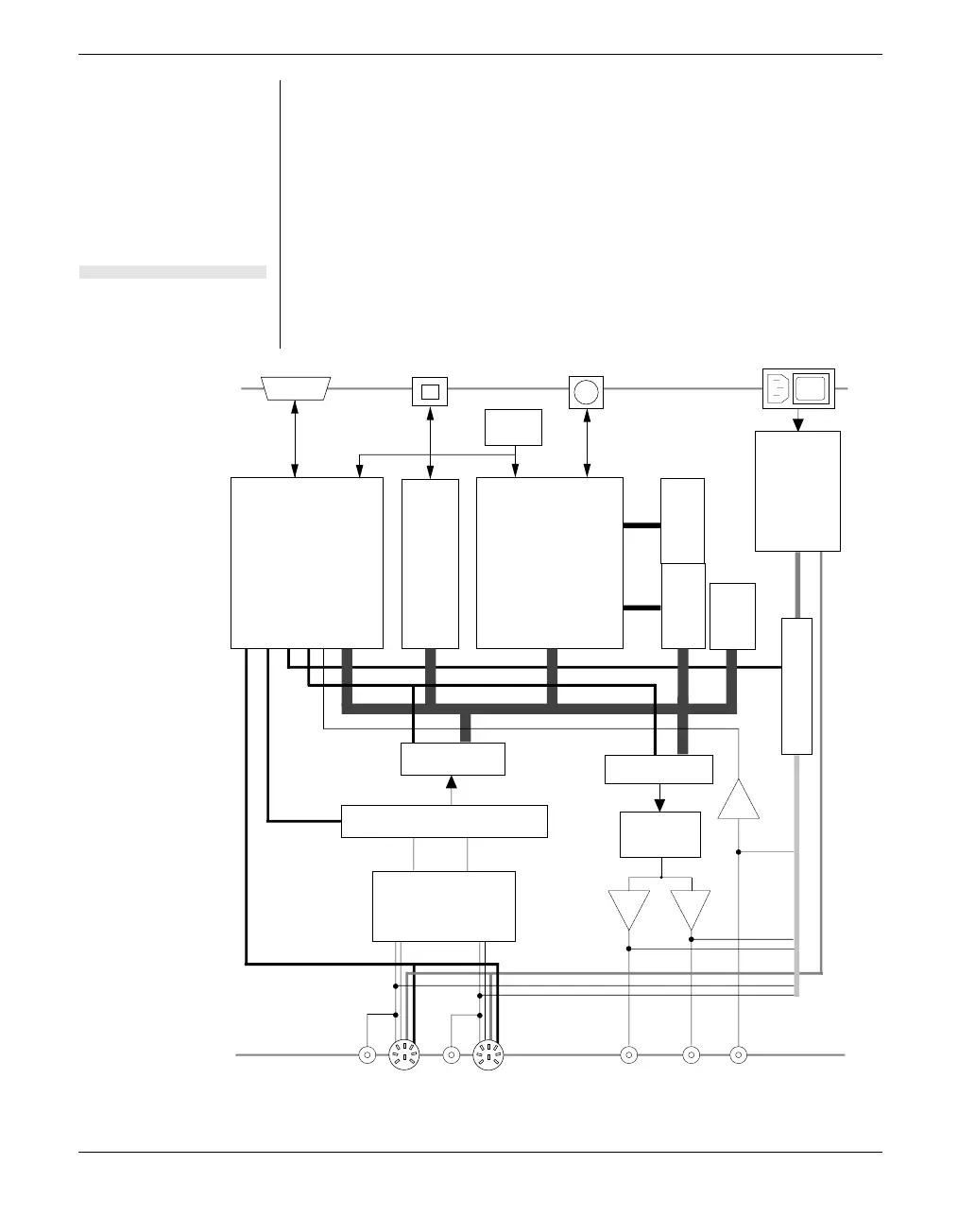

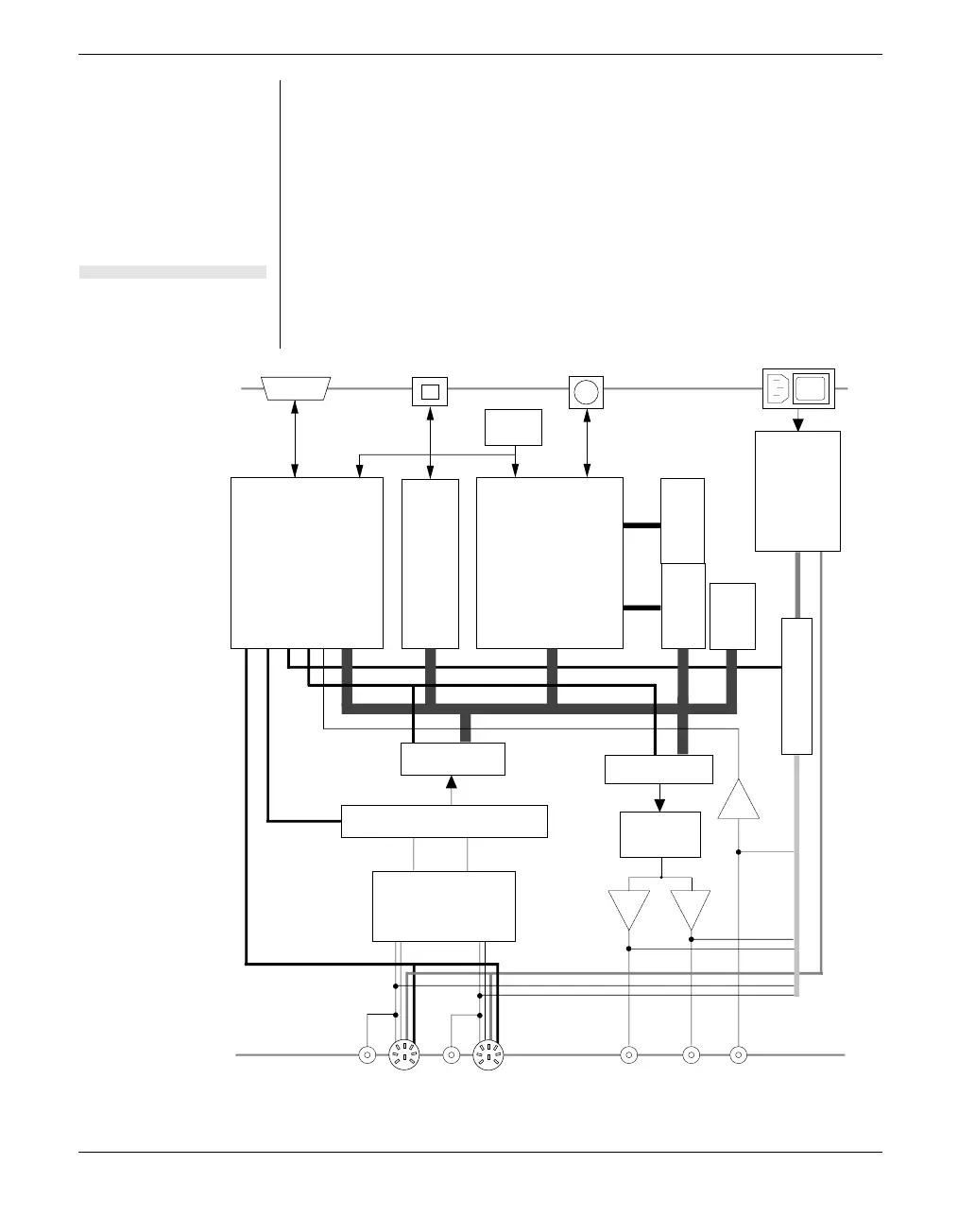

Figure A–1

Block diagram of the

PowerLab 2/20.

PPC403 CPU

16-bit ADC

16-bit DAC

RAN GE

C ON TROL

Switching

Power

Supply

IEC Mains

Input

USB Port

Co mpar at o r

FLASH ROM

1M x 16 DRAM

System

Glue

Chip

+1 –1

2 Differential Input

Am plif iers

MultiPort

POD I C

±5 V

USB C ont roller

1M x 16 DRAM

30 MH z

XTAL

Serial PortI C Port

MULTIPLEXER

2

2

REAR

PANEL

FRONT

PANEL

Analog Inputs Analog Output

External Trigger InputInput 1 Input 2 + –

Loading...

Loading...