364

02

/3AL 91669 AA AA

674

674

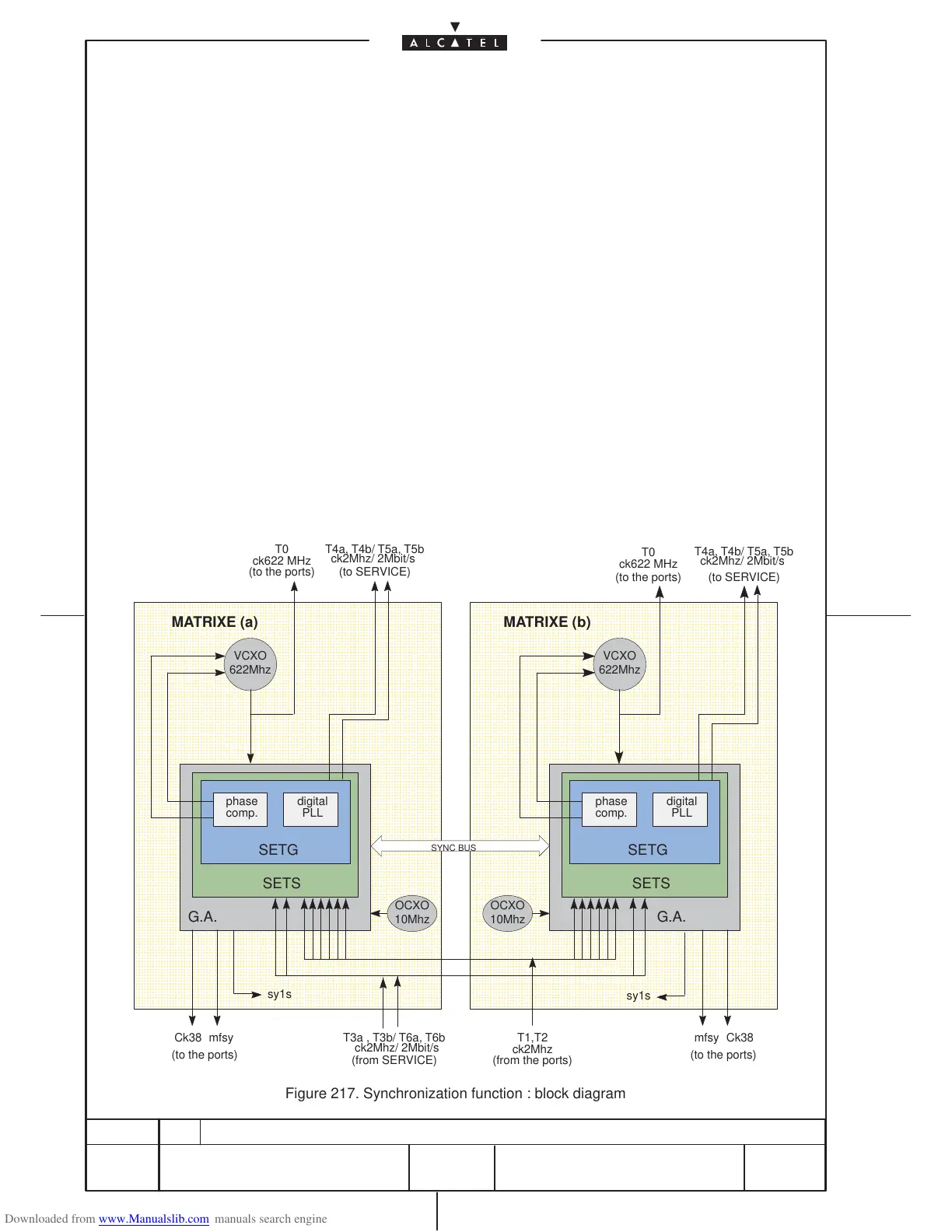

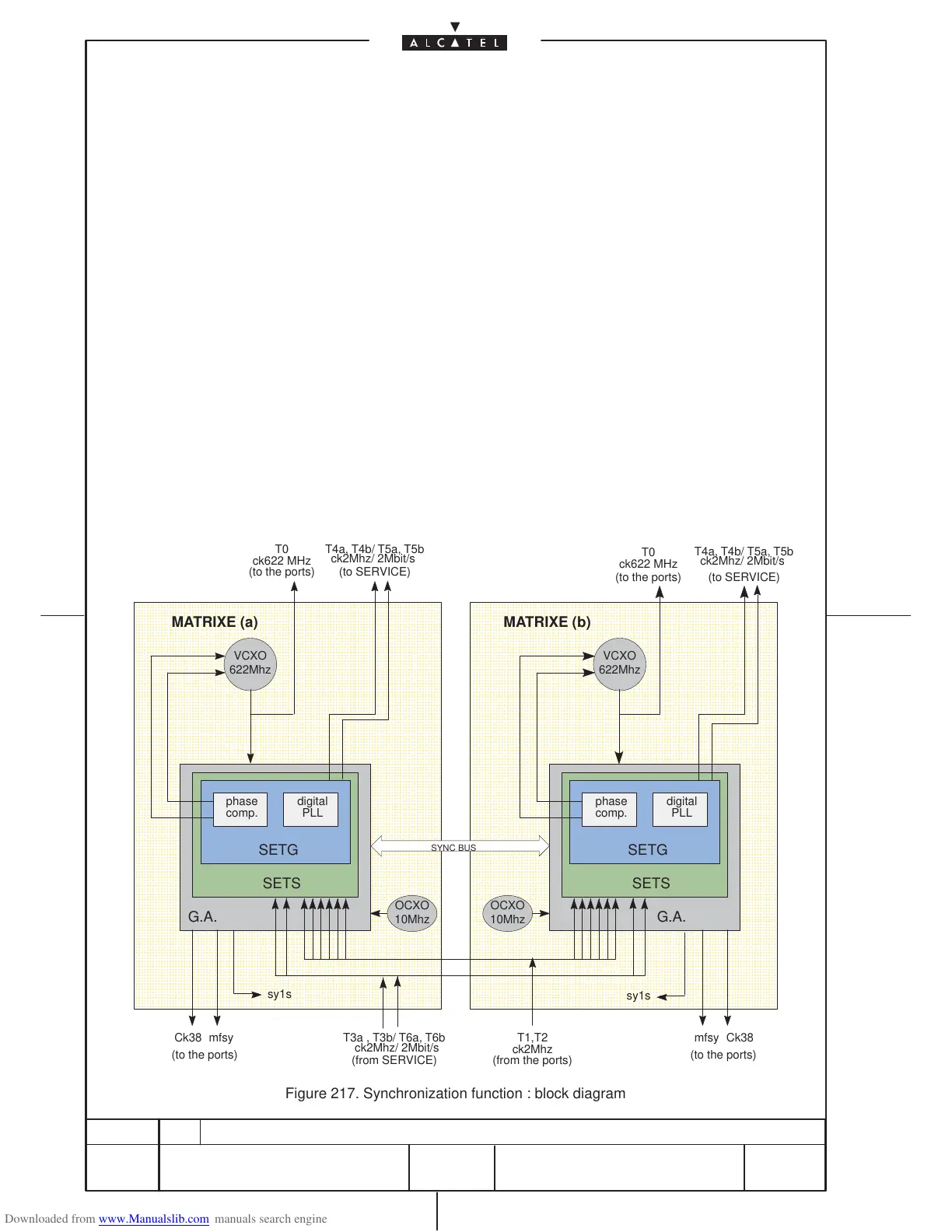

• T4 or T5: the first is a synchronizing clock at 2.048 Mhz , the second is a 2 Mbit/s synchronizing

signal ; the selection between the two signals is made via software and the result is sent towards

the external. T4 or T5 is obtained from a digital PLL that can be locked to any of the T1/T2

references and can be squelched. This clock is sent to the SERVICE card that inserts the SSM

algorithm and generates the clock standard format to be output from the system.

The T4/T5 clocks are two (i.e. T4a, T4b or T5a, T5b).

The ”don’t use” criteria is sent to the ”NEi clock” which had supplied the synch. reference to obtain the

T0. This operation is carry out to prevent the ”timing reference” synchronizing the supplier NEi (timing

loop).

Other synchronizing signals generated by the MATRIXE

The MATRIXE generates the following synchronisms for internal use :

• CK38Mhz : it is derived from the system clock and it is distributed to the ports and to the

SERVICE and EQUICOE cards. Its frequence is 38 MHz

• MFSY : it is the multiframe synchronism at 500 Hz, obtained from the ck 38MHz. It is distributed

to all the ports and to SERVICE and PQ2/EQC cards.

• SY1S : it is a one second synchronism used on the MATRIXE for the Performance Monitoring

calculation.

As the MATRIXE is redundant, the synchronization function is redundant as well. The synchronization

system guarantees the Hitless switch because the two MATRIXE works in a Master–Slave mode. In order

to maintain locked and in phase the two G.A. some signal are exchange on the SYNC BUS.

Loading...

Loading...