APx PDM I/O Module for B Series: Specifications 79

PDM

Logic Level 2.0 V

t

CO

Clock to out 15 ns

t

R

Rise Time 3.9 ns

t

F

Fall Time 2.9 ns

r

OUT

Output Impedance 40 ohms

f

CLK

max

Maximum Clock Frequency 24.576 MHz

PDM RECEIVER

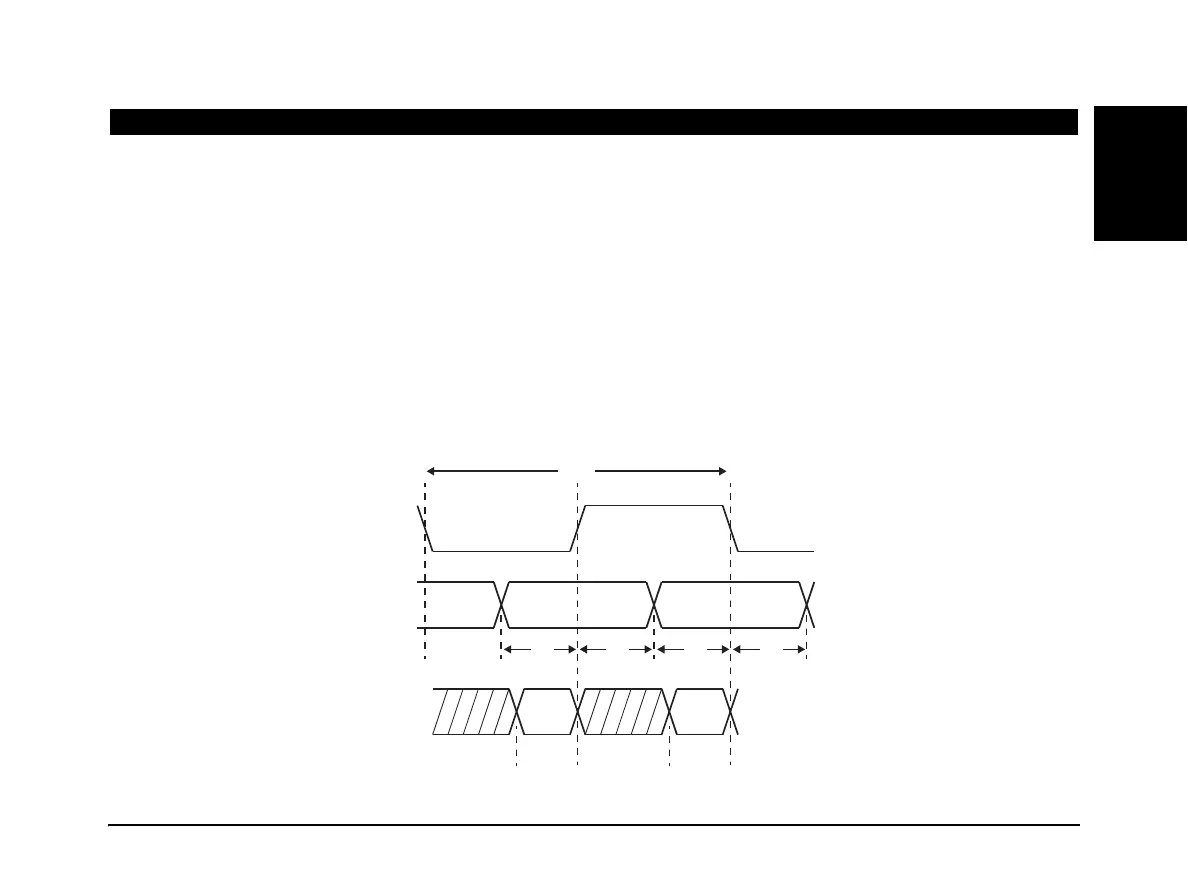

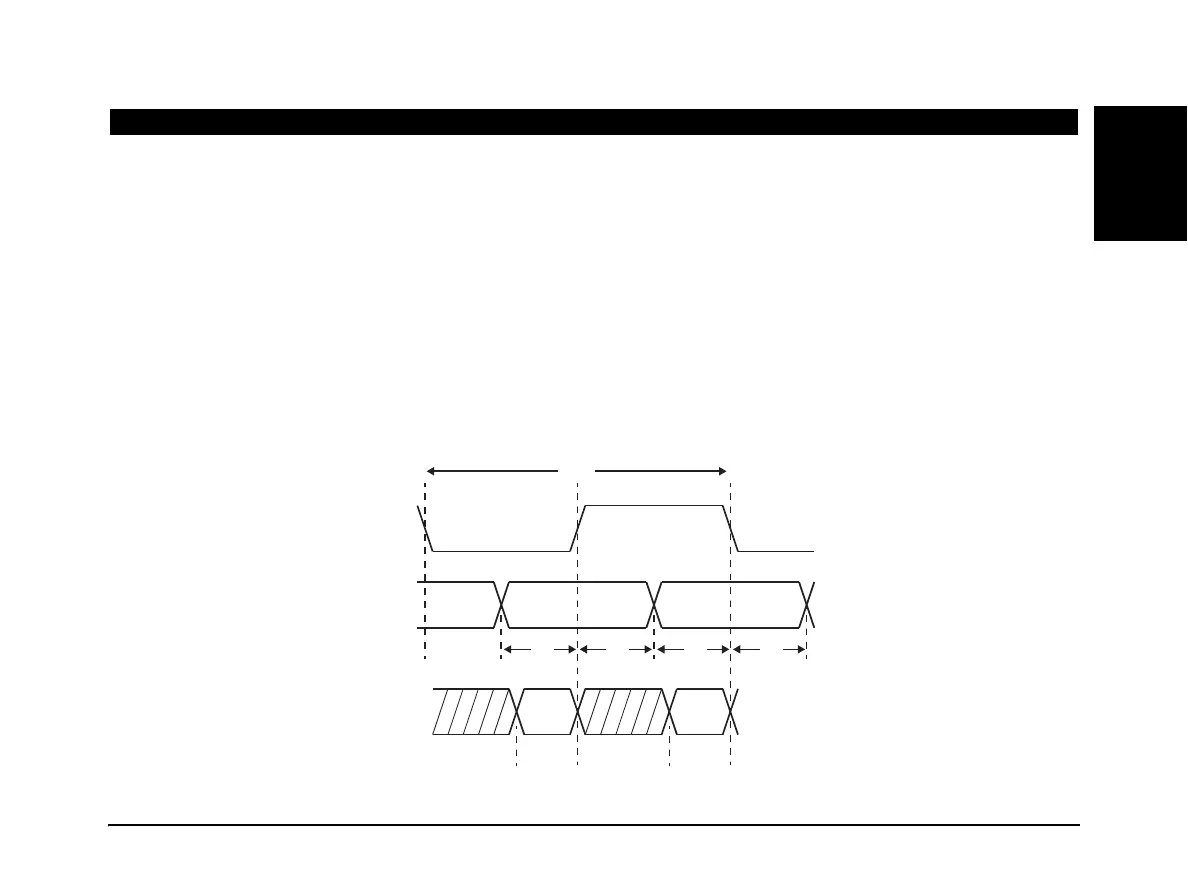

t

CLKRX

Clock period (master or slave

mode)

41 7813 ns

t

HP

Data hold time, rising edge 5 ns

t

HN

Data hold time, falling edge 5 ns

t

SU

Data setup time 5 ns

Parameter Symbol Test Conditions Min Typ Max Unit

t

SU

t

SU

t

HP

t

SU

t

HN

t

CLK

t

H

t

H

t

SU

BITCLK

DATA TX CH 1

CH 1

CH 2

CH 2

DATA RX

Loading...

Loading...