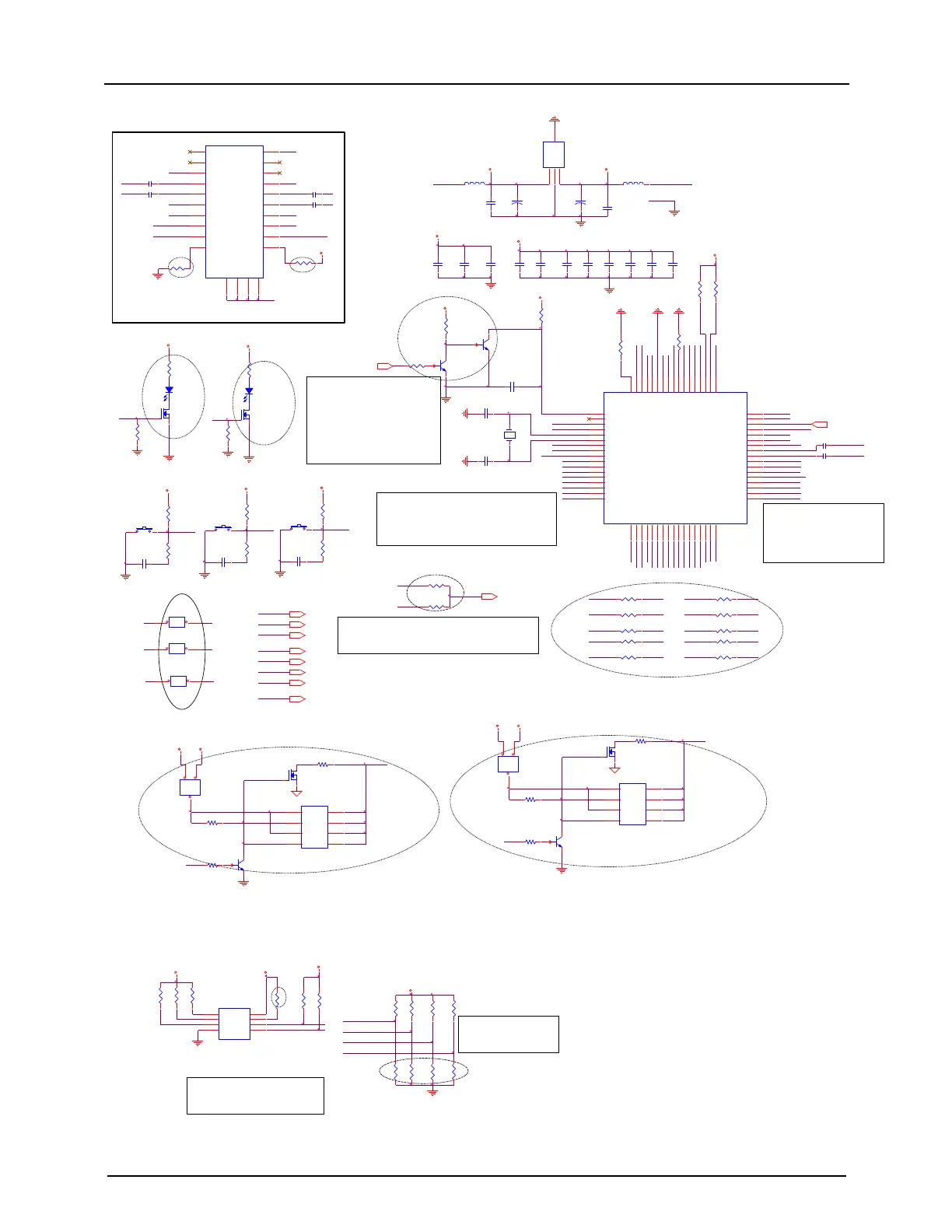

JP10

HEADER 1x2

1 2

SPC0 SPC1

SPD0

JP11

HEADER 1x2

1 2

SPD1

GLED

VCC18

JP12

HEADER 1x2

1 2

D1

P504CT-ND

ENAVDDIRQ

R16

100

Q3

BSS138CT-ND

1

32

D2

P504CT-ND

R17

100

Must be reserved, Ju mper canbe

replace with 0 oh m r esisitor

+3.3V

+3.3V

Q4

BSS138CT-ND

1

32

DP0N

R15

1k

R48

100

A2M A2P

GPIO[2]GPIO[2]

HPDET

GND

C3 0.1uF

U4

CH9904(SOIC-8 package)

GP2

2

GP3

3

GND

4

SPD

5

SPC

6

WE

7

VCC

8

GP1

1

C24

22pF

GND

R36

6.8k

Q6

MMBT3904

1

2 3

U5

SI4953

S1

1

G1

2

S2

3

G2

4

D2

5

D2

6

D1

7

D1

8

C1 0.1uF

Q5

H2N7002

1

32

R37

470

R3

10K

SW2

SPD0

U7

SI4953

S1

1

G1

2

S2

3

G2

4

D2

5

D2

6

D1

7

D1

8

+3.3V

SPD0

BLDN

Y1

27MHz

DP0P

R8 50

R14

100K

Q8

MMBT3904

1

2 3

R50

10k

R56

470

C4 0.1uF

R13

10K(1%)

R38

6.8k

U2

DP_sink

ML_Lane3n

1

GND

2

ML_Lane3p

3

ML_Lane2n

4

GND

5

ML_Lane2p

6

ML_Lane1n

7

GND

8

ML_Lane1p

9

ML_Lane0n

10

GND

11

ML_Lane0p

12

GND

13

GND

14

AUX_CHp

15

GND

16

AUX_CHn

17

HPDET

18

RTN_DPPWR

19

DPPWR

20

GND

22

GND

23

GND

24

GND

25

C23

0.1uF

Q7

H2N7002

1

32

A7M

A7P

GND

R51

100

U3

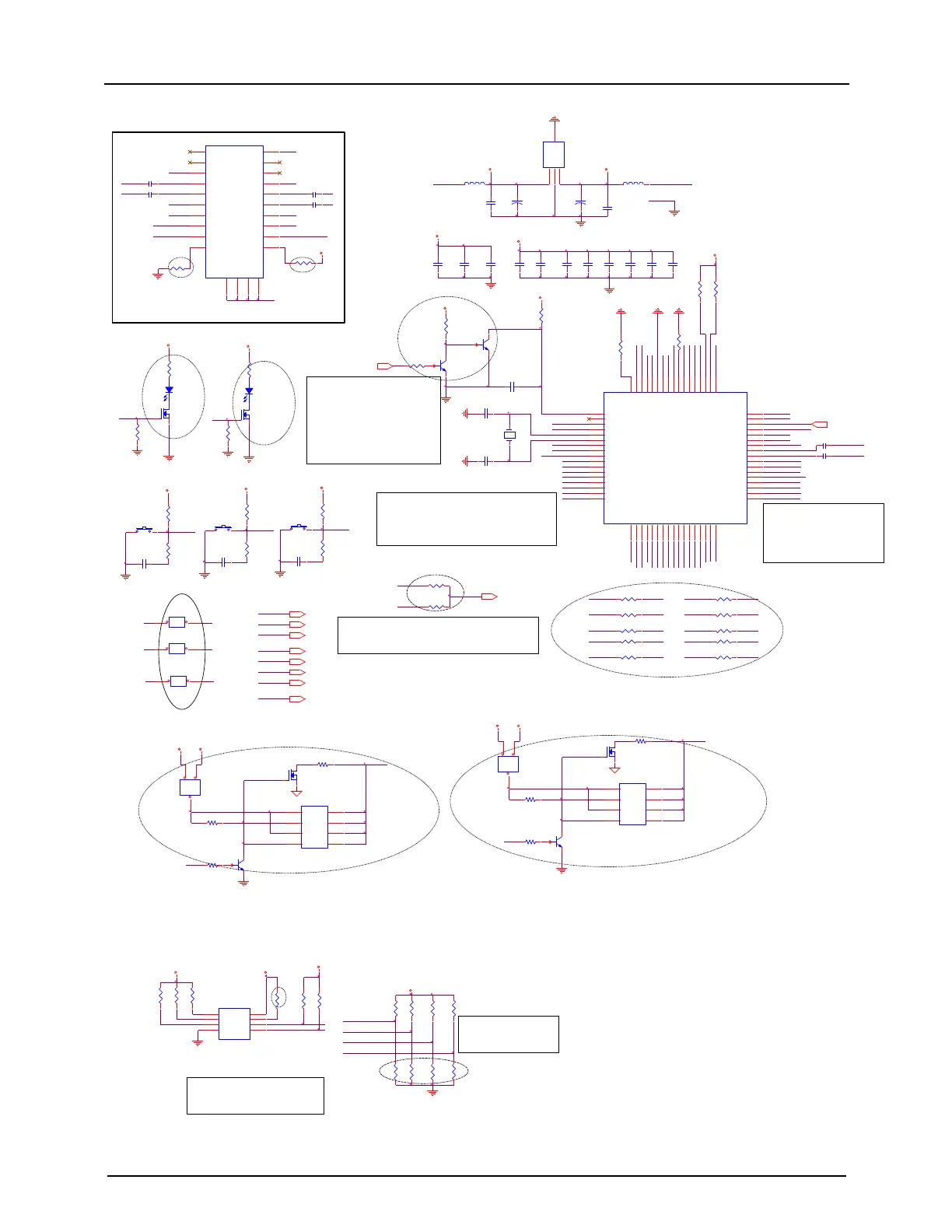

CH7511B

RESETB

1

Reserved

2

AVDD

3

AVDD

4

XO

5

XI

6

DVDD

7

GND

8

REFCK

9

LL2CP

10

LL2CN

11

LDC7P

12

LDC7N

13

LDC6P

14

LDC6N

15

LDC5P

16

LDC5N

17

LVDD

18

LDC4P

19

LDC4N

20

GND

21

LDC3P

22

LDC3N

23

LL1CP

24

LL1CN

25

LDC2P

26

LDC2N

27

LDC1P

28

LDC1N

29

LDC0P

30

LDC0N

31

LVDD

32

GPIO[0]

33

GPIO[1]

34

SPC1

51

SPD1

50

PWM_IN

49

PWM_OUT0

48

ENAVDD

47

ENABKL

46

GND

45

AUXP

44

AUXN

43

DVDD

42

PWRDN

41

GND

40

PWM_OUT1

39

GPIO[3]

38

GPIO[2]

37

IRQ

36

GND

35

RBIAS

68

AVDD

67

AVDD

66

DP1N

65

DP1P

64

GND

63

DP0N

62

DP0P

61

AVDD

60

HPDET

59

OLED

58

GLED

57

BLUP

56

BLDN

55

SPC0

54

SPD0

53

LVDD

52

VCC33

CLK1M CLK1P

R39

50k

GPIO[3]

JP1

HEADER 3

1

2

3

R58

10k

R10

6.8k

R7

10K

GPIO[3]GPIO[3]

R9

6.8k

R57

50k

R11

10K

C26

22pF

C2 0.1uF

R35

1.8k

JP2

HEADER 3

1

2

3

+3.3V

+3.3V

+3.3V

VCC18

+5V+3.3V

+3.3V

SPC1

+5V+3.3V

GPIO[2]A6M

A6P

A5M

A5P

C14

0.1uF

R1

10K

+3.3V

SW3

+3.3V

PWRDN

A4P

R23

10k

OLEDOLED

SPD0

IRQ

IRQ

A4M

PWM_OUT0

R28

0

PWM_OUT

R29 0

PWM_OUT

NO TE : P W M_O UT0 (0~ 100 % d uty cy cl e or PW M b ypa ss

mo de )

P W M_O UT1 (30 ~10 0% dut y c yc l e)

PWM_OUT1

PWM_OUT0

Solder option

R22

10k

GLEDGLEDGLEDGLEDGLEDGLED

SPD0

C5

0.1uF

+3.3V

A3P

L1

Bead

GND

C7

10uF

+1.8V

U1

IRU1206-18

Vout

3

Gnd

2

Vin

1

pin

4

C8

0.1uF

NO TE : C u sto mer ca n c hoo se

di ff e r e n t p ane l b y p ull

hi gh o r low of GP IO[ 0:3 ].

L2

Bead

C6

10uF

R32

6.8k

VCC18

A3M

GND

NO TE : C u sto mer is be tte r t o l in k

sp c0 a n d sp d0 to SMB US/ IIC to

up da t e t he Boo t R OM lat er

CLK1M

CLK1P

AUXP

AUXN

GND

GND

GND

GND

GND

HPDETHPDET

GND

GND

GNDGNDGNDGNDGNDGND

DPPWR

GNDGNDGND

GPIO[0]

GPIO[0]

R27

100

A2M

A2P

RESETB_PCH

R26

100

PWM_OUT1

C19

0.1uF

C12

0.1uF

C16

0.1uF

Backlight

C13

0.1uF

C15

0.1uF

VCC18

ENABKL

VCC33

C18

0.1uF

VCC33

A1M

A1P

Note: The resetb is 1.8V

level.

It need 10Kohm r esi ster to

1.8V

and 0.1uf capaci tor to GND.

So if the system res et signal

is 3.3V,

the level shift c irc uit is

necessary.

BLUP

R20

10K

DP1N

A0M

A0P

R21

10K

NOTE:

1. The dotted line parts are option funtion circuits.

2. The voltage circuit can only support CH7511B chip

to work.If supporting the panel voltage, please add the

other circuit.

3. Whether to use PWM_IN(3.3V), PWM_OUT0(3.3V)

and PWM_OUT1(3.3V) is determined by customers.

Which is used for Panel luminance adjustment.

4. DP and LVDS diffential pairs should be as short as

possible. Please see appliciton note for detial layout guide

5. The CH7511B thermal exposed pad must be linked to

GND

GPIO[0]

DP1P

SPD1

VCC33

VCC PanelDriver

ENAVDD

CH7511B Boot Room

GND

A3M

R53

100

A3P

C17

0.1uF

GPIO[1]

GPIO[1]

BLUP

C20

0.1uF

R12

10K

R18

10K

C10

0.1uF

R5

10K

VCC18

VCC33

R19

10K

IRQ

C21

0.1uF

GPIO[1]

GPIO[2]

GPIO[2]

NO TE : I f th e s ouc e o f A UX has

0. 1u F c a p, ple ase do n't ad d

ca p i n C H75 11 por t. For AU X C H

Ci rc u i t , Pl eas e r efe r t o A N

an d D P S pec

NOTE: CH7511B supports two kinds of clock input ways

Option1: use 27MHz crystal with 22pf capacitors

Option 2: inject clock 27MHz (3.3V) in REFCK pin(Pin 9)

Customer must choose one option f or CH7511 clock

DP0P

R2

10K

BLUPBLUPBLUP

SW1

C9

0.1uF

A0M

DP0N

C22

0.1uF

PWM_IN

A6M

OLED

R49

100

GPIO[3]

GPIO[3]

A6P

A7M

R52

100

CLK2M

A7P

CLK2P

R54

100

A4M

R41

100

A5M

A4P

R43

100

A5P

R40

100

Q2

PMBS3904

1

2 3

BLDN

R34

6.8k

R33

6.8k

+3.3V

DP1N

DP1P

VCC33

R24

100

ENAVDD

REFCKREFCK

SPC1

ENABKL

SPC0

C11

0.1uF

R6

10K

GLED

SPD1

Power

Supply

GND

PWRDN

RESETB

GPIO[0]GPIO[0]

VCC18

R4

10K

Q1

PMBS3904

1

2 3

HPDET

+3.3V

R25

100

SPC0

VCC18VCC18

Panel Voltage and backlight control circuit

DP Interface

AUXP

C25 0.1uF

C27 0.1uF

AUXN

VCC18

VCC18

A0P

VCC18

CLK2P

GPIO[1]GPIO[1]

HPDET

A1M

R42

100

A1P

SPC0

SPC0

CLK2M

Loading...

Loading...