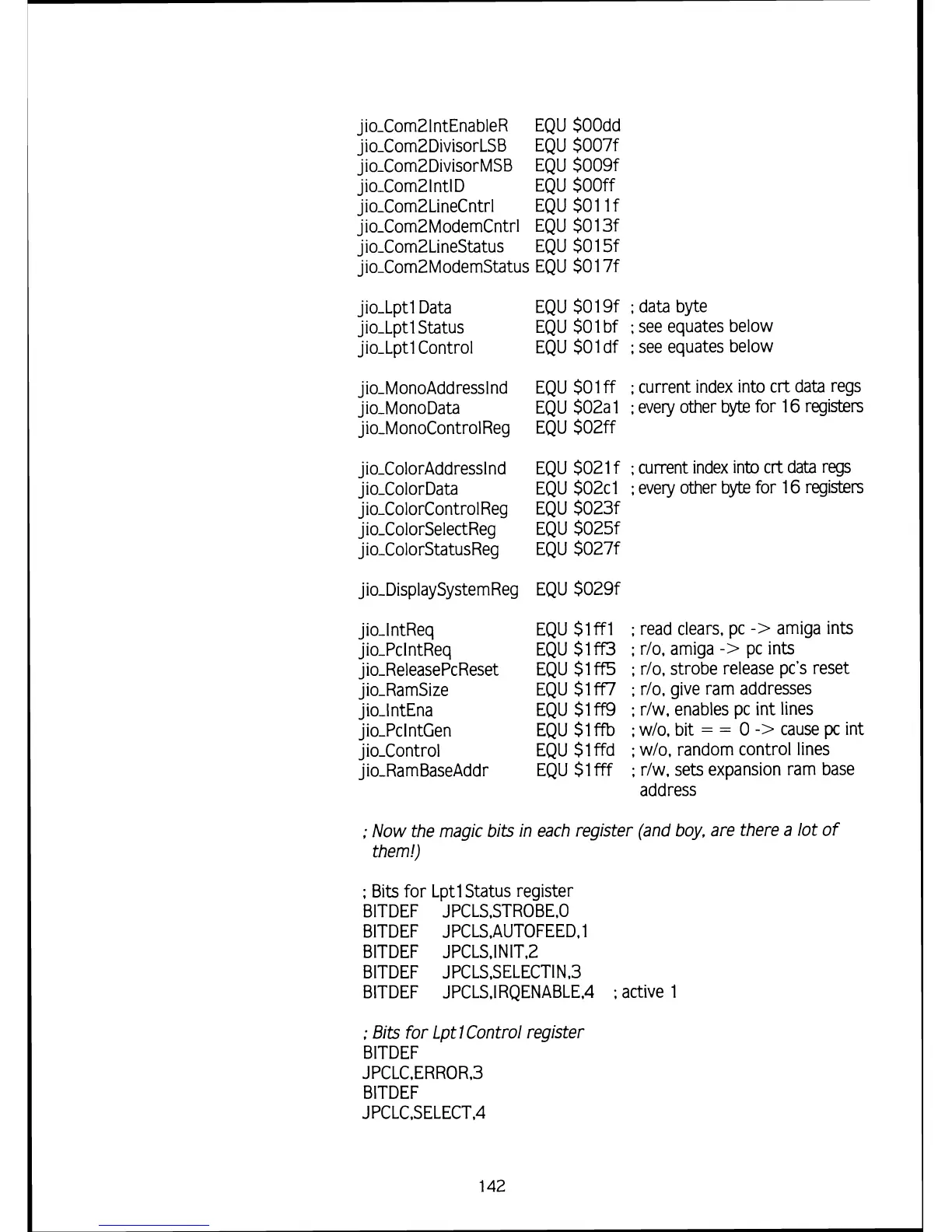

jio-Com2lntEnableR

EQU

SOOdd

jio-Com2DivisorLSB

EQU

$007f

jio-CornZDivisorMSB EQU S009f

jio-Com2lntlD EQU $OOff

jio-ComZLineCntrl

EQU

$01 l

f

jio-ComZModemCntrl EQU $01 3f

jio-CornZLineStatus EQU $01 5f

jio-ComZModemStatus EQU $01

7f

jio-Lptl Data

EQU $0 1

9f

;

data byte

jio-Lptl Status

EQU

$01 bf

;

see equates below

jio-Lptl Control

EQU

$01 df

;

see equates below

jio-MonoAddresslnd EQU $Olff

;

current index into crt data regs

jio-MonoData

EQU $02a 1

;

every other byte for 16 registers

jio-MonoControlReg EQU $02ff

jio-ColorAddresslnd

EQU $021

f

;

current index into crt data regs

jio-ColorData

EQU $02~ l

;

every other byte for

1

6

register;

jio-ColorControlReg

EQU

S023f

jio-ColorSelectReg EQU S025f

jio-ColorStatusReg

EQU

S027f

jio-DisplaySystemReg EQU $029f

EQU $lffl

;

read clears, pc

->

amiga ints

EQU

$lff3

;

rlo, amiga

->

pc ints

EQU

$1

ff!5

;

rlo, strobe release pc's reset

EQU

$1

ff7

;

rlo, give ram addresses

EQU

$lff9

;

rlw, enables pc int lines

EQU

$1

ffb

;

wlo, bit

=

=

0

->

cause

pc

int

EQU

$1 ffd

;

wlo, random control lines

EQU

$1 fff

;

rlw, sets expansion ram base

address

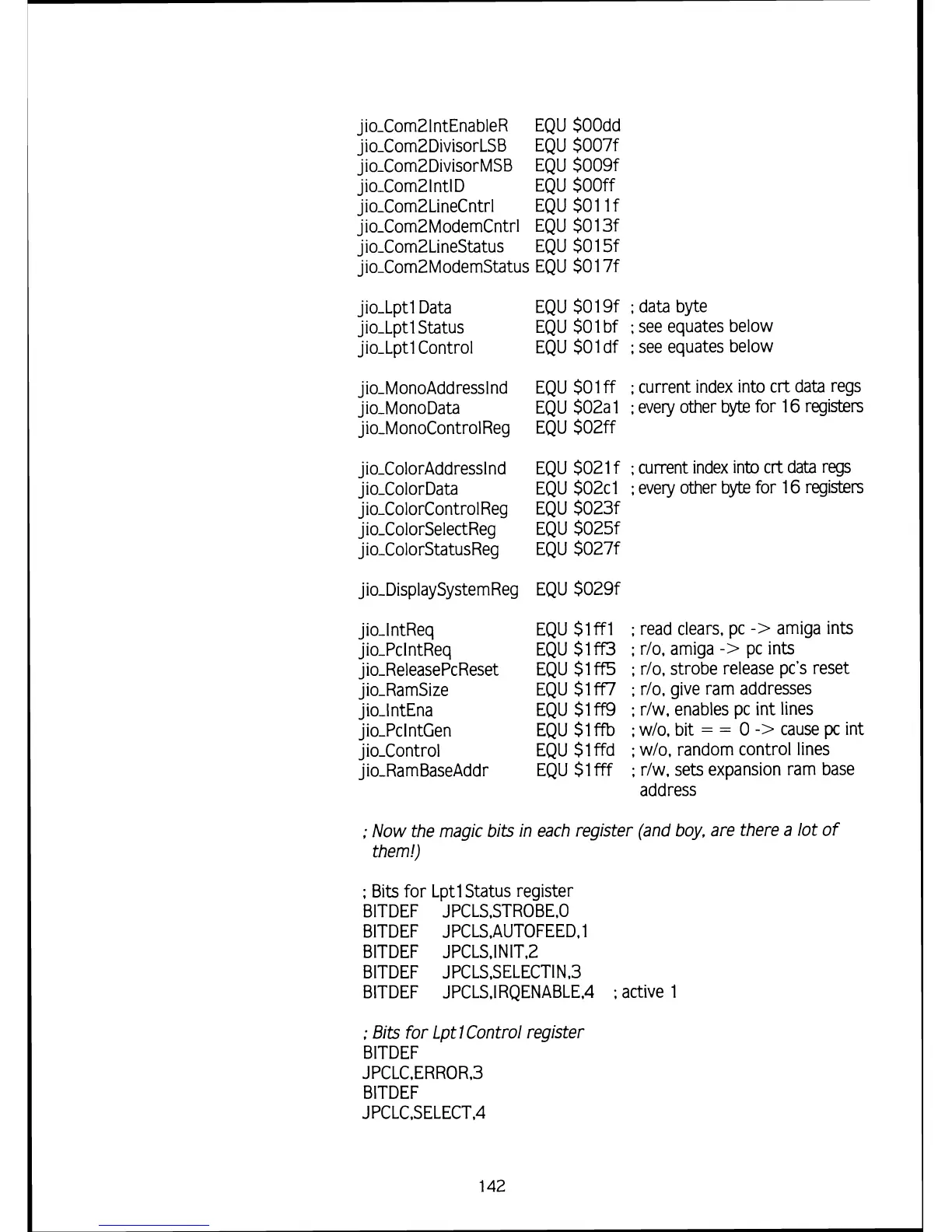

;

Now the magic bits in each register (and boy, are there a lot of

them!)

;

Bits for Lptl Status register

BITDEF

JPCLS,STROBE,O

BITDEF JPCLS,AUTOFEED,l

BITDEF JPCLS,INIT.2

BITDEF JPCLS.SELECTIN.3

BITDEF

JPCLSJRQENABLEA

;

active 1

;

Bits for Lpt

1

Control register

BITDEF

JPCLC,ERROR,3

BITDEF

JPCLC,SELECTA

Loading...

Loading...