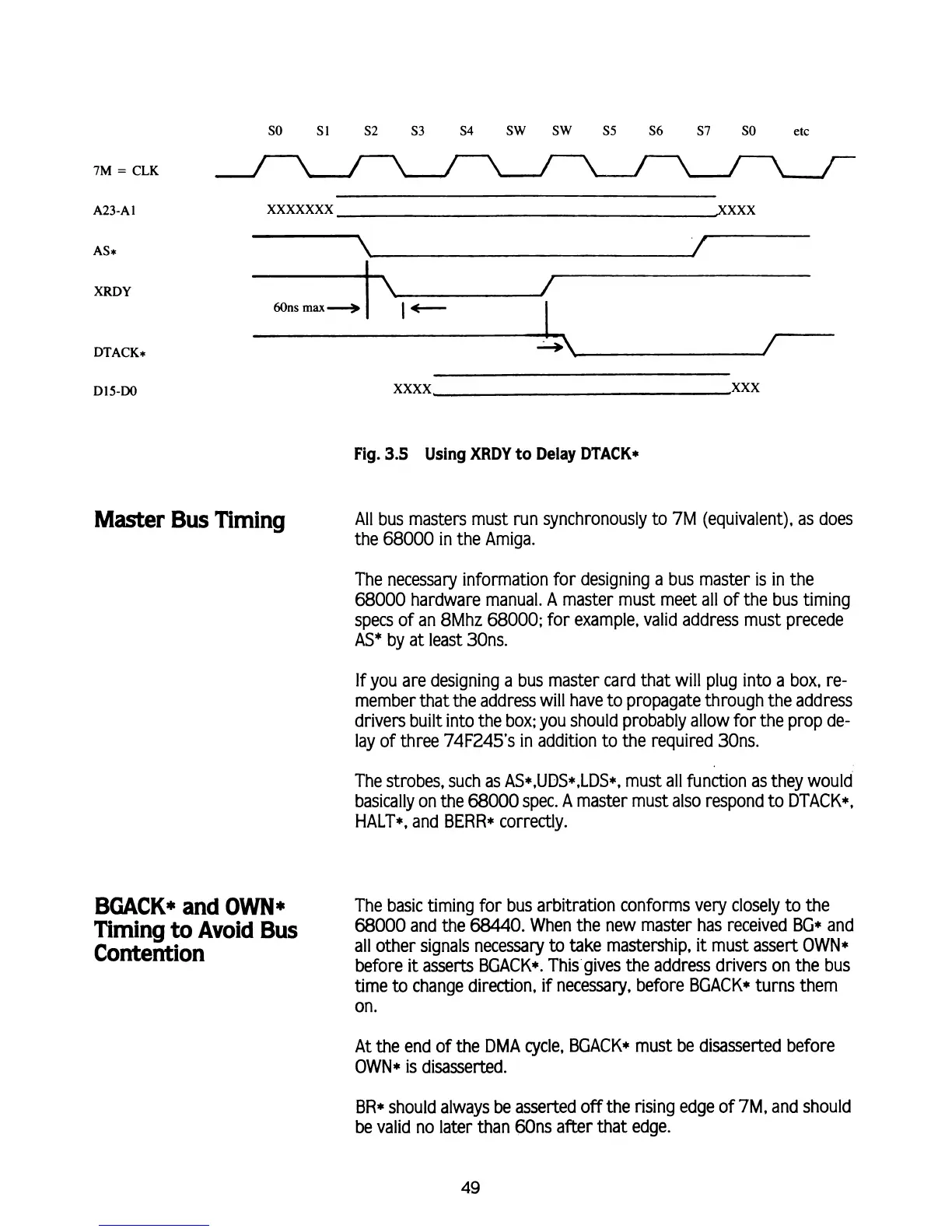

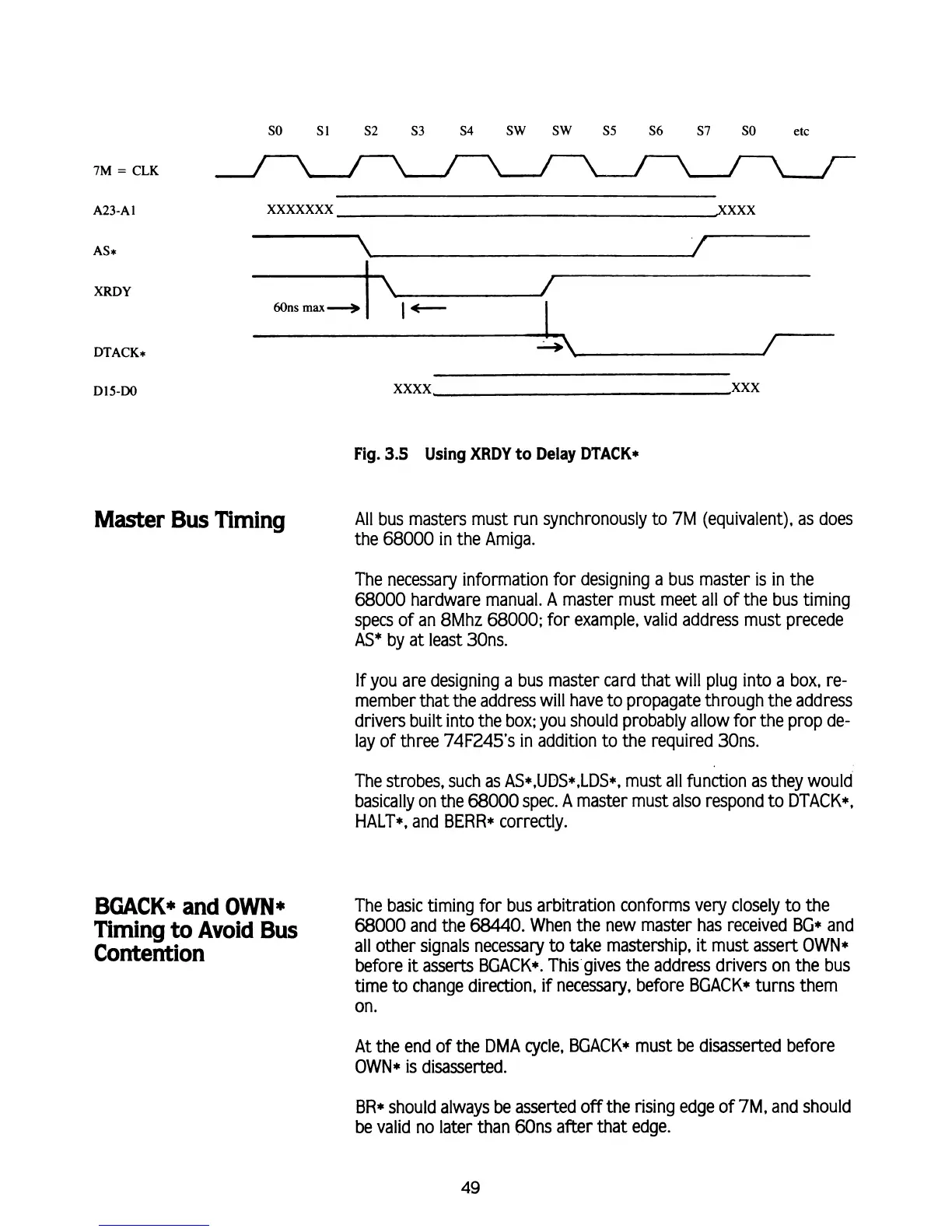

SO S1 S2 S3

S4

SW

SW

S5 S6 S7 SO

etc

7M

=

CLK

A23-AI XXXXXXX JXXX

AS*

DTACK*

D15-W

XRDY

6011s

max-

XXXX. XXX

/

1

t

Master

Bus Timing

I

BGACK*

and

OWN*

Timing to Avoid

Bus

Contention

Fig.

3.5

Using

XRDY

to

Delay DTACK*

All

bus masters must run synchronously to

7M

(equivalent), as does

the 68000 in the Amiga.

The necessary information for designing a bus master is in the

68000 hardware manual.

A

master must meet all of the bus timing

specs of an 8Mhz

68000;

for example, valid address must precede

AS* by at least

30ns.

If

you are designing a bus master card that will plug into a box, re-

member that the address will have to propagate through the address

drivers built into the box; you should probably allow for the prop de-

lay of three

74F245's in addition to the required 30ns.

The strobes, such as AS*,UDS*,LDS*, must all function as they would

basically on the

68000

spec.

A

master must also respond to DTACK*,

HALT*, and BERR* correctly.

The basic timing for bus arbitration conforms very closely to the

68000

and the

68440.

When the new master has received BG* and

all other signals necessary

to

take mastership,

it

must assert OWN*

before

it

asserts BGACK*. This gives the address drivers on the bus

time to change direction,

if

necessary, before BGACK* turns them

on.

At

the end of the

DMA

cycle, BGACK* must be disasserted before

OWN* is disasserted.

BR* should always be asserted off the rising edge of

7M,

and should

be valid no later than

60ns after that edge.

Loading...

Loading...