CO

152

143

134

161

116

107

98

125

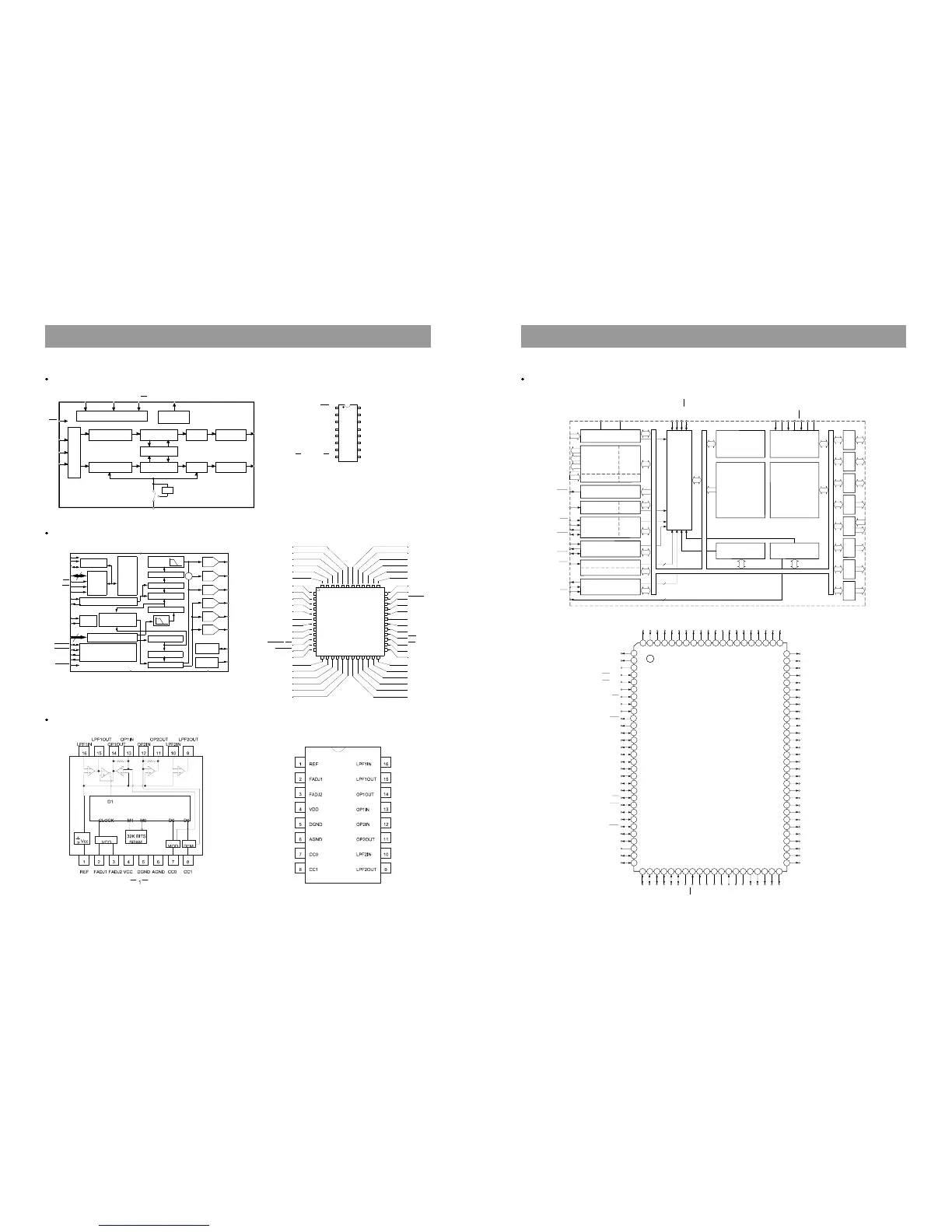

Reset RST MUTEC Mute Control

Serial Data SDATA AOUTA Analog Output A

Serial Clock SCLK VA Analog Power

ft/Right Clock LRCK AGND Analog Ground

Master Clock MCLK AOUTB Analog Output B

SCL/CCLK SCL/CCLK REF_GND Reference Ground

SDA/CDIN SDA/CDIN VQ Quiescent Voltage

AD0/CS

AD0/CS FILT+ Positive Voltage Reference

Loading...

Loading...