3. Instruction Set

The error checksum LRC CHK (0, 1) can be calculated by LRC instruction (8-bit mode, M1161 =

ON).

LRC checksum: 01 H + 03 H + 07 H + 08 H + 00 H + 06 H = 19 H. Operate 2’s complement on 19H

and the result is E7H. Store ‘E’(45 H) in the low byte of D113 and ‘7’ (37 H) in the low byte of D114.

Remarks:

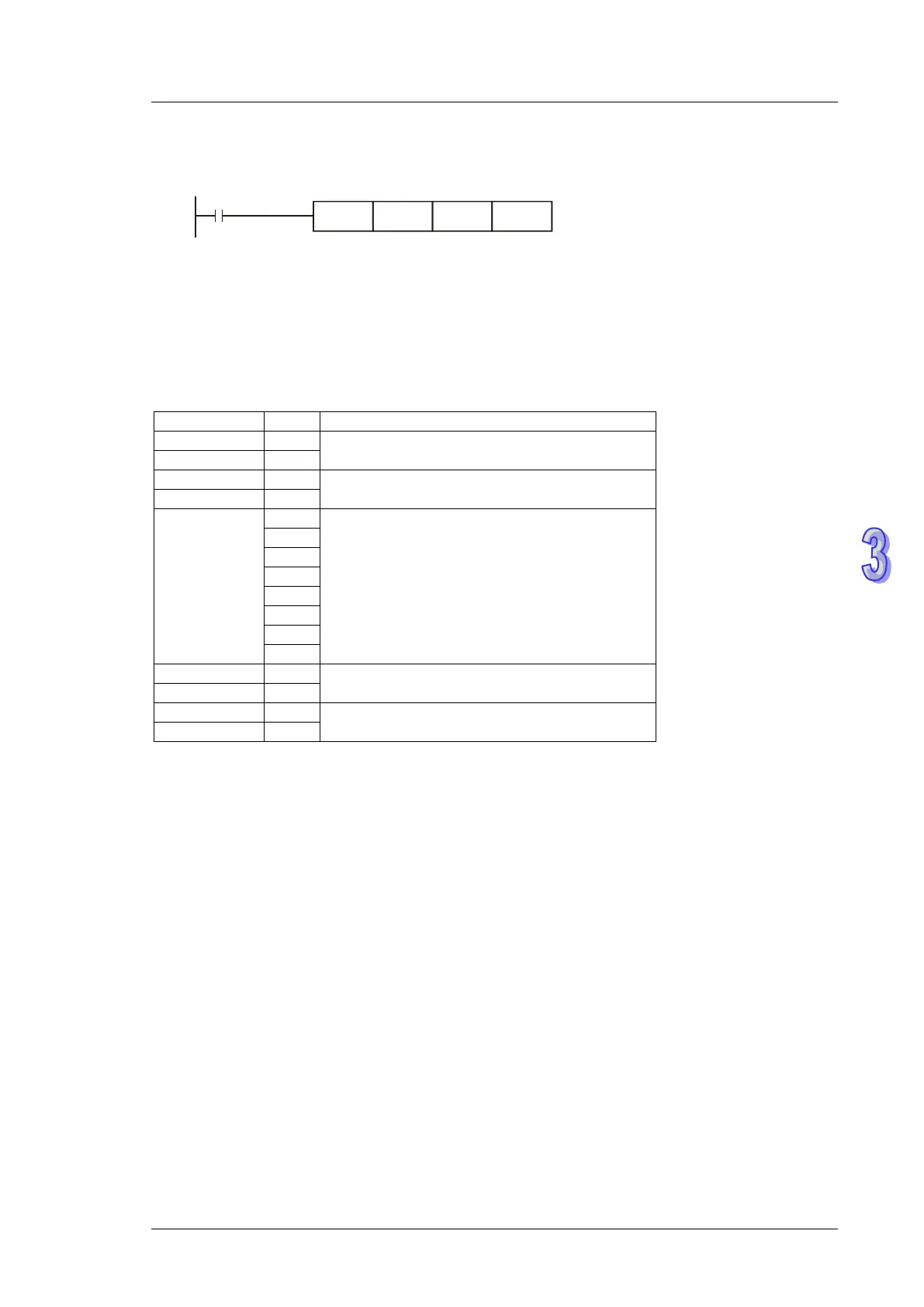

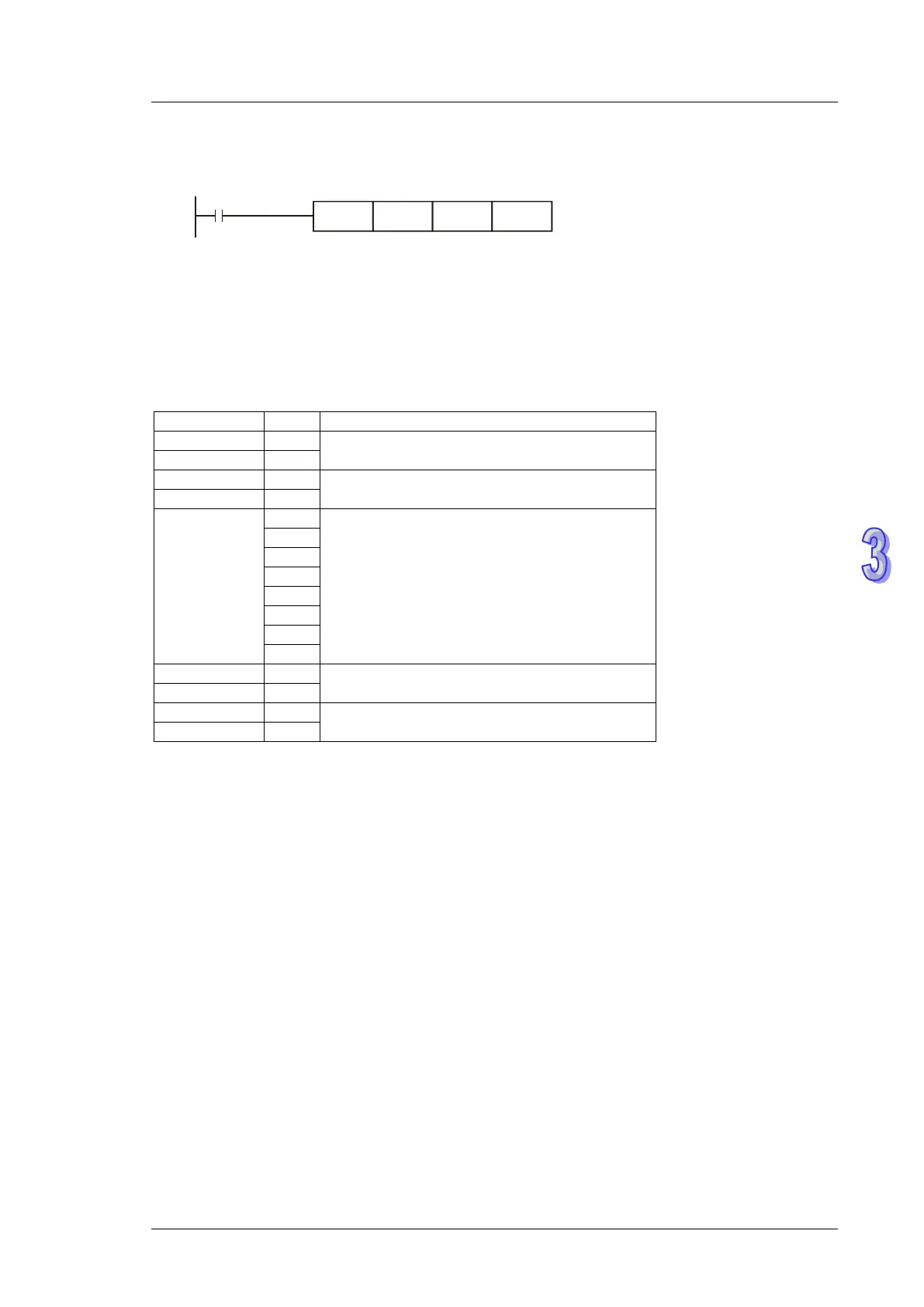

ASCII mode communication data:

Communication:

8-bit address consists of 2 ASCll codes

Function code:

8-bit function consists of 2 ASCll codes

…….

DATA 0

n × 8-bit data consists of 2n ASCll

codes

LRC checksum:

8-bit checksum consists of 2 ASCll codes

End word:

END Hi = CR (0DH), END Lo = LF(0AH)

LRC checksum: Operate 2’s complement on the summed up value from communication address

to the end of data, i.e. 01 H + 03 H + 21 H + 02 H + 00 H + 02 H = 29 H, the operation result of 29H

is D7H.

Loading...

Loading...