SN74CBT3251PWR (DIGITAL : IC723)

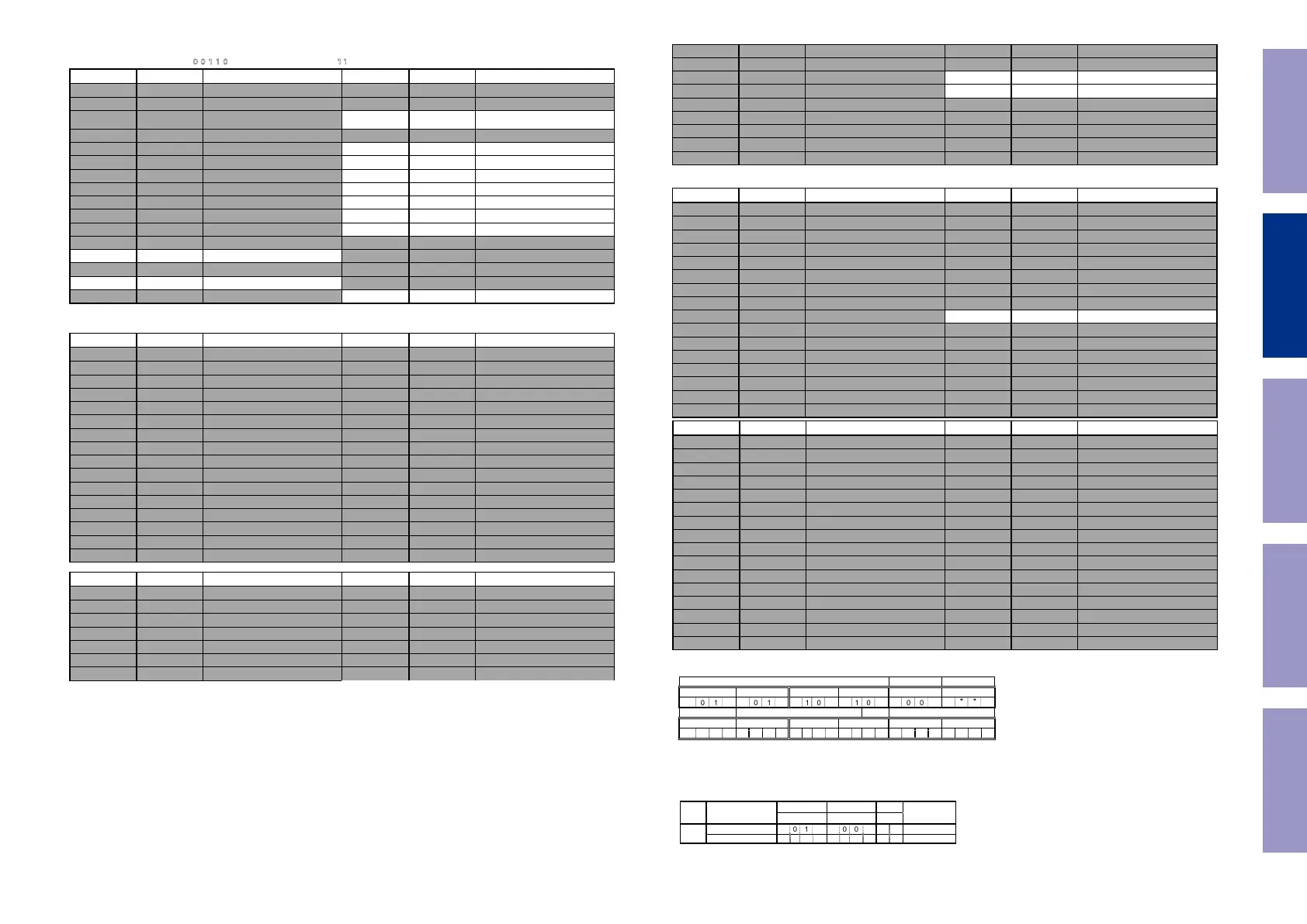

Block diagram

SN74CBT3251

1-OF-8 FET MULTIPLEXER/DEMULTIPLEXER

SCDS019L − MAY 1995 − REVISED JANUARY 2004

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5-Ω Switch Connection Between Two Ports TTL-Compatible Input Levels

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

B4

B3

B2

B1

A

NC

OE

GND

V

CC

B5

B6

B7

B8

S0

S1

S2

D, DB, DBQ, OR PW PACKAGE

(TOP VIEW)

NC − No internal connection

RGY PACKAGE

(TOP VIEW)

1 16

89

2

3

4

5

6

7

15

14

13

12

11

10

B5

B6

B7

B8

S0

S1

B3

B2

B1

A

NC

OE

B4

S2

V

GND

CC

NC − No internal connection

description/ordering information

The SN74CBT3251 is a 1-of-8 high-speed TTL-compatible FET multiplexer/demultiplexer. The low on-state

resistance of the switch allows connections to be made with minimal propagation delay.

When output enable (OE

) is low, the SN74CBT3251 is enabled. S0, S1, and S2 select one of the B outputs for

the A-input data.

ORDERING INFORMATION

T

A

PACKAGE

†

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

QFN − RGY Tape and reel SN74CBT3251RGYR CU251

SOIC − D

Tape and reel SN74CBT3251DR

CBT3251

−40°C to 85°C

SSOP − DB Tape and reel SN74CBT3251DBR CU251

SSOP (QSOP) − DBQ Tape and reel SN74CBT3251DBQR CU251

TSSOP − PW

Tape and reel SN74CBT3251PWR

CU251

†

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design

guidelines are available at www.ti.com/sc/package.

Copyright © 2004, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN74CBT3251

1-OF-8 FET MULTIPLEXER/DEMULTIPLEXER

SCDS019L − MAY 1995 − REVISED JANUARY 2004

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

FUNCTION TABLE

(each multiplexer/demultiplexer)

INPUTS

OE S2 S1 S0

FUNCTION

L L L L A port = B1 port

L L L H A port = B2 port

L L H L A port = B3 port

L L H H A port = B4 port

L H L L A port = B5 port

L H L H A port = B6 port

L H H L A port = B7 port

L H H H A port = B8 port

H X X X Disconnect

logic diagram (positive logic)

B5

B1

A

B2

B3

B4

B6

B7

B8

OE

S0

S1

S2

5

7

11

10

9

4

3

2

1

15

14

13

12

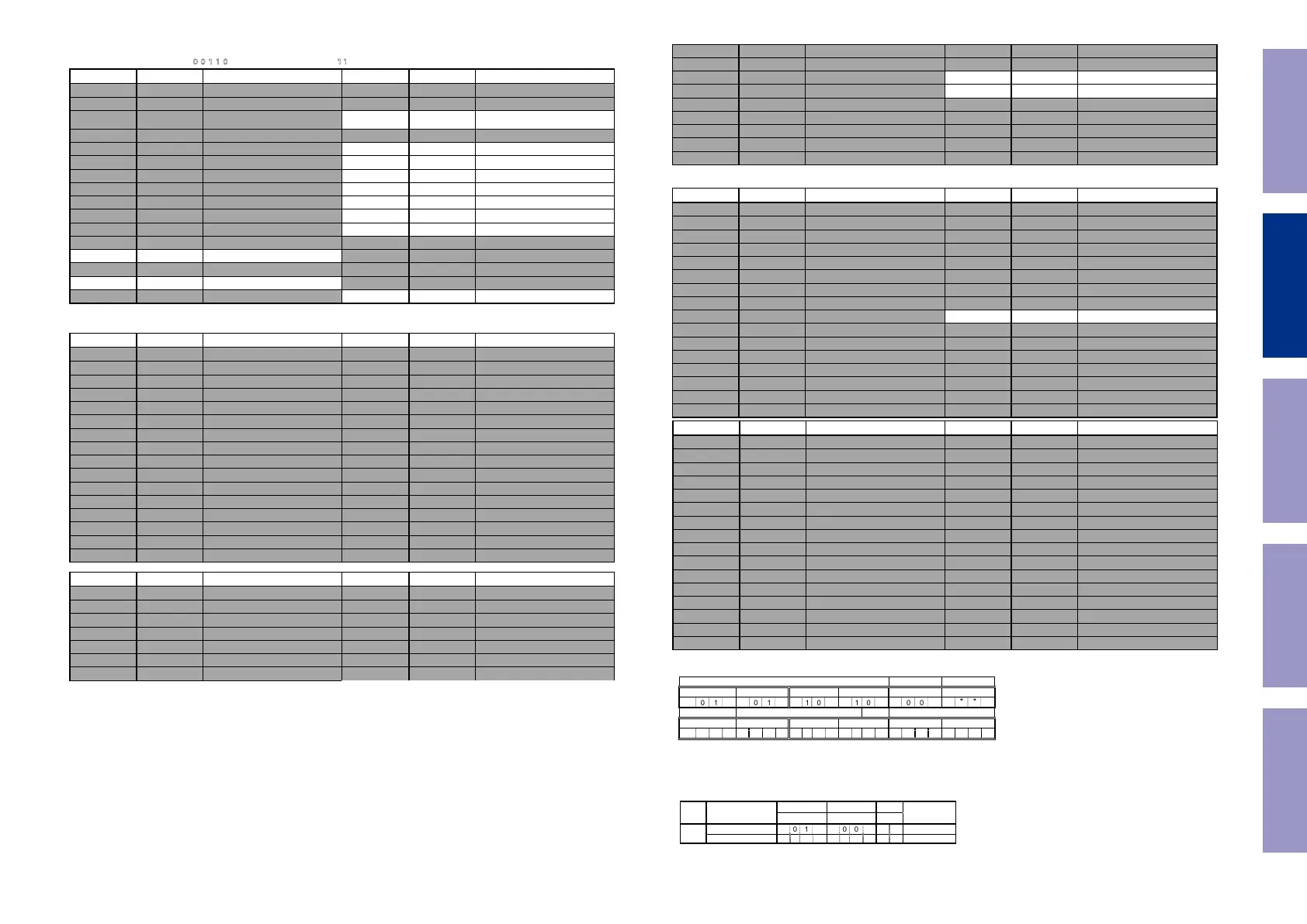

TOP268VG (SMPS : IC601)

Figure 3. Functional Block Diagram.

PI-4511-012810

SHUTDOWN/

AUTO-RESTART

CLOCK

CONTROLLED

TURN-ON

GATE DRIVER

CURRENT LIMIT

COMPARATOR

INTERNAL UV

COMPARATOR

INTERNAL

SUPPLY

5.8 V

4.8 V

SOURCE (S)

SOURCE (S)

S

R

Q

D

MAX

STOP

SOFT

START

CONTROL (C)

VOLTAGE

MONITOR (V)

FREQUENCY (F)

-

+

5.8 V

I

FB

1 V

Z

C

V

C

+

-

+

-

+

-

LEADING

EDGE

BLANKING

÷ 16

1

HYSTERETIC

THERMAL

SHUTDOWN

SHUNT REGULATOR/

ERROR AMPLIFIER

+

-

DRAIN (D)

ON/OFF

DC

MAX

DC

MAX

66k/132k

0

OV/

UV

OVPV

V

I (LIMIT)

CURRENT

LIMIT

ADJUST

V

BG

+ V

T

LINE

SENSE

SOFT START

OFF

F REDUCTION

F REDUCTION

STOP LOGIC

EXTERNAL CURRENT

LIMIT (X)

OSCILLATOR

WITH JITTER

PWM

K

PS(UPPER)

K

PS(LOWER)

SOFT START

I

FB

I

PS(UPPER)

I

PS(LOWER)

K

PS(UPPER)

K

PS(LOWER)

Pin Functional Description

DRAIN (D) Pin:

High-voltage power MOSFET DRAIN pin. The internal start-up

bias current is drawn from this pin through a switched high-

voltage current source. Internal current limit sense point for

drain current.

CONTROL (C) Pin:

Error amplifier and feedback current input pin for duty cycle

control. Internal shunt regulator connection to provide internal

bias current during normal operation. It is also used as the

connection point for the supply bypass and auto-restart/

compe

nsation capacitor.

EXTERNAL CURRENT LIMIT (X) Pin:

Input pin for external current limit adjustment remote-ON/OFF

and device reset. A connection to SOURCE pin disables all

functions on this pin. This pin should not be left floating.

VOLTAGE MONITOR (V) Pin:

Input for OV, UV, line feed-forward with DC

MAX

reduction, output

overvoltage protection (OVP), remote-ON/OFF. A connection to

the SOURCE pin disables all functions on this pin. This pin should

not be left flo

ating.

FREQUENCY (F) Pin :

Input pin for selecting switching frequency 132 kHz if connected

to SOURCE pin and 66 kHz if connected to CONTROL pin. This

pin should not be left floating.

SOURCE (S) Pin:

Output MOSFET source connection for high-voltage power return.

Primary-side control circuit common and reference point.

NO CONNECTION (NC) Pin:

Internally not connected, floating potential pin.

Figure 4. Pin Configuration (Top View).

12 S

11 S

10 S

9 S

8 S

7 S

V 1

X 2

C 3

F 4

D 6

PI-5568-061011

K Package

(eSOP-12B)

Exposed Pad (On Bottom)

Internally Connected to

SOURCE Pin

Before Servicing

This Unit

Electrical Mechanical Repair Information Updating

47

Loading...

Loading...