35

IEEE 488.2 Register Model

6.5 The Status Byte Register

The Status Byte register reports conditions from the other registers. Data in the

instruments output buffer is immediately reported on the “Message Available”

bit (bit 4). Clearing an event register from one of the other registers will clear

the corresponding bits in the Status Byte condition register. Reading all

messages from the output buffer, including any pending queries, will clear the

“Message Available” bit. To set the enable register mask and generate an SRQ

(service request), you must write a decimal value to the register using the *SRE

command.

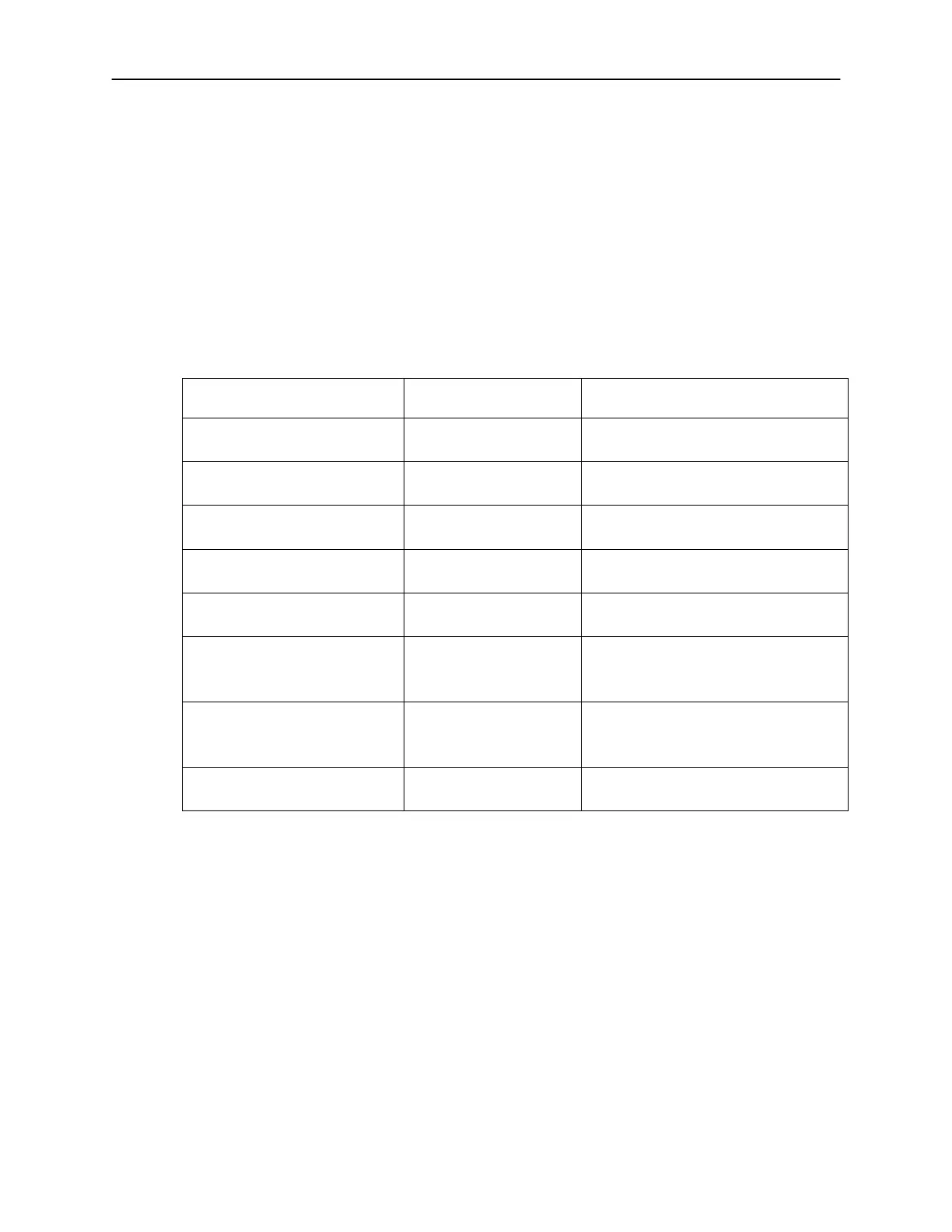

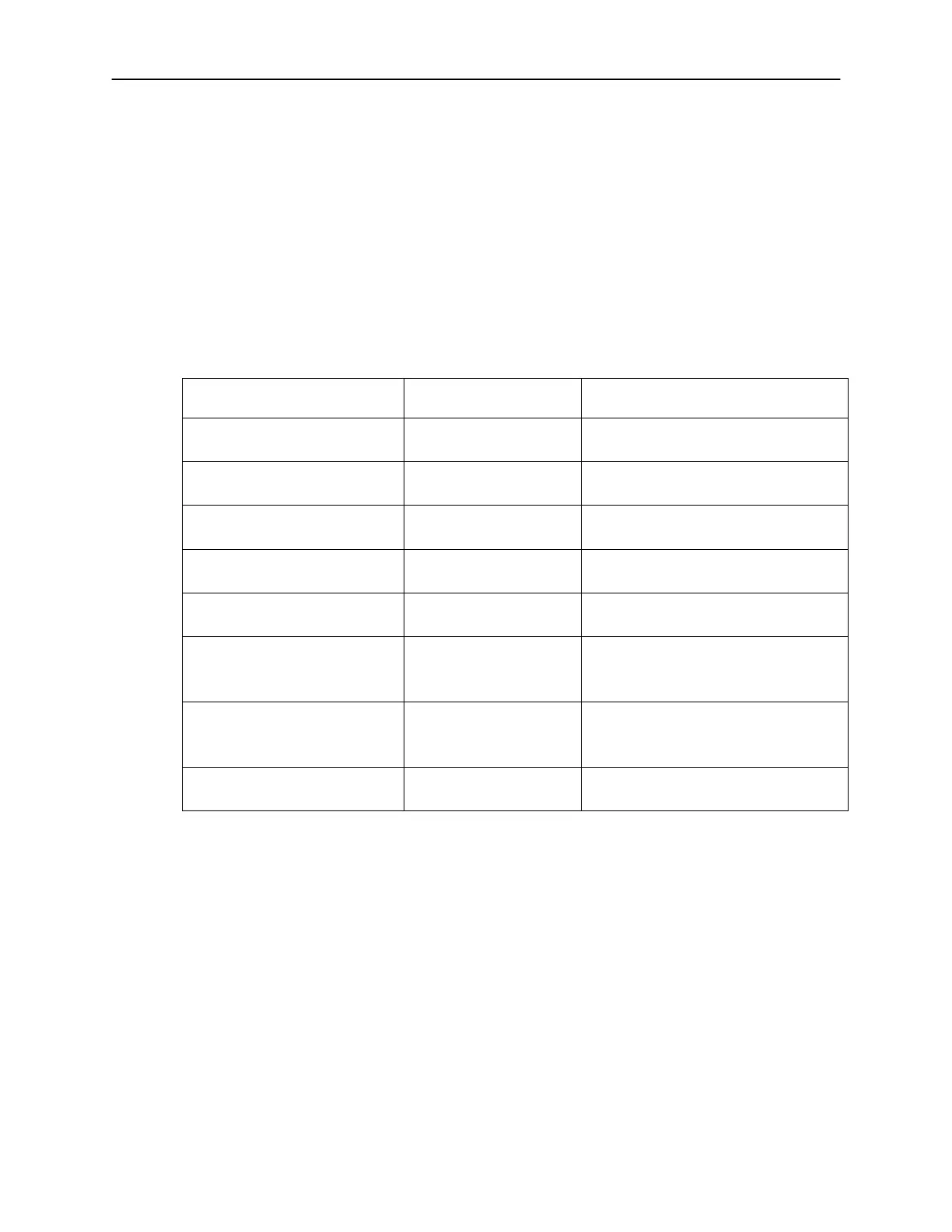

Table 6-1 Bit definitions – Status Byte Register

Bit Number Decimal Value Definitions

0 1 Free for manufacturer to

assign

1 2 Free for manufacturer to

assign

2 4 Free for manufacturer to

assign

3 8 Free for manufacturer to

assign

4 Message Available 16 Data is available in the

instruments output buffer

5 Standard Event 32 One or more bits are set in

the Standard Event Register

(bits must be enabled)

6 Master Summary 64 One or more bits are set in

the Status Byte Register

(bits must be enabled)

7 128 Free for manufacturer to

assign

The Status Byte condition register is cleared when:

• The *CLS command is executed.

• One of the event registers in the other registers are read (only the

corresponding bits are cleared in the Statue Byte condition register).

The Status Byte enable register is cleared when:

• The *SRE 0 command is executed.

Loading...

Loading...