1

11

1

PS_HOLD

PMIC2SDM_RESET_N

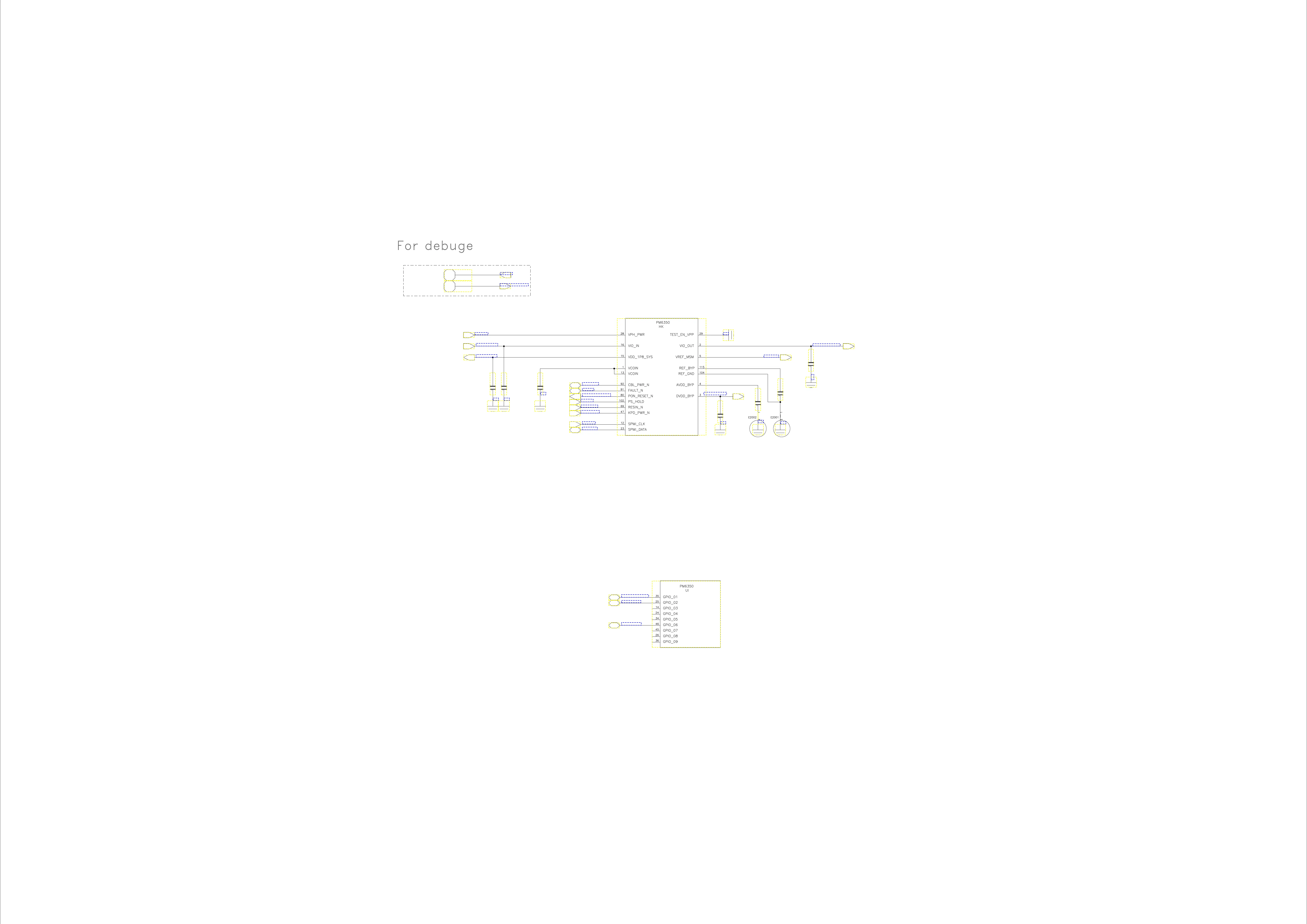

For debuge

VPH_PWR

VREG_L11A_1P8

VREG_1P8_SYS

C2007

1

1uF

2

C2013

2.2uF

2

1

CBL_PWR_N

FAULT_N

PMIC2SDM_RESET_N

PS_HOLD

PM_RESIN_N

PHONE_ON_N

SPMI_CLK

SPMI_DATA

VREG_VIO_OUT_1P8

1uF

2

C2011

1

VREF_MSM

C2009

1uF

2

1

1

2

1uF

C2008

AVDD_BYP

1

C2010

2

100nF

E2001

2 1

REF_BYP_B

12

E2002

NOTE1:SPMI_CLK & SPMI_DATA should be routed away from noisy traces

Route signals as a diff pair as much as possible

NOTE2:Dedicated trace from REF_BYP to cap.

Dedicated trace from REF_GND to cap.

Dedicated via to main ground plane right under PMIC pin (REF_GND)

or as close to the pin as possible.

Do NOT add via at cap.

NOTE3:REF_BYP and REF_GND should be

routed away from noisy traces

RTC_ALARM_TO_PM

KYPD_VOLP_N

TP2001

TP2002

PMIC_DVDD_BYP

C2006

2

1

47uF

NPI_DOWN_EN

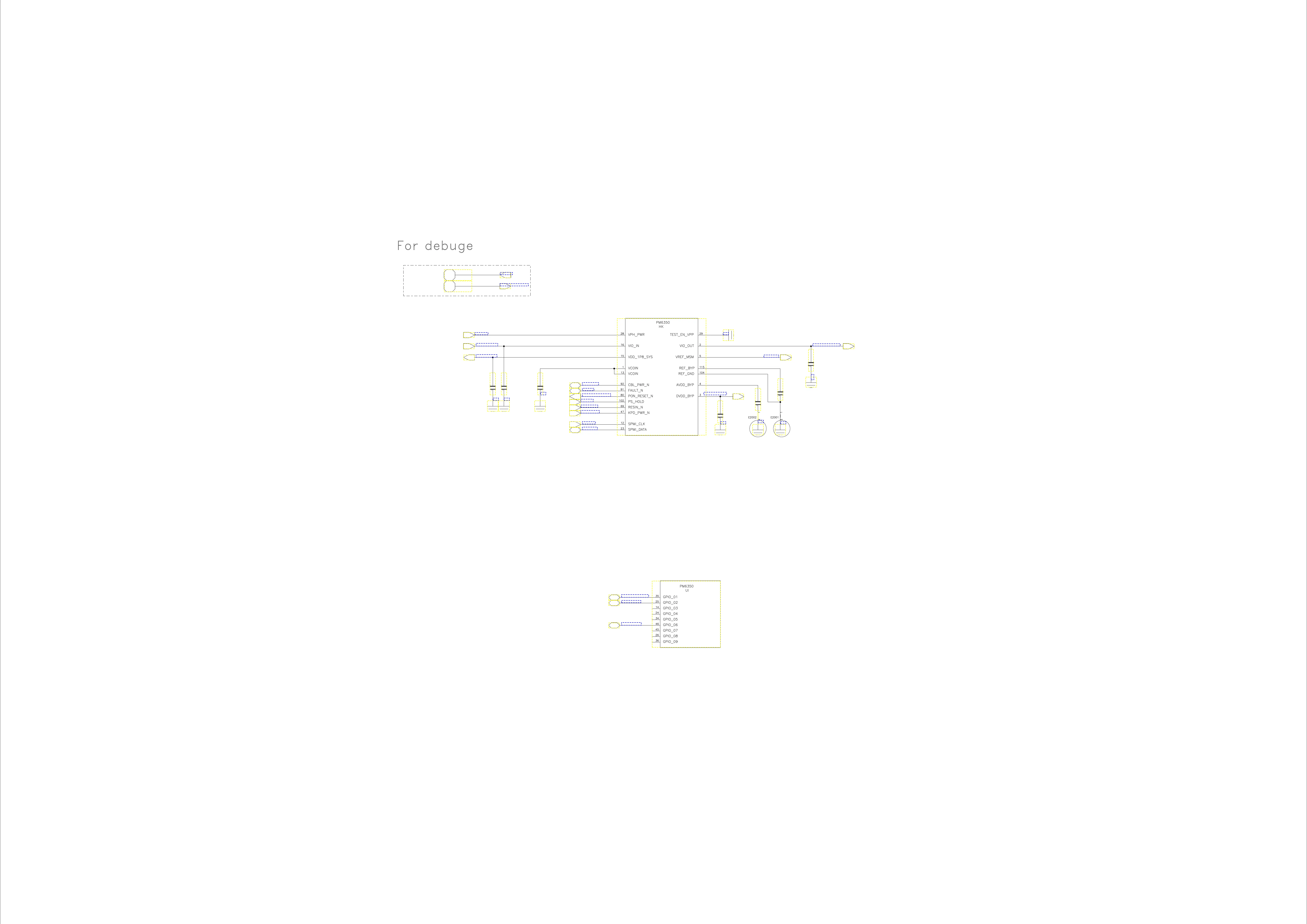

PM6350

UI

GPIO_03

GPIO_04

GPIO_02

GPIO_08

GPIO_05

GPIO_01

GPIO_09

GPIO_07

GPIO_06

U2001

46

45

36

35

34

26

25

24

14

PM-6350-0-FOWPSP121-TR-00-0

PM6350

HK

VCOIN

VIO_OUT

DVDD_BYP

AVDD_BYP

VREF_MSM

SPMI_CLK

VCOIN

VDD_1P8_SYS

VIO_IN

SPMI_DATA

VPH_PWR TEST_EN_VPP

KPD_PWR_N

RESIN_N

PON_RESET_N

FAULT_N

CBL_PWR_N

PS_HOLD

REF_GND

REF_BYP

U2001

115

104

102

92

91

80

69

47

2928

23

16

15

13

12

5

4

3

2

1

PM-6350-0-FOWPSP121-TR-00-0

Loading...

Loading...