6

Revision 1.9

256M Double Data Rate Synchronous DRAM

A3S56D30ETP

A3S56D40ETP

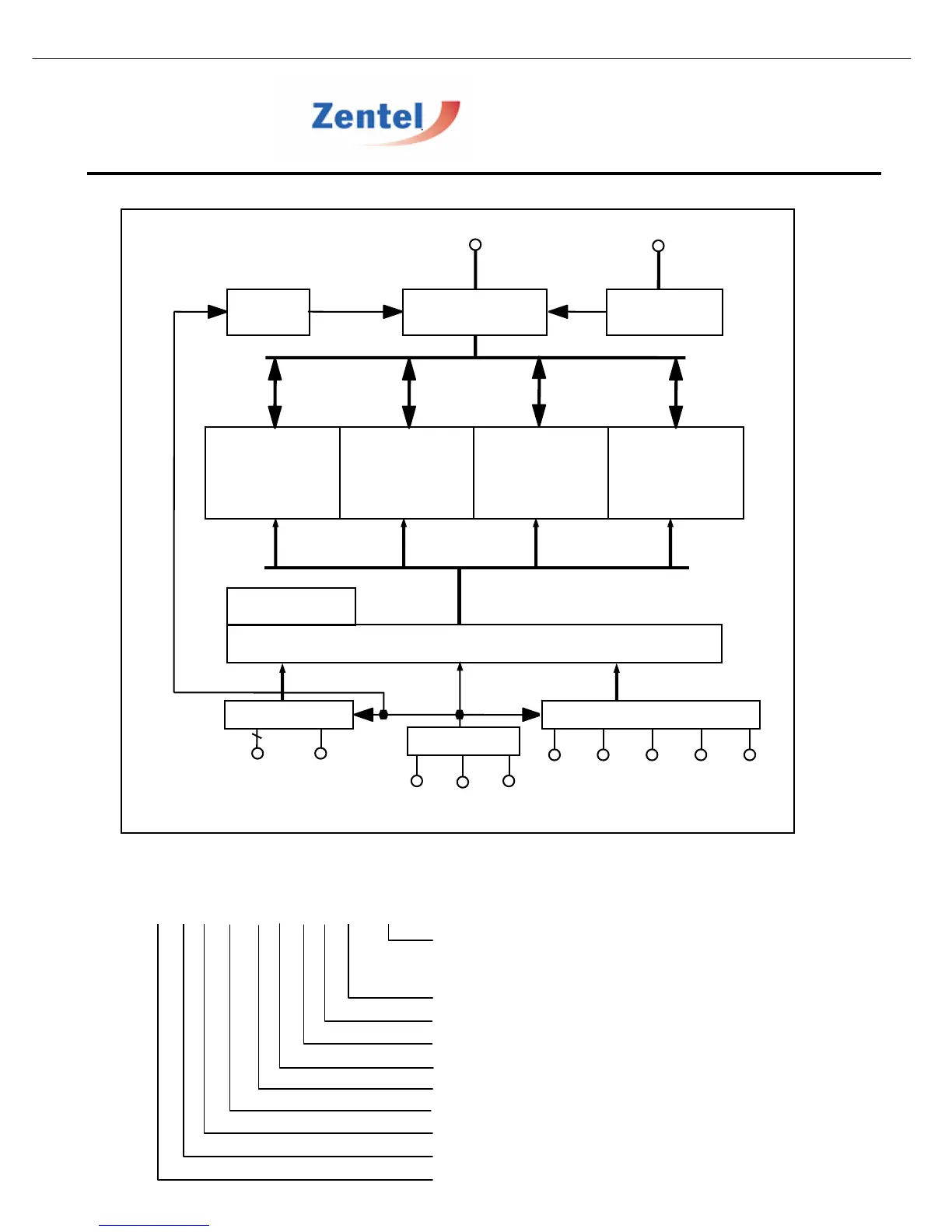

BLOCK DIAGRAM

/CS /RAS /CAS /WE UDM,

LDM

Memory

Array

Bank #0

DQ0 - 15

I/O Buffer

Memory

Array

Bank #1

Memory

Array

Bank #2

Memory

Array

Bank #3

Mode Register

Control Circuitry

Address Buffer

A0-12

BA0,1

Clock Buffer

CLK CKE

Control Signal Buffer

DQS Buffer

UDQS, LDQS

DLL

/CLK

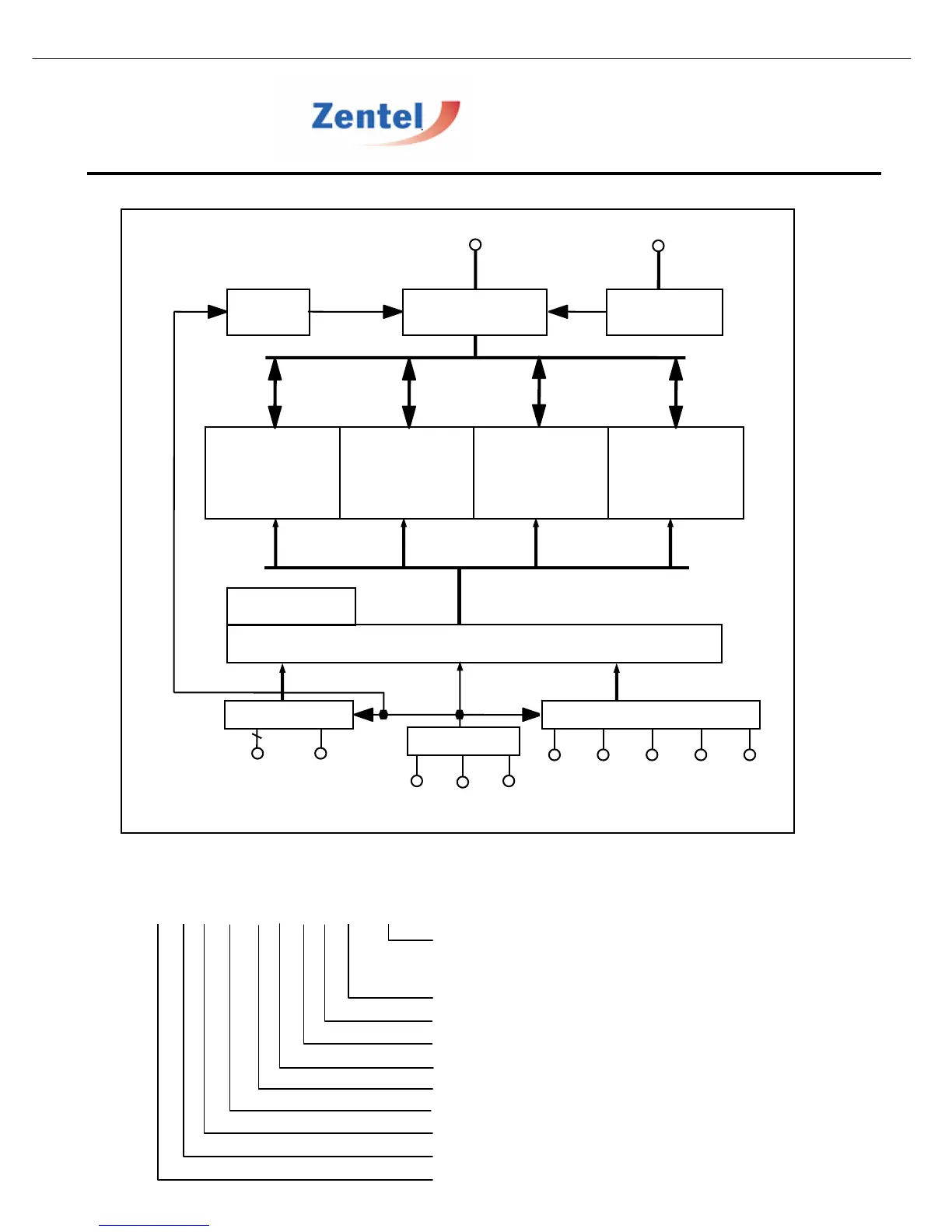

A3S56D40ETP

Type Designation Code

This rule is applied to only Synchronous DRAM family.

Zentel DRAM

Speed Grade

Package Type TP: TSOP(II)

Process Generation

Function Reserved for Future Use

Organization 2

n

4: x16

DDR Synchronous DRAM

Density 56: 256M bits

Interface S:SSTL_3, _2

Memory Style (DRAM)

A 3 S 56 D 4 0 E TP –G5

6: 166MHz @CL=3.0/2.5, and 133MHz @CL=2.0

5: 200MHz @CL=3.0, 166MHz @CL=2.5, and 133MHz @CL=2.0

5E: 200MHz @CL=3.0/2.5, and 133MHz @CL=2.0

AVR3600 harman/kardon

Loading...

Loading...