5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

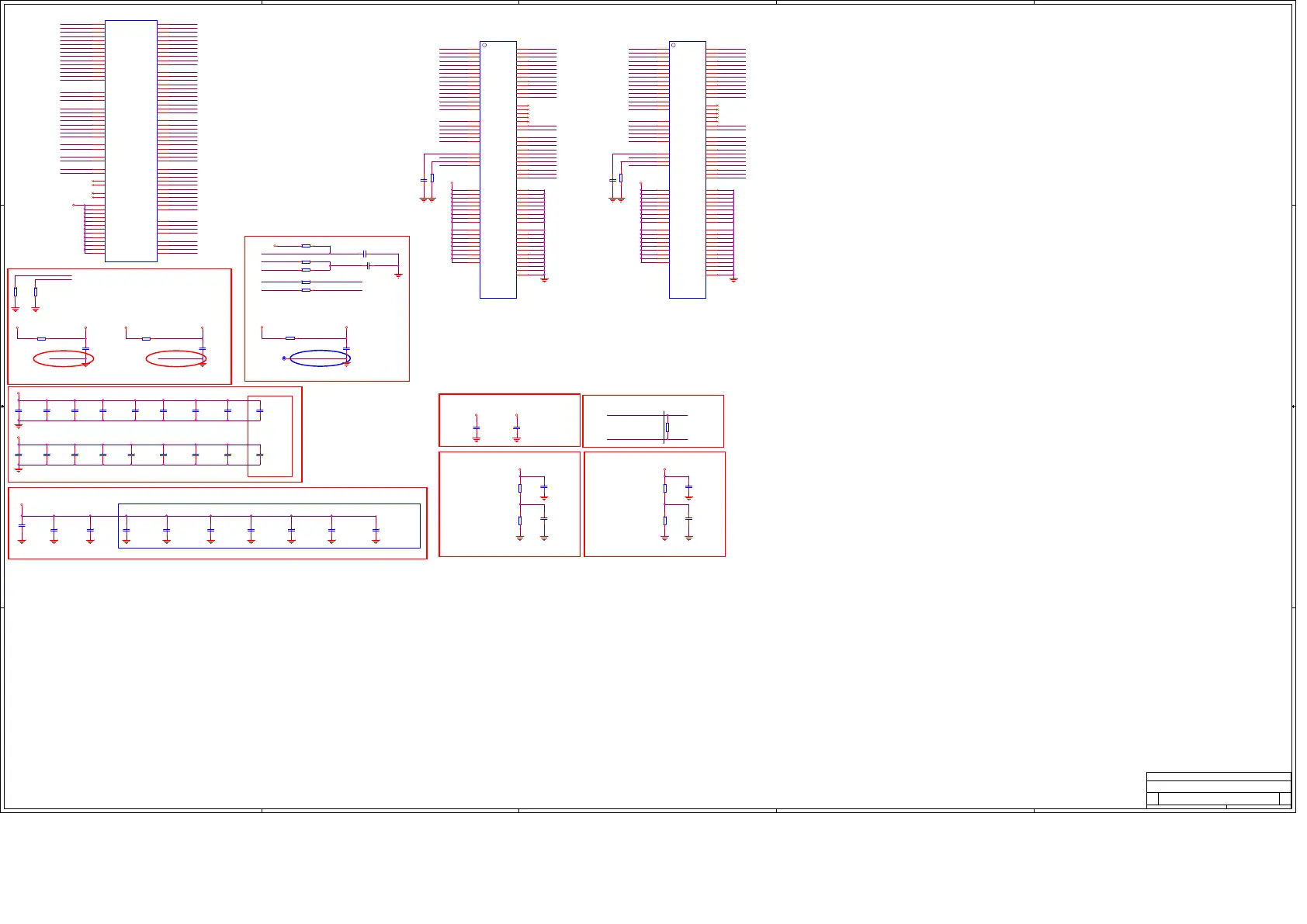

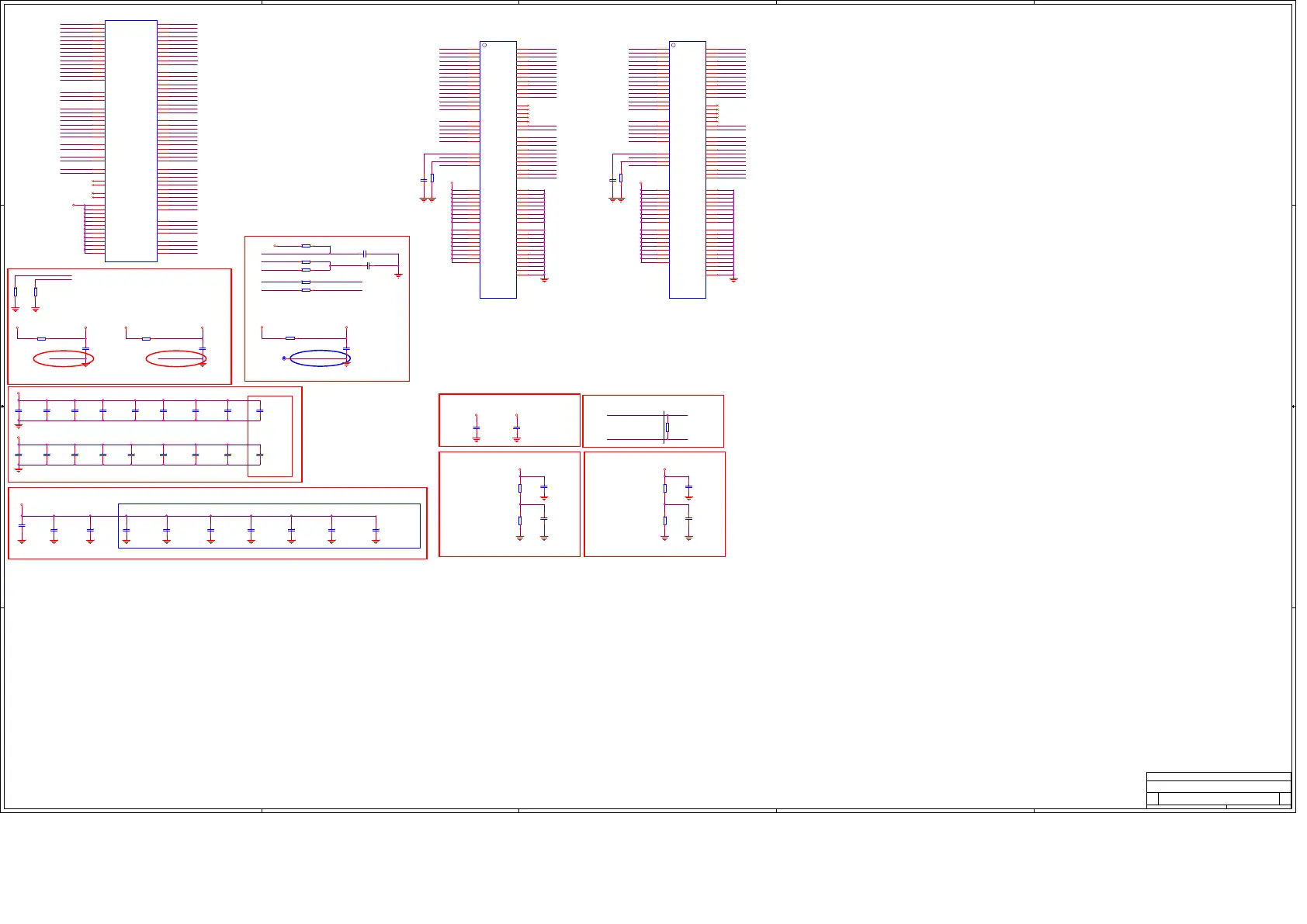

Keep a trace from the GND of Cap to Main Chip

DRAM#2 Bypass Cap

DRAM#1 Bypass Cap

Close to DRAM

Main Chip Bottom Side

DE-CAP.

Reseved on bottom side.

NEAR Main Chip

Differential Clock

NEAR DRAM

DDR3#2 Ref Volt.DDR3#1 Ref Volt.

Near DRAMNear DRAM

DDR3#1 DDR3#2

Hisense Electric Co.,LTD

需要换料,系统里没料

ARD QS 0B

ARD QM0

ARD QS 0

ARD Q7

ARD Q6

ARD Q4

ARD Q5

ARD Q3

ARD Q0

ARD Q1

ARD Q2

ARD QS 2

ARD QS 3

ARD QM3

ARD QM2

ARD QS 3B

ARD QS 2B

ARD Q2 6

ARD Q2 5

ARD Q2 8

ARD Q2 4

ARD Q2 9

ARD Q3 0

ARD Q3 1

ARD Q2 7

ARD Q2 3

ARD QS 1B

ARD QS 1

ARD QM1

ARD Q2 0

ARD Q1 6

ARD Q2 1

ARD Q1 7

ARD Q2 2

ARD Q1 8

ARD Q1 9

ARD Q9

ARD Q8

ARD Q1 1

ARD Q1 0

ARD Q1 3

ARD Q1 2

ARD Q1 5

ARD Q1 4

ARA 12

ARA 1

ARA 13

ARA 14

ARA 2

ARA 7

ARA 9

ARA 8

ARA 3

ARA 4

ARA 10

ARA 5

ARA 0

ARA 11

ARA 6

ARO DT

ARR AS

ARC AS

ARW E

ARC SD

ARC S

ARB A2

ARB A0

ARB A1

ARR ES ET #

ARC KE

ARC LK 0

ARC LK 0B

ART P

ART N

AVD D3 3_ DD R

AVD D1 0_ DD R

DDR VR EF _A 1

DDR VR EF _A 2

AVD D1 0_ DD R

AVS S_ DD R

AVS S3 3_ DD R

AVS S_ DD R

AVS S_ DD R

AVD D1 0_ DD R

ART N

ART P

AVD D3 3_ DD R AV DD 10_DD R

AVS S3 3_ DD R AVS S_ DD R

ARR ES ET #

DDR VR EF _A 1 A_V RE FC A1

DDR VR EF _A 2 A_V RE FC A2

ARC S

ARC SD

AVS S_ DD R

AVD D1 0_ DD R

A_V RE FC A1 A_V RE FC A2

ARC LK 0B

ARC LK 0A RC LK 0

ARC LK 0B

ARB A2

ARB A1

ARB A0

ARR AS

ARO DT

ARC LK 0

ARC LK 0B

ARC S

ARC AS

ARW E

ARA 1

ARA 2

ARA 3

ARA 0

ARA 4

ARA 5

ARA 6

ARA 7

ARA 8

ARA 13

ARA 9

ARA 10

ARA 11

ARA 12

ARR ES ET #

DDR VR EF _A 2

A_V RE FC A1

A_Z Q2

ARR ES ET #

A_V RE FC A2

ARC KE

DDR VR EF _A 1

A_Z Q1

ARA 3

ARA 2

ARA 1

ARA 0

ARA 8

ARA 7

ARA 6

ARA 5

ARA 4

ARA 13

ARA 12

ARA 11

ARA 10

ARA 9

ARO DT

ARW E

ARR AS

ARB A0

ARC LK 0

ARC LK 0B

ARC AS

ARC S

ARB A2

ARB A1

ARC KE

ARD QS 1

ARD QS 1B

ARD Q7

ARD Q6

ARD Q5

ARD Q4

ARD Q3

ARD Q0

ARD Q1

ARD Q2

ARD QS 0B

ARD QS 0

ARD QM0

ARD Q9

ARD Q8

ARD Q1 1

ARD Q1 0

ARD Q1 3

ARD Q1 2

ARD Q1 5

ARD Q1 4

ARD QM1

ARD QM2

ARD QS 2

ARD QS 2B

ARD QM3

ARD QS 3

ARD QS 3B

ARD Q2 6

ARD Q2 5

ARD Q2 8

ARD Q2 4

ARD Q2 9

ARD Q3 0

ARD Q3 1

ARD Q2 7

ARD Q2 3

ARD Q2 0

ARD Q1 6

ARD Q2 1

ARD Q1 7

ARD Q2 2

ARD Q1 8

ARD Q1 9

ARA 14 ARA 14

1.5V _D DR

AVD D1 0_ DD RVCC KDVD D3 V3 AVD D3 3_ DD R

1.5V _D DR

1.5V _D DR

1.5V _D DR

1.5V _D DR

VCC K AVD D1 0_ DD R

1.5V _D DR 1.5 V_ DDR

1.5V _D DR 1.5V _D DR

1.5V _D DR1.5V _D DR

Title

Size D oc ume nt Numbe r Rev

Date: Shee t of

1.0

MT5657

D

9 22Thurs day, J une 25 , 20 15

Title

Size D oc ume nt Numbe r Rev

Date: Shee t of

1.0

MT5657

D

9 22Thurs day, J une 25 , 20 15

Title

Size D oc ume nt Numbe r Rev

Date: Shee t of

1.0

MT5657

D

9 22Thurs day, J une 25 , 20 15

R275 0R

R274 0R

C297

100n/16V

C305

100n/16V

R280

1k

C285

100n/16V

C306

100n/16V

C299

100n/16V

R263

240R

C286

100n/16V

C307

100n/16V

C28 7

10u/1 0V

C301

100n/16V

C308

100n/16V

C273

100n/16V

C290

100n/16V

C29 8

10u/1 0V

TP29

1

C300

100n/16V

C302

100n/16V

R26 5 47R

C291

100n/16V

R26 6 47R

C292

100n/16V

C274

100n/16V

C27 6

1u/10 V

C293

100n/16V

R276

100R

N57

H5TQ 4G 63 CF R-RD C

VDD_0

B2

NC_0

J1

VSS_0

A9

VSSQ_0

B1

UDQS#

B7

VDDQ_0

A1

DQ14

B8

VSSQ_1

B9

UDM

D3

UDQS

C7

VSSQ_2

D1

DQ15

A3

VDDQ_1

A8

DQ9

C3

VDDQ_2

C1

VDDQ_3

C9

DQ8

D7

VDDQ_4

D2

DQ12

A7

VSSQ_3

D8

DQ11

C2

DQ10

C8

VSSQ_4

E2

DQ13

A2

VDD_1

D9

NC_1

J9

VSS_1

B3

VSSQ_5

E8

LDQS#

G3

VDDQ_5

E9

DQ6

G2

VSSQ_6

F9

LDM

E7

LDQS

F3

VSSQ_7

G1

DQ7

H7

VDDQ_6

F1

DQ1

F7

VDDQ_7

H2

DQ0

E3

VDDQ_8

H9

DQ4

H3

VSSQ_8

G9

DQ3

F8

DQ2

F2

BA2

M3

DQ5

H8

VDD_5

N1

VREFDQ

H1

VSS_2

E1

VSS_5

J8

CK

J7

VDD_2

G7

CKE

K9

WE#

L3

RAS#

J3

CK#

K7

ODT

K1

RESET#

T2

BA0

M2

BA1

N8

CAS#

K3

CS#

L2

A10/AP

L7

A1

P7

A2

P3

A0

N3

VDD_3

K2

VSS_3

G8

A3

N2

A5

P2

A6

R8

A4

P8

A7

R2

A9

R3

A11

R7

A8

T8

VSS_4

J2

VDD_4

K8

A12/BC#

N7

NC_3

L9

ZQ

L8

NC_2

L1

VREFCA

M8

NC_4

M7

A13

T3

A14

T7

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VDD_6

N9

VDD_7

R1

VDD_8

R9

C798

4.7u/10 V

C289

4.7u/10V

C275 100n/16V

C309

100n/16V

C277

100n/16V

C279

100n/16V

R262

240R

R267 0R/NC

C283

100n/16V

C303

4.7u/10V

C280

100n/16V

N56

H5TQ 4G 63 CF R-RD C

VDD_0

B2

NC_0

J1

VSS_0

A9

VSSQ_0

B1

UDQS#

B7

VDDQ_0

A1

DQ14

B8

VSSQ_1

B9

UDM

D3

UDQS

C7

VSSQ_2

D1

DQ15

A3

VDDQ_1

A8

DQ9

C3

VDDQ_2

C1

VDDQ_3

C9

DQ8

D7

VDDQ_4

D2

DQ12

A7

VSSQ_3

D8

DQ11

C2

DQ10

C8

VSSQ_4

E2

DQ13

A2

VDD_1

D9

NC_1

J9

VSS_1

B3

VSSQ_5

E8

LDQS#

G3

VDDQ_5

E9

DQ6

G2

VSSQ_6

F9

LDM

E7

LDQS

F3

VSSQ_7

G1

DQ7

H7

VDDQ_6

F1

DQ1

F7

VDDQ_7

H2

DQ0

E3

VDDQ_8

H9

DQ4

H3

VSSQ_8

G9

DQ3

F8

DQ2

F2

BA2

M3

DQ5

H8

VDD_5

N1

VREFDQ

H1

VSS_2

E1

VSS_5

J8

CK

J7

VDD_2

G7

CKE

K9

WE#

L3

RAS#

J3

CK#

K7

ODT

K1

RESET#

T2

BA0

M2

BA1

N8

CAS#

K3

CS#

L2

A10/AP

L7

A1

P7

A2

P3

A0

N3

VDD_3

K2

VSS_3

G8

A3

N2

A5

P2

A6

R8

A4

P8

A7

R2

A9

R3

A11

R7

A8

T8

VSS_4

J2

VDD_4

K8

A12/BC#

N7

NC_3

L9

ZQ

L8

NC_2

L1

VREFCA

M8

NC_4

M7

A13

T3

A14

T7

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VDD_6

N9

VDD_7

R1

VDD_8

R9

R272 0R/NC

C278

100n/16V

C295

100n/16V

C310

100n/16V

C311

100n/16V

C281

100n/16V

R26 8

47R

R277

1k

R264

47k/NC

C296

100n/16V

C31 2

22u/6 .3V /NC

C282

100n/16V

R26 9

47R

R279

1k

R273 0R

C284

100n/16V

C80 1

15n/5 0V /NC

C294

100n/16V

C30 4

1u/10 V

R278

1k

MT56 57 _3 1x3 1

N1-1

DDRV

AB8

DDRV

AC10

DDRV

AC9

DDRV

AD10

DDRV

AH10

DDRV

AH9

DDRV

AJ10

DDRV

AJ11

DDRV

AJ8

DDRV

AJ9

MEMTP

AE10

MEMTN

AF10

DDRVREF_A1

V1

ARCKE

AA7

ARCLK0

Y4

ARCLK0#

Y5

ARODT

AB6

ARRAS#

AA5

ARCAS#

AA6

ARCS#

AB5

ARWE#

AB7

ARRESET#

AK4

ARBA0

AD5

ARBA1

AE3

ARBA2

AD6

ARCSD#

AB4

ARA14

AM4

ARA13

AK5

ARA12

AF6

ARA11

AK6

ARA10

AD7

ARA9

AH4

ARA8

AL4

ARA7

AJ5

ARA6

AJ6

ARA5

AG7

ARA4

AG5

ARA3

AF4

ARA2

AF7

ARA1

AG6

ARA0

AE4

ARDQM0

AD1

ARDQS0

AC1

ARDQS0#

AC2

ARDQ0

Y2

ARDQ1

AG2

ARDQ2

Y1

ARDQ3

AG3

ARDQ4

W1

ARDQ5

AH3

ARDQ6

W2

ARDQ7

AH2

ARDQM1

AC3

ARDQS1

AD2

ARDQS1#

AE2

ARDQ8

AF1

ARDQ9

AB3

ARDQ10

AG1

ARDQ11

Y3

ARDQ12

AF2

ARDQ13

AB2

ARDQ14

AF3

ARDQ15

AB1

ARDQM2

AN2

ARDQS2

AM3

ARDQS2#

AN1

ARDQ16

AK2

ARDQ17

AT2

ARDQ18

AK1

ARDQ19

AU1

ARDQ20

AJ1

ARDQ21

AU2

ARDQ22

AJ3

ARDQ23

AR4

ARDQM3

AM1

ARDQS3

AP1

ARDQS3#

AP2

ARDQ24

AR2

ARDQ25

AL2

ARDQ26

AT1

ARDQ27

AK3

ARDQ28

AP3

ARDQ29

AL3

ARDQ30

AR3

ARDQ31

AM2

AVDD33_DDR

G1

AVDD10_DDR

AV20

ARTN

W10

ARTP

Y10

DDRVREF_A2

AJ2

TN_HPCPLL

AK18

TP_HPCPLL

AK19

DDRV

AK10

DDRV_CKA

Y6

AVSS_DDR

G2

AVSS_DDR

AU20

DDRV

AK11

AVDD10_DDR

AF13

AVSS_DDR

AF12

AVDD10_DDR

AE19

AVSS_DDR

AE17

Loading...

Loading...