RELIABILITY

TEST

DATA

OF

MICR')COMPUTER------------------

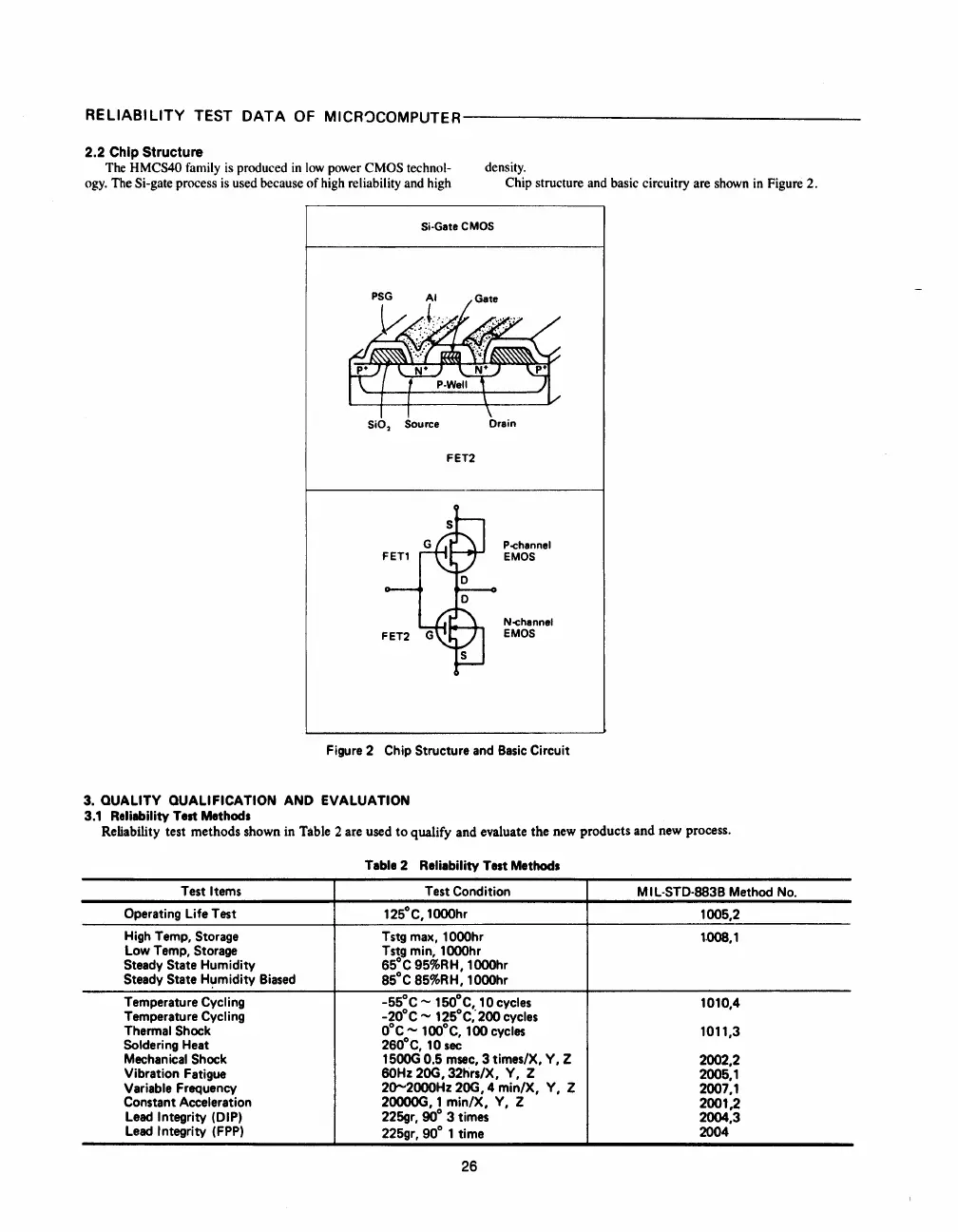

2.2 Chip Structure

density.

The

HMCS40 family

is

produced

in

low

power CMOS technol-

ogy. The Si-gate process

is

used because

of

high reliability and high Chip structure and basic circuitry are shown in Figure 2.

Si·Gate CMOS

SiO.

Source Drain

FET2

P<hannel

EMOS

N<hennel

EMOS

Figure 2 Chip Structure and

Basic

Circuit

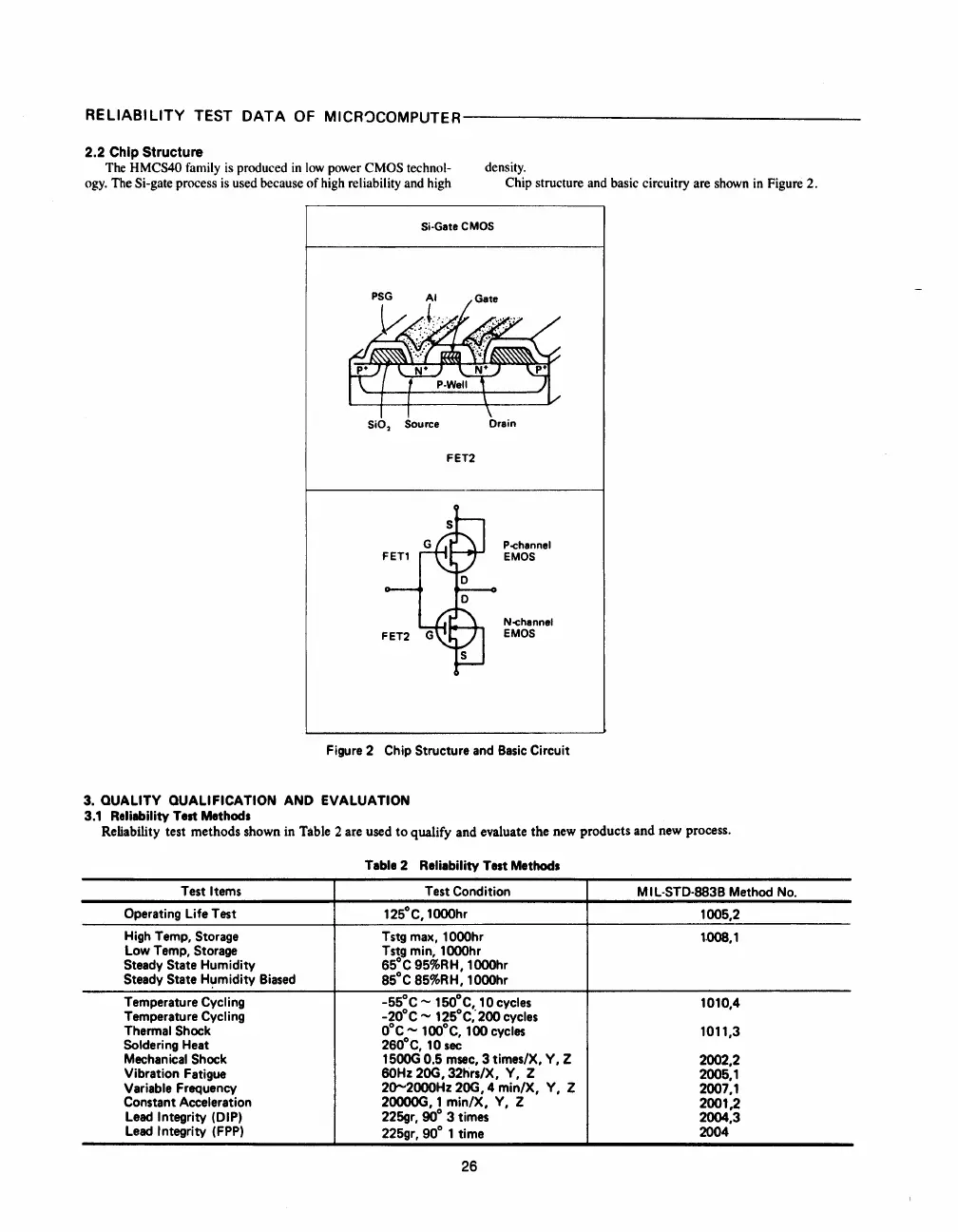

3. QUALITV QUALIFICATION AND EVALUATION

3.1 Reliability Test Methods

Reliability test methods shown in Table 2 are used

to

qualify and evaluate the new products and new process.

Table 2 Reliability Test Methods

Test Items Test Condition

MIL·STD·883B Method

No.

Operating Life Test 12SoC,1000hr

looS,2

High

Temp, Storage

Tstg max, 1000hr

1.008,1

Low Temp, Storage

Tstg min,

l000hr

Steady State Humidity

6SoC 9S%RH,

l000hr

Steady State

H~midity

Biased 8SoC 8S%RH,

l000hr

Temperature Cycling

-SSoC - 150°C, 10 cycles

1010,4

Temperature Cycling

-20°C""

12

S

oC,'2oo cycles

Thermal

Shock

O°C"" 100°C, 100 cycles

1011,3

Soldering Heat

260°C, 10 sec

Mechanical Shock

lSooo

0.5 msec, 3 times/X, V, Z

2002,2

Vibration Fatigue

60Hz

200,

32hrs/X, V, Z

2005,1

Variable Frequency

2o-2000Hz

200,

4 minIX, V, Z

2007,1

Constant Acceleration

20000G,1 min/X,

V,

Z

2001,2

Lead Integrity (DIP) 225gr, 90° 3 times

2004.3

Lead Integrity (FPP)

22Sgr,900 1 time

2004

26

Loading...

Loading...