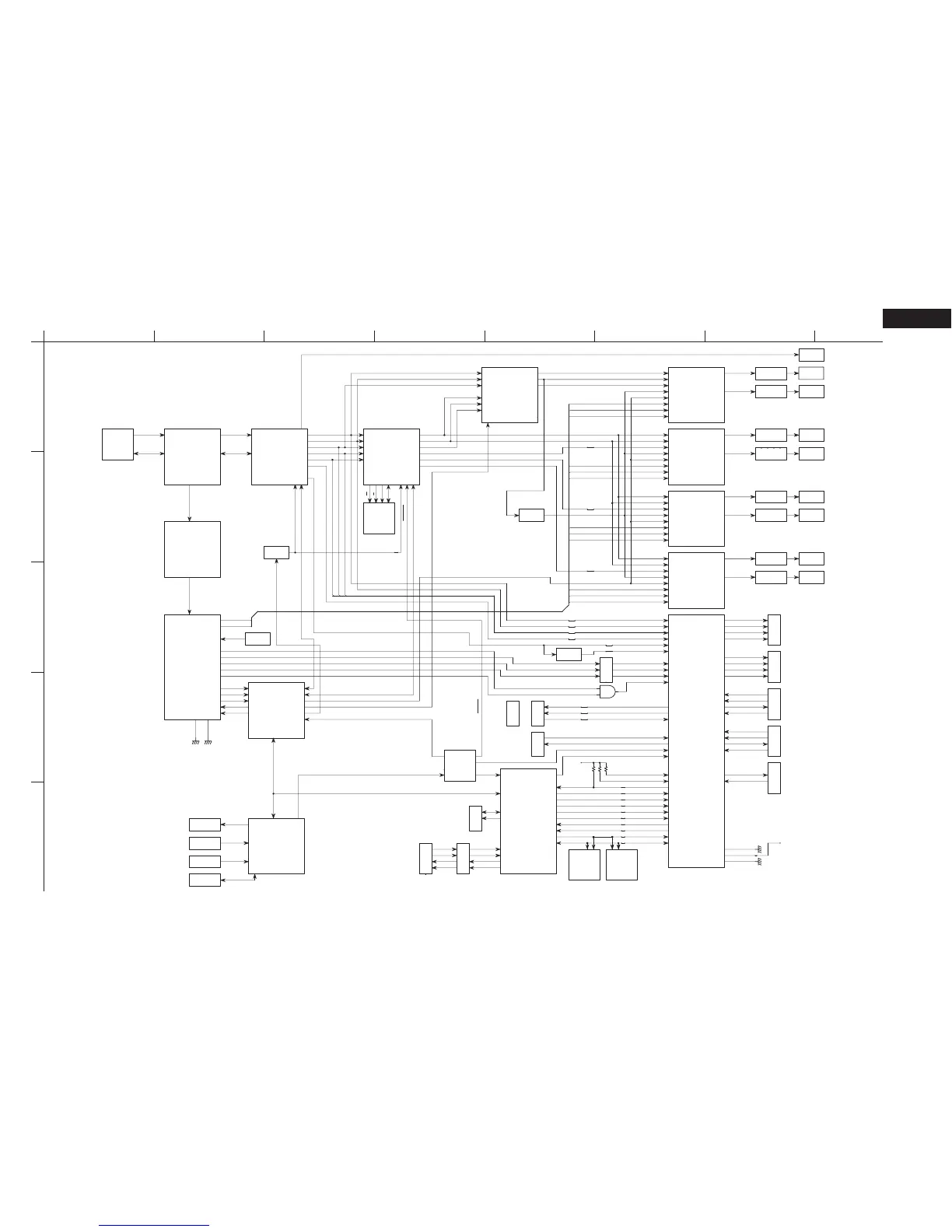

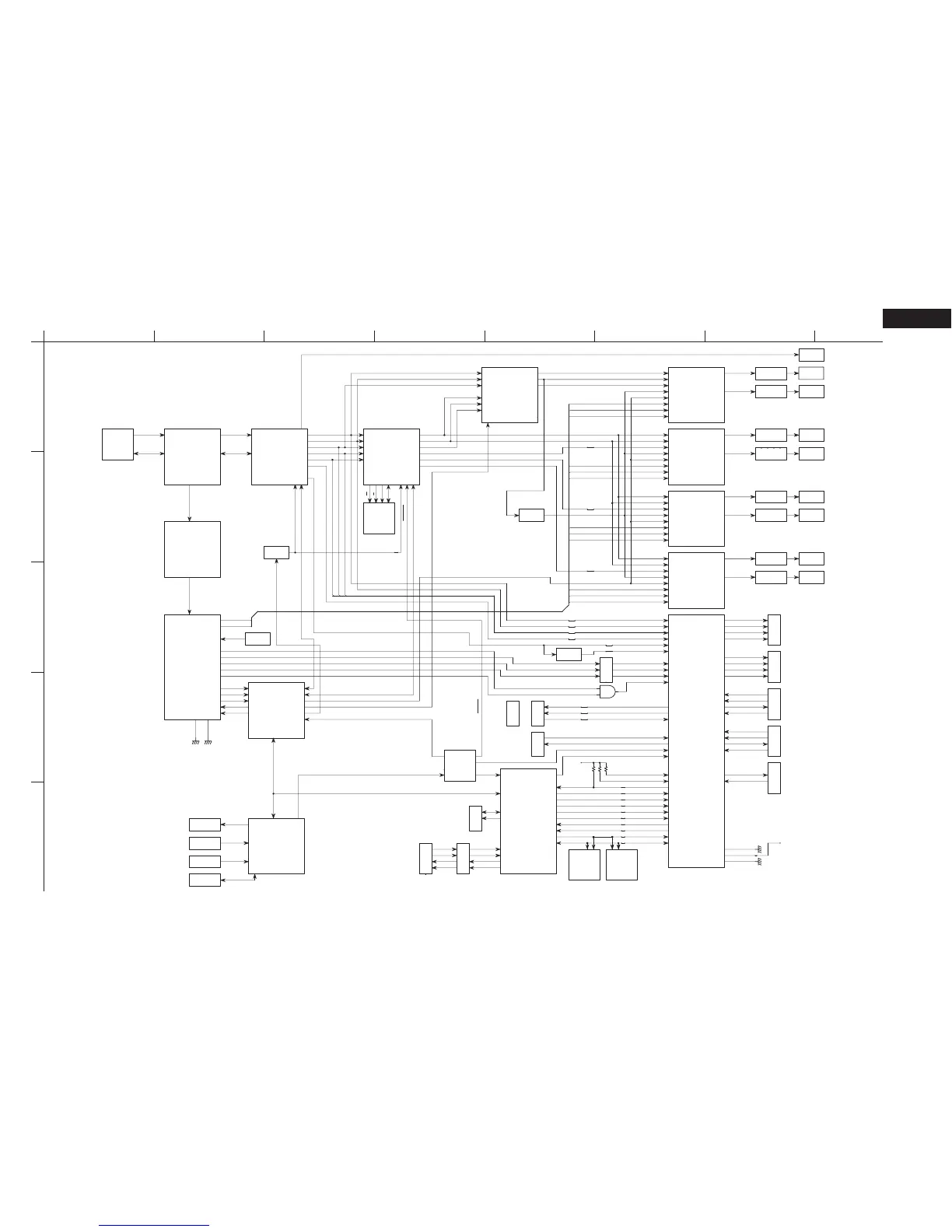

DV-SP1000

BLOCK DIAGRAM-5

AUDIO SECTION-2

A

1

2

3

4

5

BCDEFGH

UART

PORT

JTAG

PORT

JTAG

PORT

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

AUDIO

FILTER

RS-232C

I/O_PORT

RS-232C

CONTROLER

IEEE1394

PORT-1

IEEE1394

PORT-2

RI_IN/OUT

IR

KEY_INPUT

DISPLAY

AUDIO

LINE_OUT

AUDIO

LINE_OUT

SPDIF

OUT

MASTER

CLOCK

E2PROM

FOR CONFIG.

DAC_PLL

AUDIO

LINE_OUT

AUDIO

LINE_OUT

AUDIO

LINE_OUT

AUDIO

LINE_OUT

AUDIO

LINE_OUT

AUDIO

LINE_OUT

XTAL

24.576MHZ

BU2370FV

NJU7093A

DIR

AK4112B

EXT.PLL

TLC2932

BUFFER

74VHC541

XTAL

33.8688MHZ

10K

10K

10K

ICELYNX_IEEE1394

TSB43CA43A

TC7SH08FU

1

2

3

CONTROL_CPU

FOR_IEEE1394

SACD-DECODER

CXD2753R

FLASH-ROM

SRAM

RESET

CONTROL

DVD

MECHANIZM

2M_SRAM

MPEG-DECODER

M65776

AUDIO_DAC

C/LFE

AUDIO_DAC

FL/FR

AUDIO_DAC

DOWNMIX_LCH/RCH

AUDIO_DAC

SL/SR

21MUX

TC74VCX157

AUDIO_DSP

BASS_MANAGEMENT

FL/KEY_CONTROLER

FOR_DVD

SYSTEM_CONTROLER

FOR_DVD

SACD-I/F_PLD

FRONT-END

DOUT1

BCLK BCLK BCLK FL

LRCK LRCK LRCK

AO1 SDATA1 SDATA1

FR

BCLK

LRCK DSD_DATA1[LDATA]

SDO1 DSD_DATA2[RDATA]

DSD_SCLK

DATA BD[7..0] BCLK BCLK BCLK SL

LRCK LRCK LRCK

AO1 SDO1 SDATA2

CONTROL

CONTROL AO2 SDO2 SR

AOD SDO3

AAD SDOD DSD_DATA3[LDATA]

192/176.4KHZ_SW DSD_DATA4[RDATA]

DSD_SCLK

LRCK

RD

WR

AD

DA

DOUT0

C

VDT[7..0]

ACLKI[256FS]

MPEG_CONTROL

SDATA3

MCLK[256/128FS] LFE

MCKI[256FS]

XRST[DSP]

HCLK/HCS/HDIN/HDOUT/HACN

DSD_DATA5[LDATA]

DSD_DATA6[RDATA]

DSD_SCLK

DMXL

SDATA4

DMXR

CLOCK_SELECT

BCLK CDATA/CLATCH/CCLK

LRCK DSD_DATA7[LDATA]

SD[7..0]

DSD_DATA8[RDATA]

DSD_SCLK

DSA[7..0] MLPCM_BCLK[64FS] TPA0P

BCKAO MLPCM_LRCLK TPA0N

MLPCM_D[2..0] TPB0P

MCKI MLPCM_A[ANCILLARY] TPB0N

DOUT0 HSDI1_60958_IN

IBCK[128FS] HSDI1_AMCLK_IN

BCLK

IOUT[5..0] TPA1P

IANCO HSDI1_D[5..0] TPA1N

IFRM HSDI1_D6[ANCILLARY] TPB1P

IOUTE[64FS] HSDI1_SYNC TPB1N

HSDI1_CLK

MSDTAI

MSCK HCLK/HCS/HDIN/HDOUT/HACN JTAG_TCK

XMSLAT CDATA/CLATCH/CCLK JTAG_TDI

MSREADY 192/176.4KHZ_SW

XRST[DSP]

FIN-A REF_SYT JTAG_TDO

MADAT0 FIN-B DIV_VCO JTAG_TMS

SYSTEM_RESET VCO_OUT VCO_CLK

IFULL

IEMPTY

JTAG_TRST

XI XI ARM_JTAG_TDI

XO XO ARM_JTAG_TDO

I2C

RESET_Z ARM_JTAG_TMS

RESET_ARMZ

+3.3V

RESET_CONTROL MCIF_RW UART_TXD

MCIF_STRBZ UART_RXD

WAIT# MCIF_WAIT

I2C I2C CS0# MCIF_CS_IOZ

CS2# MCIF_CS_MEMZ

I2C

RD# MCIF_OEZ

SDA WE0# MCIF_WEZ

SCL CKIO MCIF_BUSCLK

IRQ1/IRL1# MCIF_INTZ

IRQ2/IRL2# WTCH_DG_TMRZ

A[10..0] MCIF_ADDR[10..1]

D[15..0] MCIF_DATA[15..0] +3.3V

CTS CTS MCIF_MODE2

RXD RXD MCIF_MODE1

RTS RTS MCIF_MODE0

TXD TXD

Loading...

Loading...