THE

80286

INSTRUCTION SET

LOCK-Assert

BUS

LOCK

Signal

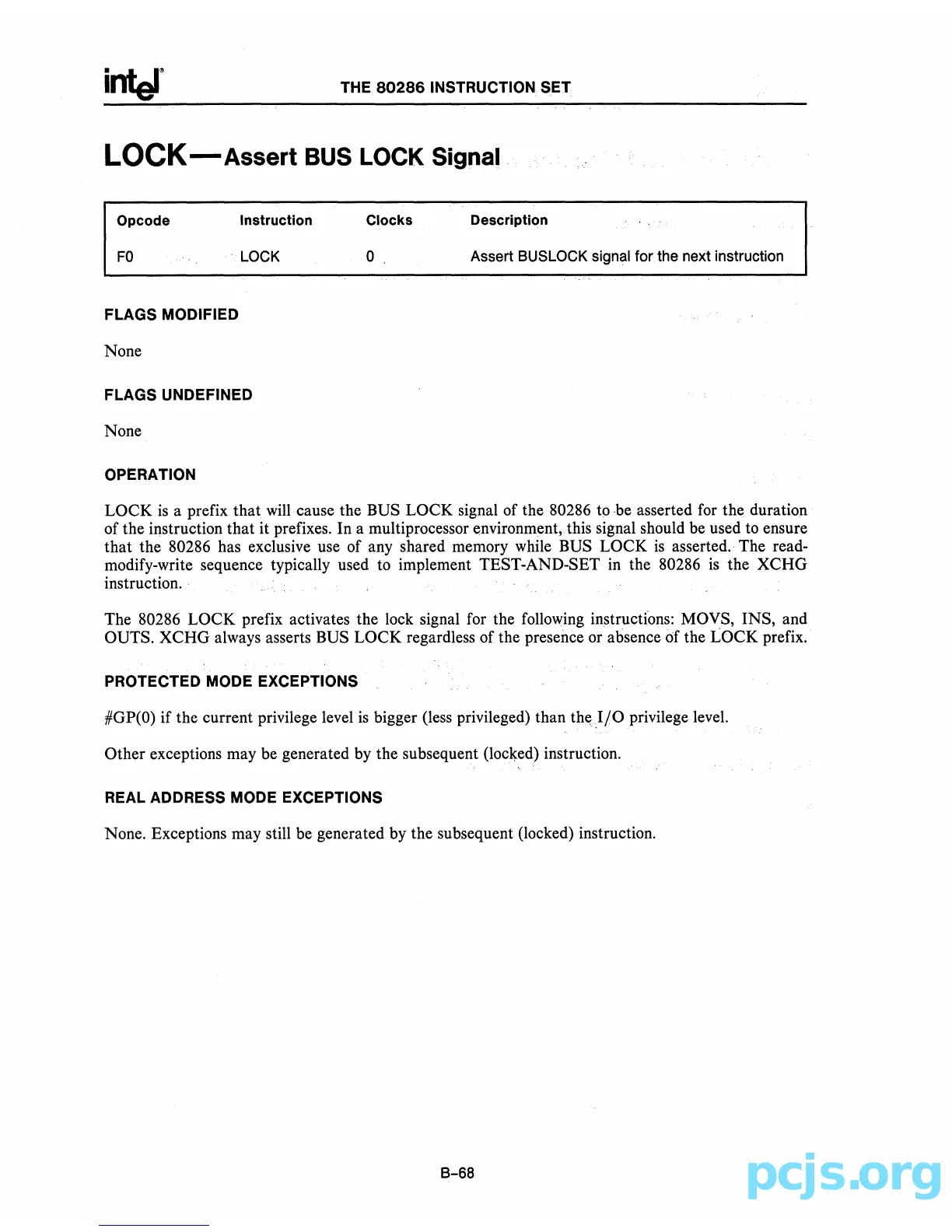

Opcode

Instruction Clocks Description

FO

LOCK o

Assert BUSLOCK signal

for

the next instruction

FLAGS MODIFIED

None

FLAGS UNDEFINED

None

OPERATION

LOCK

is

a prefix that

will

cause the BUS LOCK signal of the 80286 to

be

asserted

for

the duration

of the instruction that it prefixes. In a multiprocessor environment, this signal should

be

used

to

ensure

that the 80286 has exclusive use of any shared memory while BUS LOCK

is

asserted. The read-

modify-write sequence typically used

to

implement TEST-AND-SET

in

the 80286

is

the XCHG

instruction.

The 80286 LOCK prefix activates the lock signal for the following instructions: MOYS, INS, and

OUTS. XCHG always asserts BUS LOCK regardless of the presence or absence of the LOCK prefix.

PROTECTED MODE EXCEPTIONS

#GP(O)

if the current privilege level

is

bigger (less privileged) than the .I/O privilege level.

Other exceptions may

be

generated by the subsequent (locked) instruction.

REAL ADDRESS MODE EXCEPTIONS

None. Exceptions may still be generated

by

the subsequent (locked) instruction.

B-68

Loading...

Loading...