THE

80286

INSTRUCTION SET

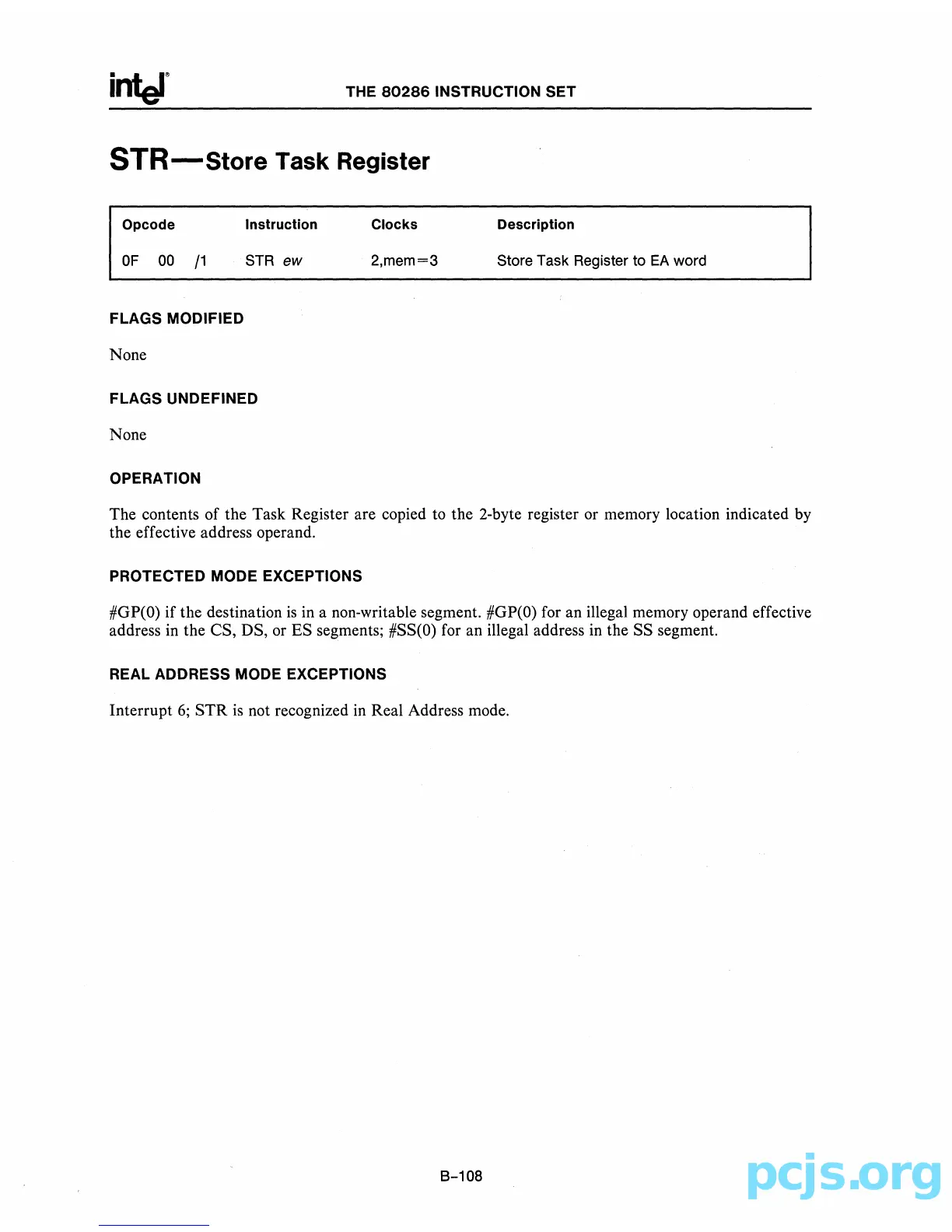

STR-Store

Task Register

Opcode

Instruction

Clocks

Description

OF

00

/1

STR ew 2,mem=3 Store Task Register to

EA

word

FLAGS MODIFIED

None

FLAGS UNDEFINED

None

OPERATION

The contents of the Task Register are copied to the 2-byte register or memory location indicated by

the effective address operand.

PROTECTED MODE EXCEPTIONS

#GP(O) if the destination

is

in a non-writable segment. #GP(O) for an illegal memory operand effective

address in the CS, DS, or ES segments;

#SS(O)

for an illegal address

in

the SS segment.

REAL ADDRESS MODE EXCEPTIONS

Interrupt

6;

STR

is

not recognized in Real Address mode.

8-108

Loading...

Loading...