MUL TIBUS® I AND

80386

1FITii

(FROM SLAVE

1

8205

INTERRUPT CONTROLLER)

8259A

~'b

MASTER

CASD

AD

,

CAS,

A,

07

INfA

CAS2

A2

74S30

CASVALlD(1J

E1

1:2

~J

r174S00

~::~

74ALS58D

I'

A2D-AD

STB

P

I(

UM+lO

Df'

OE

MBSEU

2

)

SYSB IllES!!

MU~W:SS®

<

)

DECODE

'"

AEN

-

82289

BUS

74S00

ARBITER

fI'IfA

MCE

.....

CENL

SELECT

CMDLY

<=

......

VC::r:

CENL

liEN

I-

M8

LOCALMB~

MBfO'3I

ALE

)

BUS

MIlO

CONTROLLER _

WAIT·STATE

82288

GENERATOR

BUS

+-

READY

CONTROLLER

ARDYEN

AI!DY

XACK

210760·113

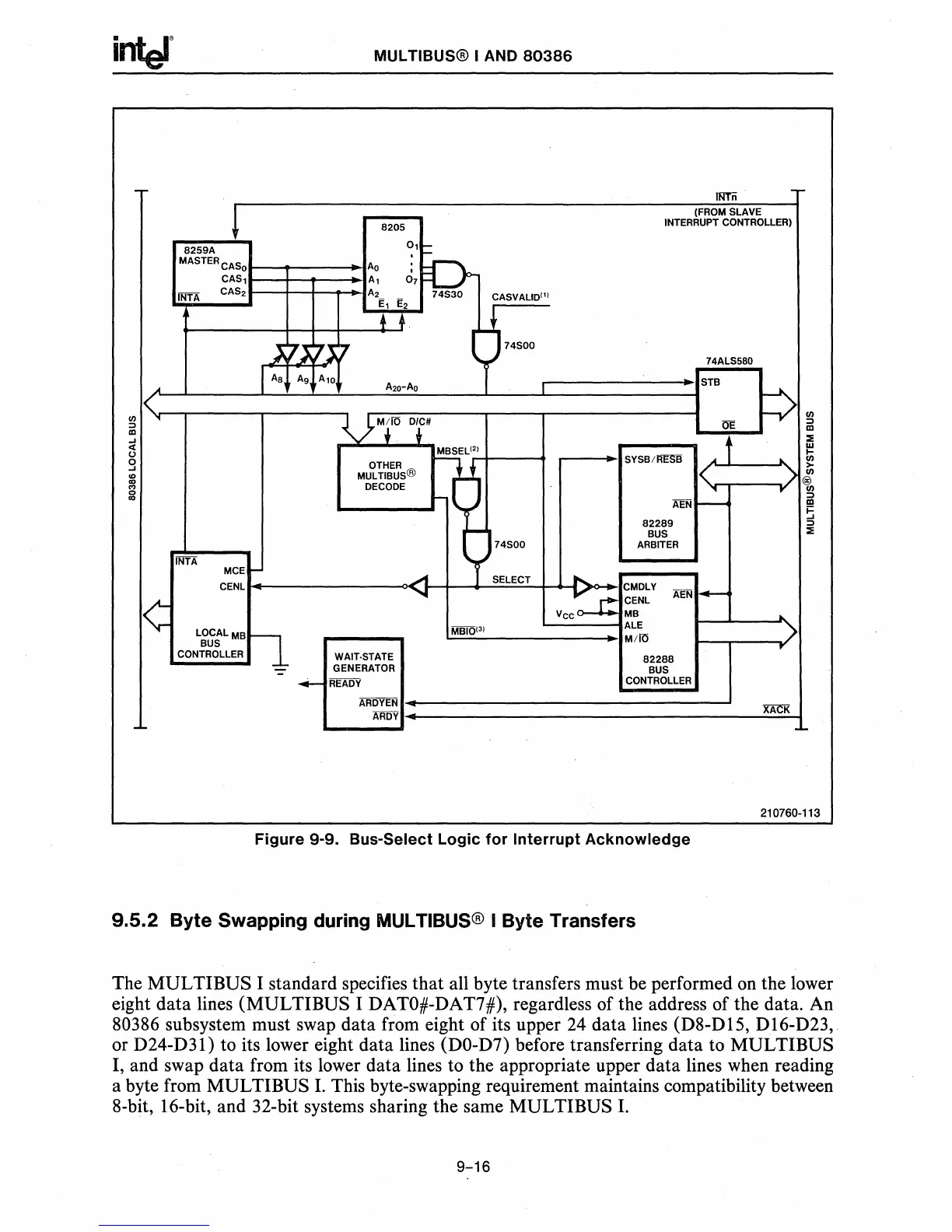

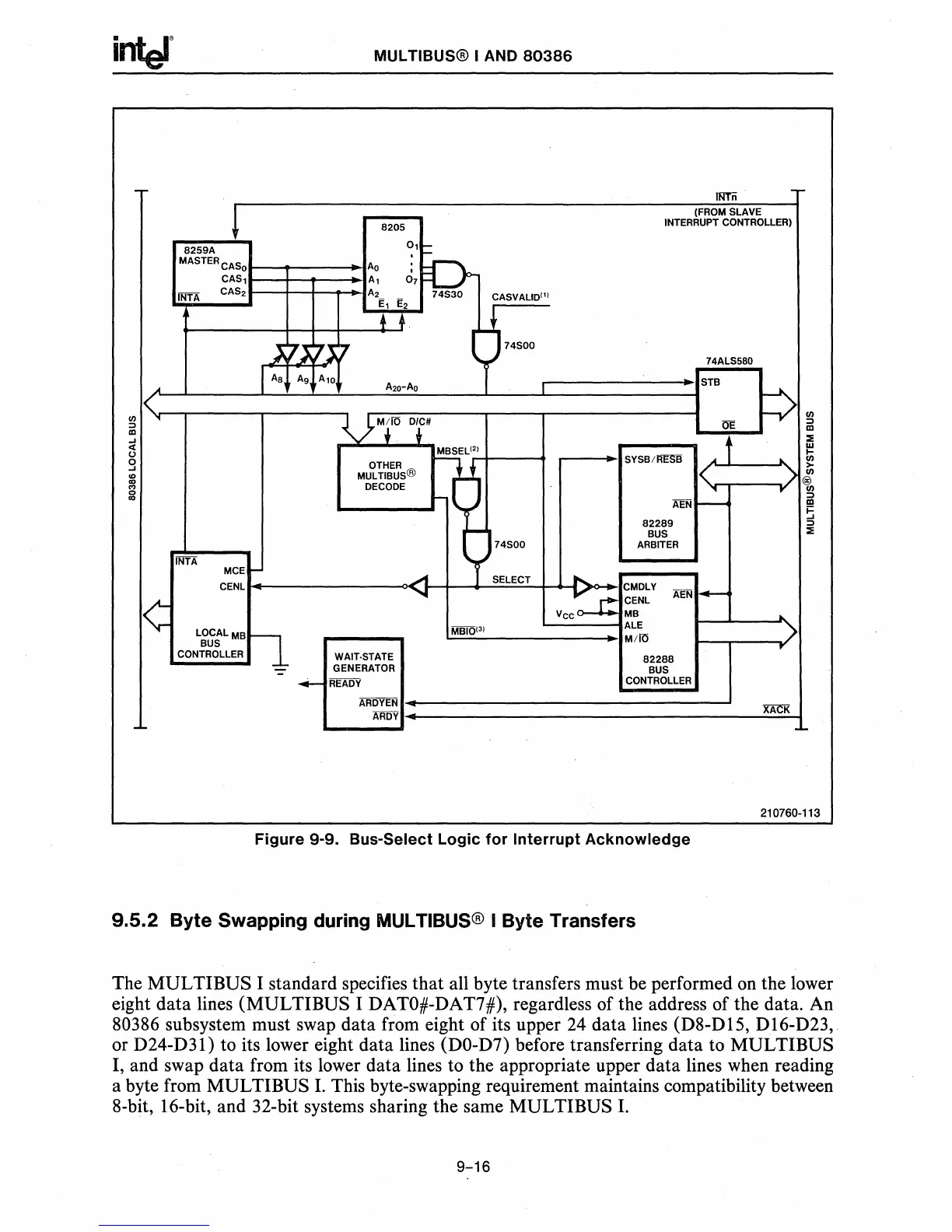

Figure

9-9. Bus-Select

Logic

for

Interrupt

Acknowledge

9.5.2

Byte

Swapping during

MUL

TIBUS® I

Byte

Transfers

The

MUL

TIBUS I standard specifies

that

all byte transfers must be performed on the lower

eight data lines (MULTIBUS I DATO#-DAT7#), regardless of the address

of

the data. An

80386 subsystem must swap data from eight

of

its upper

24

data lines (D8-DI5, DI6-D23,

or D24-D31) to its lower eight data lines (DO-D7) before transferring data to MULTIBUS

I, and swap data from its lower data lines to the appropriate upper data lines when reading

a byte from

MUL

TIBUS

1.

This byte-swapping requirement maintains compatibility between

8-bit, I6-bit, and 32-bit systems sharing the same MULTIBUS

1.

9-16

Loading...

Loading...