TEST CAPABILITIES

TOEAX

G30107

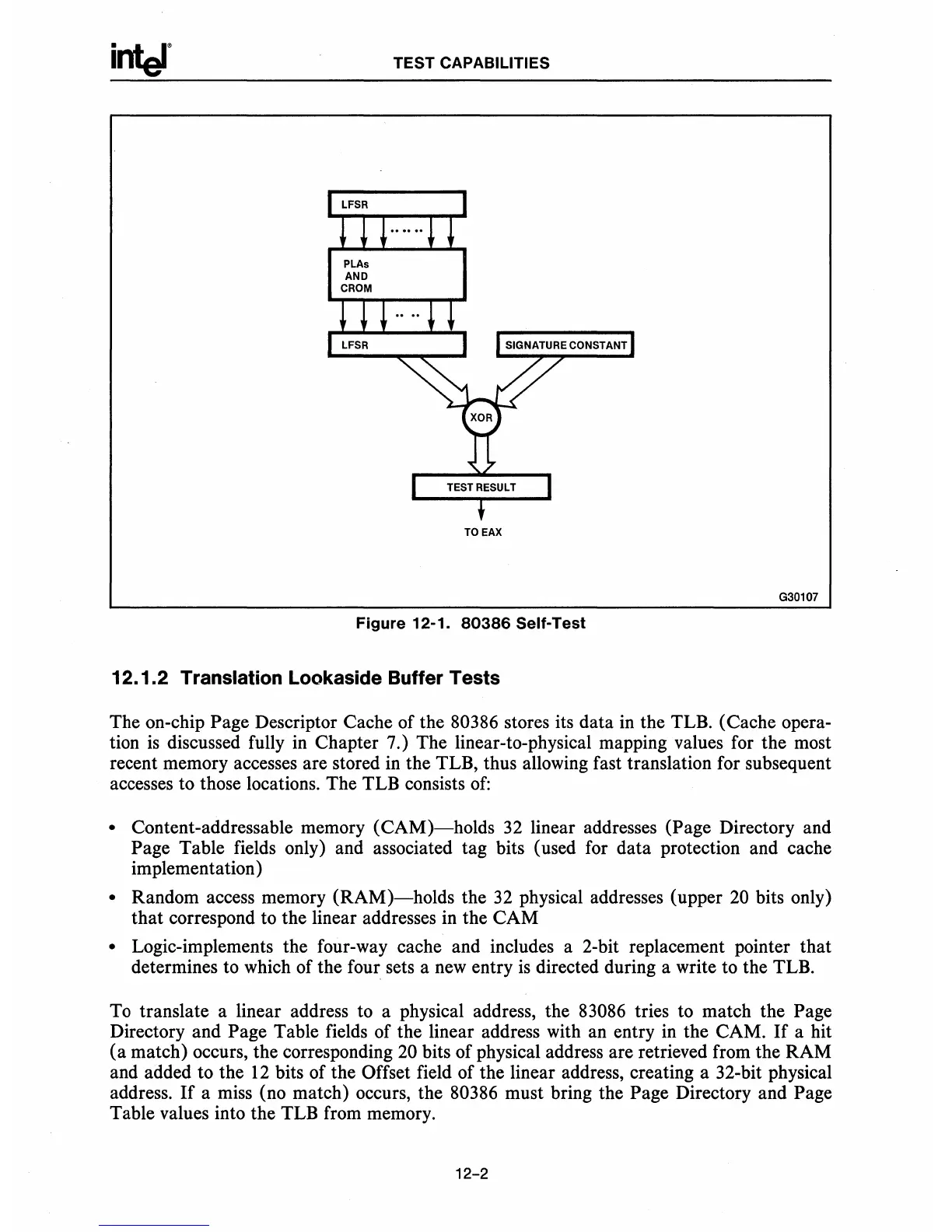

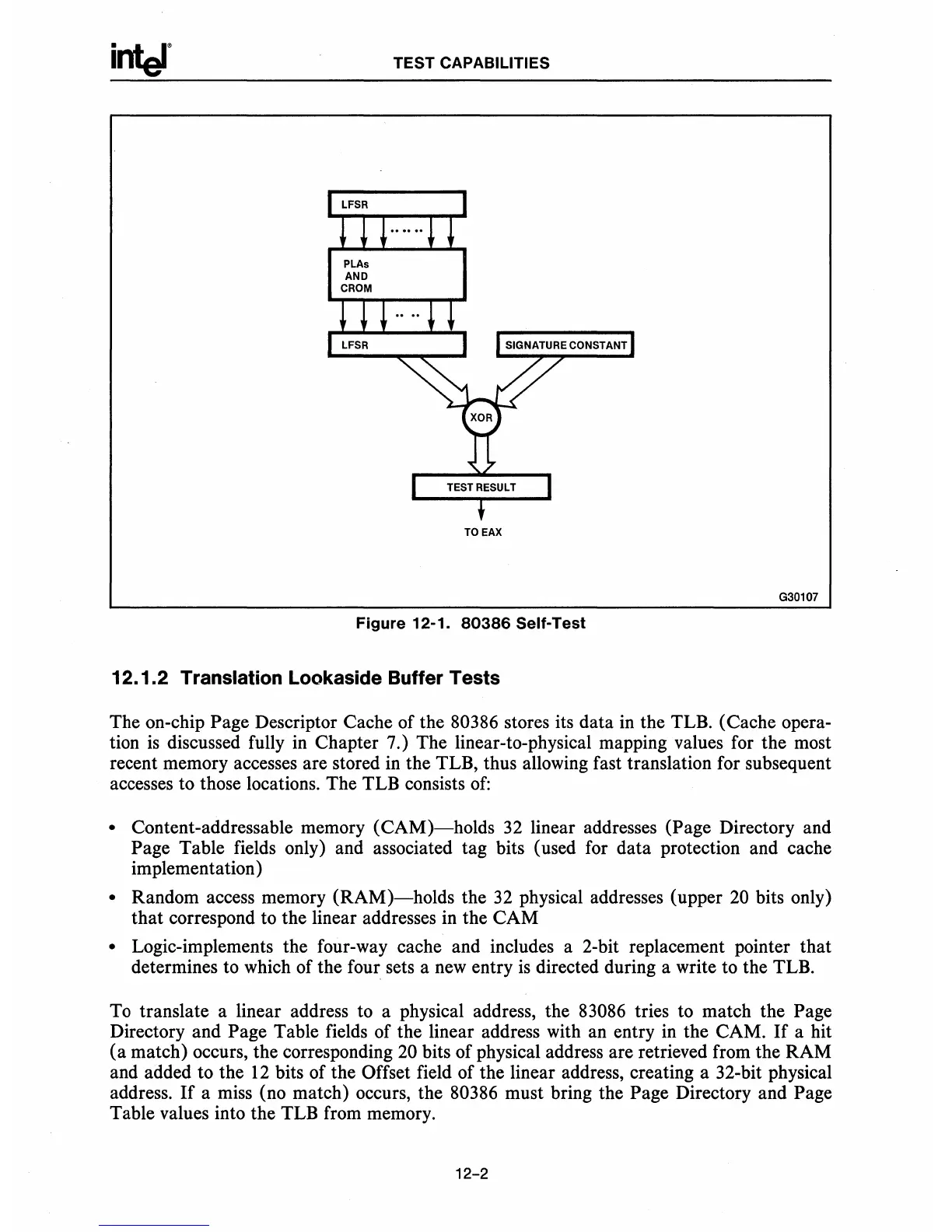

Figure

12-1.

80386

Self-Test

12.1.2 Translation Lookaside Buffer Tests

The on-chip

Page Descriptor Cache of the 80386 stores its data

in

the TLB. (Cache opera-

tion

is

discussed fully in Chapter 7.) The linear-to-physical mapping values for the most

recent memory accesses are stored in the TLB, thus allowing fast translation for subsequent

accesses to those locations. The TLB consists

of:

• Content-addressable memory

(CAM)-holds

32

linear addresses (Page Directory and

Page Table fields only) and associated tag bits (used for data protection and cache

implementation)

• Random access memory

(RAM)-holds

the

32

physical addresses (upper

20

bits only)

that correspond to the linear addresses in the CAM

• Logic-implements the four-way cache and includes a 2-bit replacement pointer that

determines to which of the four sets a new entry

is

directed during a write to the TLB.

To translate a linear address to a physical address, the

83086 tries to match the Page

Directory and Page Table fields of the linear address with an entry in the CAM.

If

a hit

(a

match) occurs, the corresponding 20 bits of physical address are retrieved from the RAM

and added to the

12

bits of the Offset field of the linear address, creating a 32-bit physical

address.

If

a miss (no match) occurs, the 80386 must bring the Page Directory and Page

Table values into the TLB from memory.

12-2

Loading...

Loading...