TEST CAPABILITIES

The 80386 provides an interface through which to test the TLB.

Two

32-bit test registers of

the

80386 are used

to

write and read the contents of the TLB through the MOV TREG, reg

and

MOV reg, TREG instructions. An 80386 program can be used to generate test patterns

which are applied to the TLB through automatic test machines or assembly language

programs.

The paging mechanism of the

80386 must be disabled during a test of the TLB. The internal

response

is

therefore not identical to that of normal operation, but the main functionality of

the TLB can be verified.

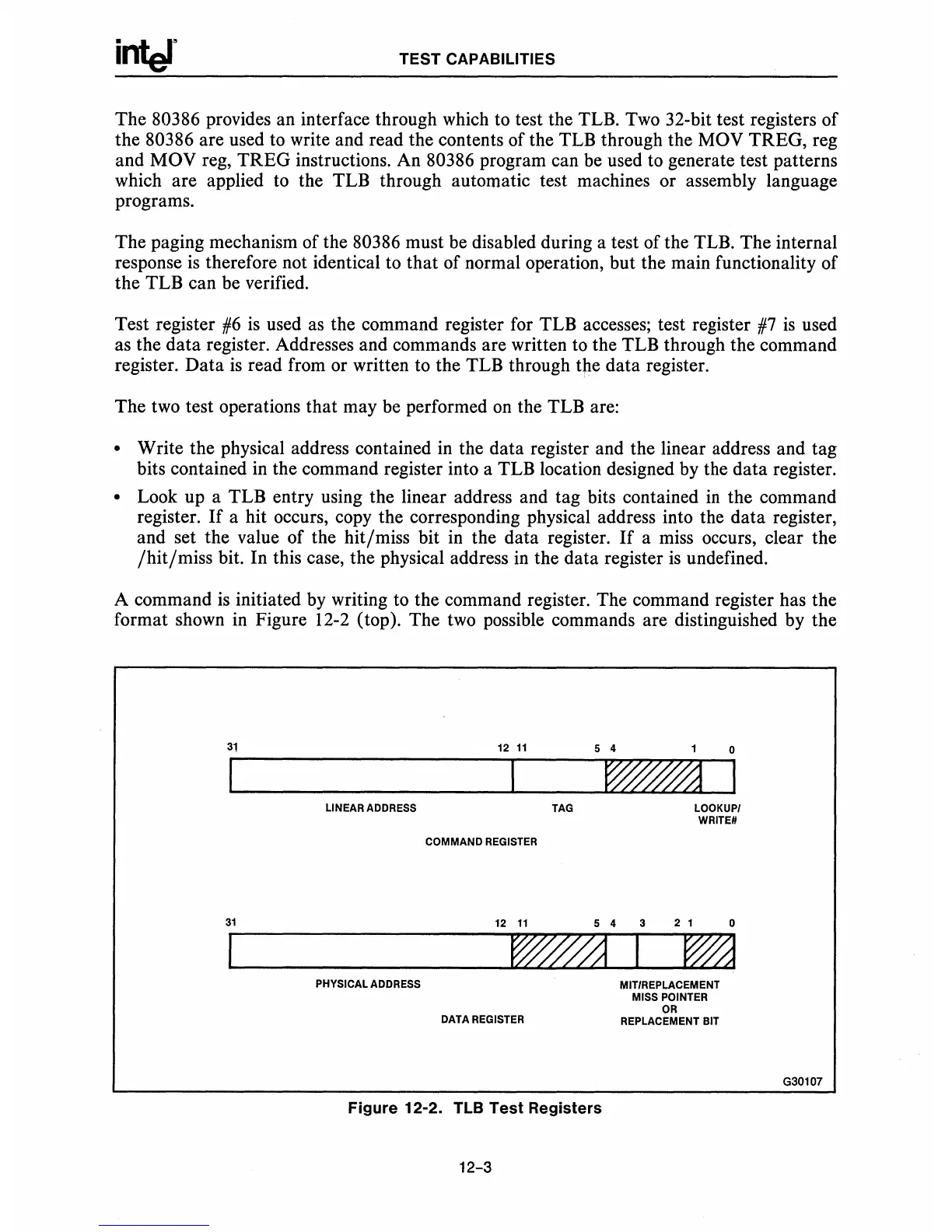

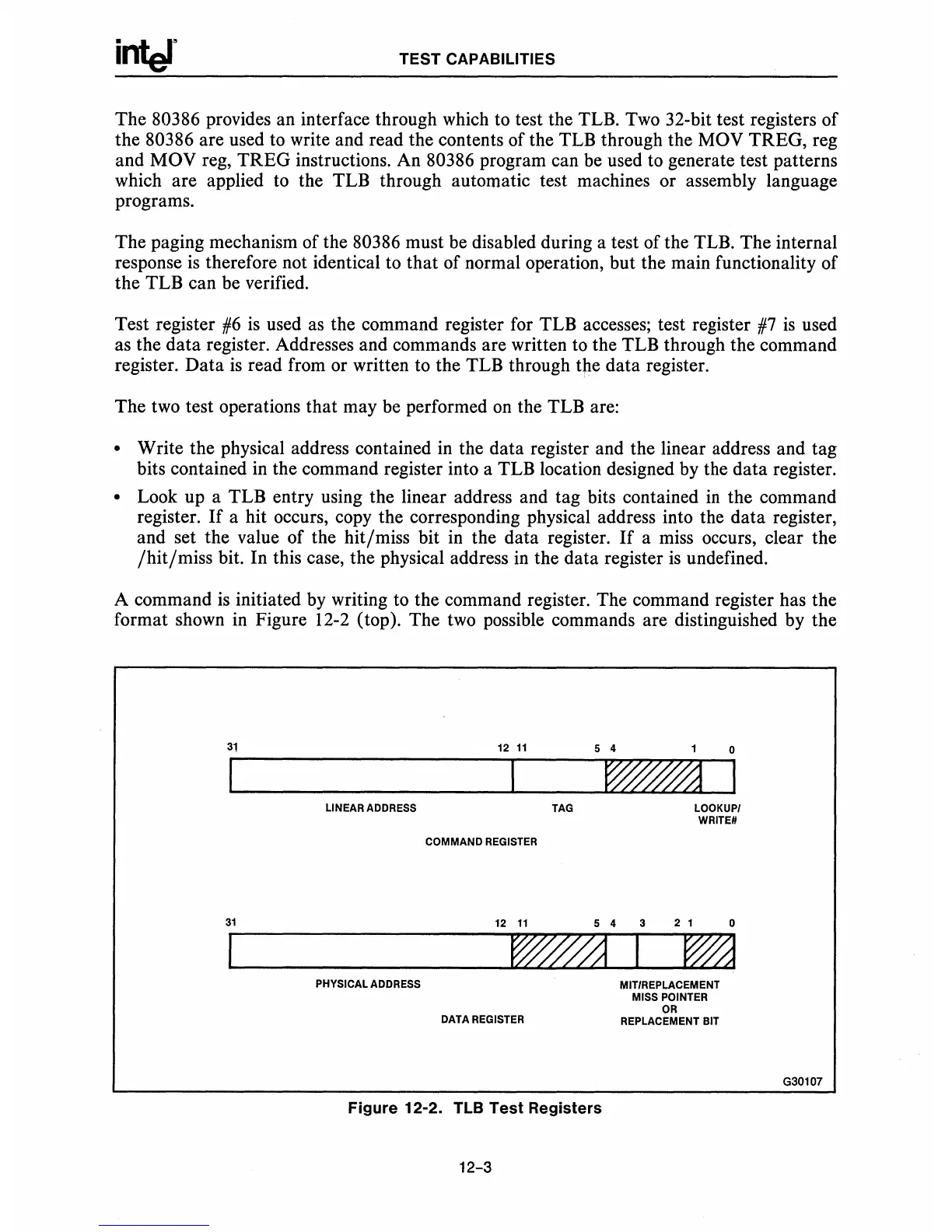

Test register

#6

is

used

as

the command register for TLB accesses; test register

#7

is

used

as

the data register. Addresses and commands are written to the TLB through the command

register. Data

is

read from or written to the TLB through the data register.

The two test operations that may be performed

on

the TLB are:

• Write the physical address contained

in

the data register and the linear address and tag

bits contained

in

the command register into a TLB location designed by the data register.

• Look up a TLB entry using the linear address and tag bits contained

in

the command

register.

If

a hit occurs, copy the corresponding physical address into the data register,

and set the value of the hit/miss bit

in

the data register.

If

a miss occurs, clear the

/hit/miss

bit. In this case, the physical address

in

the data register

is

undefined.

A command

is

initiated

by

writing to the command register. The command register has the

format shown

in

Figure 12-2 (top). The two possible commands are distinguished by the

31

31

12

11

LINEAR ADDRESS

TAG

COMMAND

REGISTER

12

11

5 4

5 4

2 1

LOOKUP/

WRITE#

o

~I

PHYSICAL ADDRESS

DATA REGISTER

Figure 12-2. TLB

Test

Registers

12-3

MIT/REPLACEMENT

MISS POINTER

OR

REPLACEMENT BIT

G30107

Loading...

Loading...