DRAM

PAL

DESCRIPTIONS

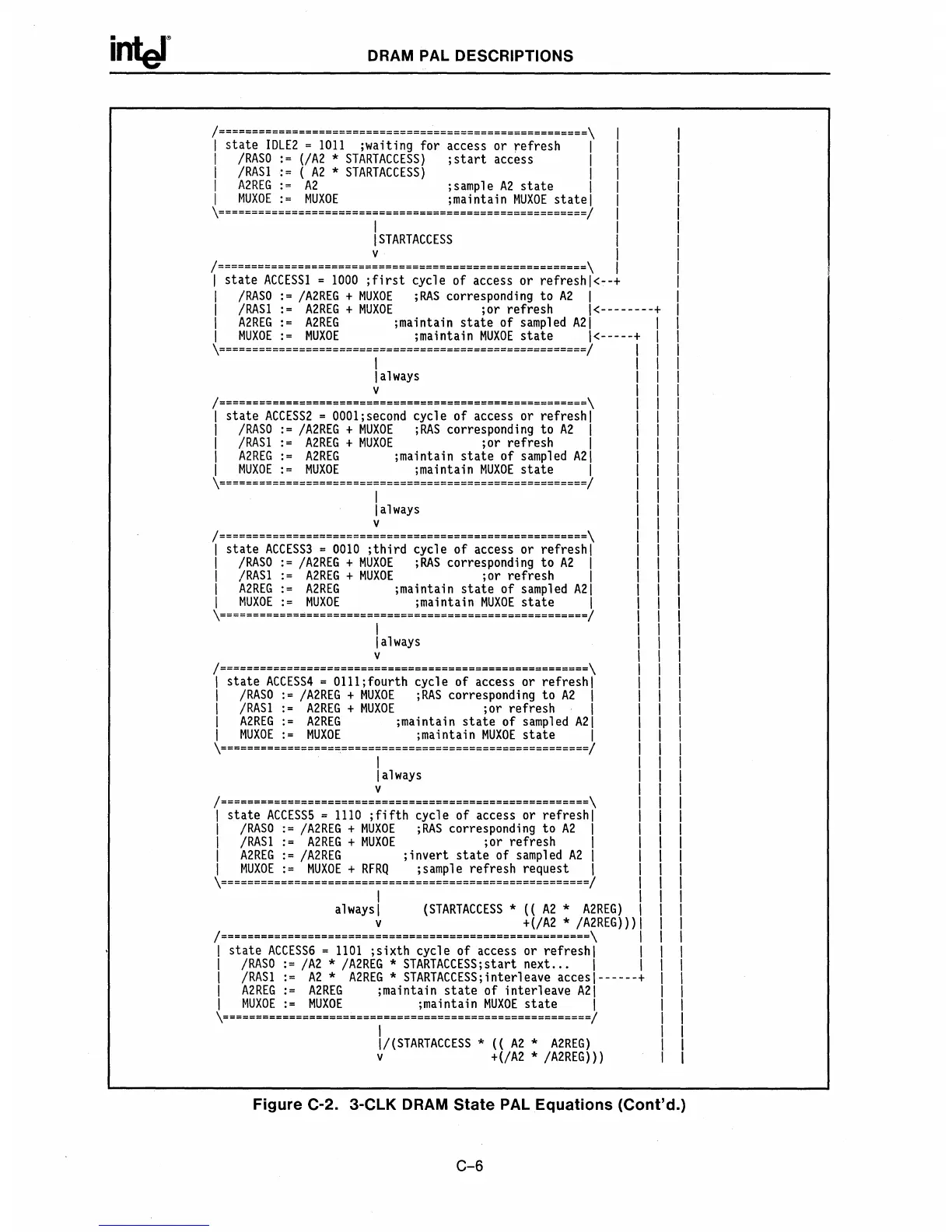

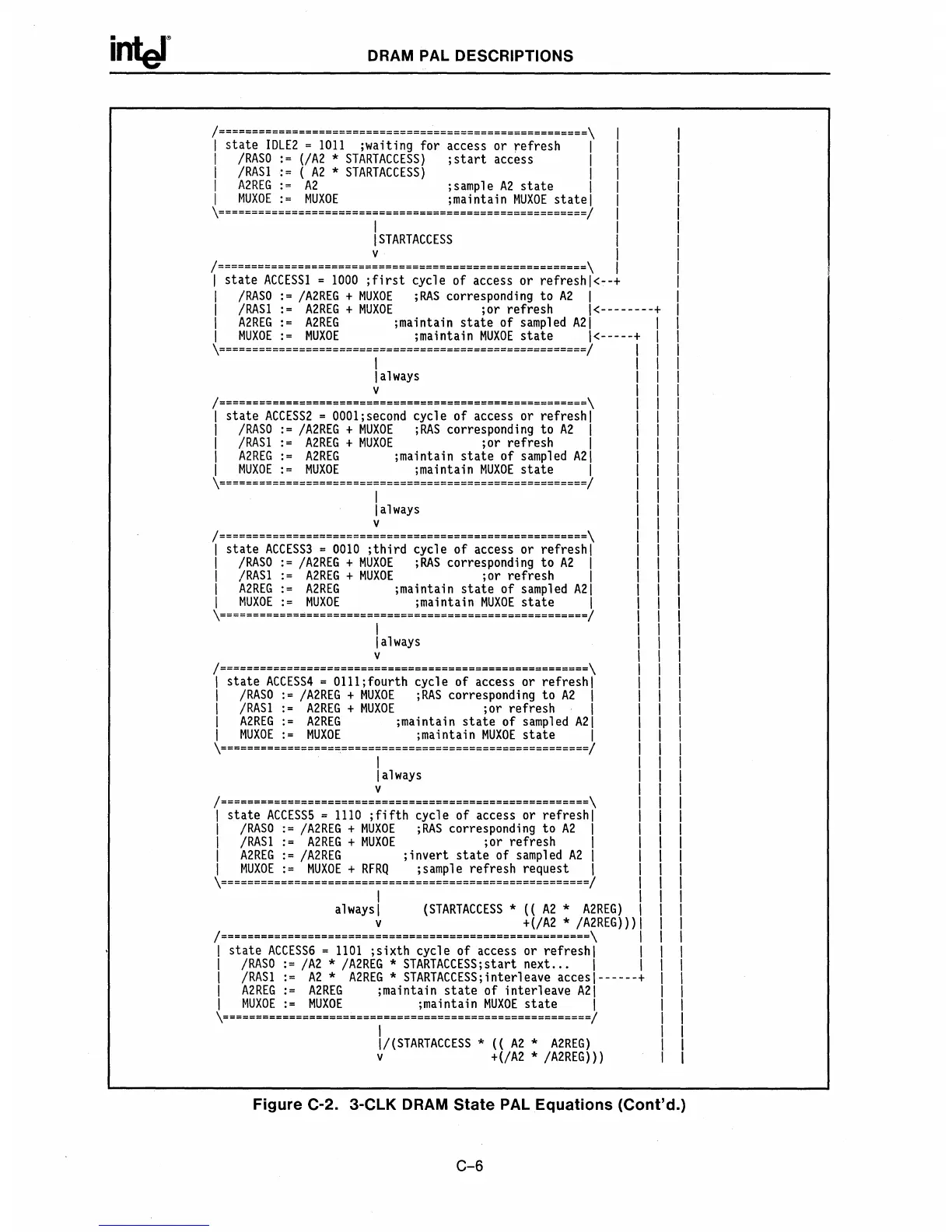

1=====================================================

==\

I

I

state

IDLE2 =

1011

;wa

it

i

ng

for

access

or

refresh

I I

I

IRASO:=

UA2

*

STARTACCESS)

;start

access I I

I

IRASl:=

(

A2

*

STARTACCESS)

I I

I

A2REG:=

A2

;sample

A2

state

I I

I MUXOE:=

MUXOE

;maintain

MUXOE

state

I I

\=====================================================

==1

I

I I

I

STARTACCESS

I

v I

1=====================================================

==\

I

state

ACCESSI

= 1000

;first

cycle

of

access

or

refreshl<--+

lRASO

: =

IA2REG

+

MUXOE

;

RAS

correspondi

ng

to

A2

I

lRASl

:=

A2REG

+

MUXOE

;or

refresh

1<--------+

I A2REG:=

A2REG

;maintain

state

of

sampled

A21

I MUXOE:=

MUXOE

;maintain

MUXOE

state

1<-----+

\=====================================================

==1

I

I always

v

1=====================================================

==\

I

state

ACCESS2

= 0001 ;second

cycle

of

access

or

refresh

I

I

lRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASl:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:=

A2REG

;maintain

state

of

sampled

A21

I MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

==1

I

I always

v

I ====a=====_============================================ \

I

state

ACCESS3

- 0010

;third

cycle

of

access

or

refresh

I

I

lRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASl:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:=

A2REG

;maintain

state

of

sampled

A21

I MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

=-1

I

I always

v

1=====================================================

==\

I

state

ACCESS4

=

011l;fourth

cycle

of

access

or

refresh

I

I

IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASl:

=

A2REG

+

MUXOE

;

or

refresh

I

I

A2REG:=

A2REG

;maintain

state

of

sampled

A21

I MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

==1

I

I always

v

I ======================================================= \

I

state

ACCESS5

= 1110

;fifth

cycle

of

access

or

refresh

I

I

IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASl:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:=

IA2REG

;

invert

state

of

sampled

A2

I

I MUXOE:=

MUXOE

+

RFRQ

;sample

refresh

request

I

\=====================================================

==1

I

always I

(STARTACCESS

* «

A2

*

A2REG)

v

+UA2

* IA2REG)))

1=====================================================

==\

I

state

ACCESS6

= 1101

;sixth

cycle

of

access

or

refresh

I

I

lRASO:=

IA2

*

IA2REG

* STARTACCESS;start

next...

I

I

IRASl:=

A2

*

A2REG

*

STARTACCESS;

interleave

acces

1------+

I A2REG:=

A2REG

;maintain

state

of

interleave

A21

I MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

==1

I

I/(STARTACCESS

* «

A2

*

A2REG)

v

+UA2

* IA2REG)))

Figure C-2. 3-CLK

DRAM

State

PAL

Equations (Cont'd.)

C-6

Loading...

Loading...