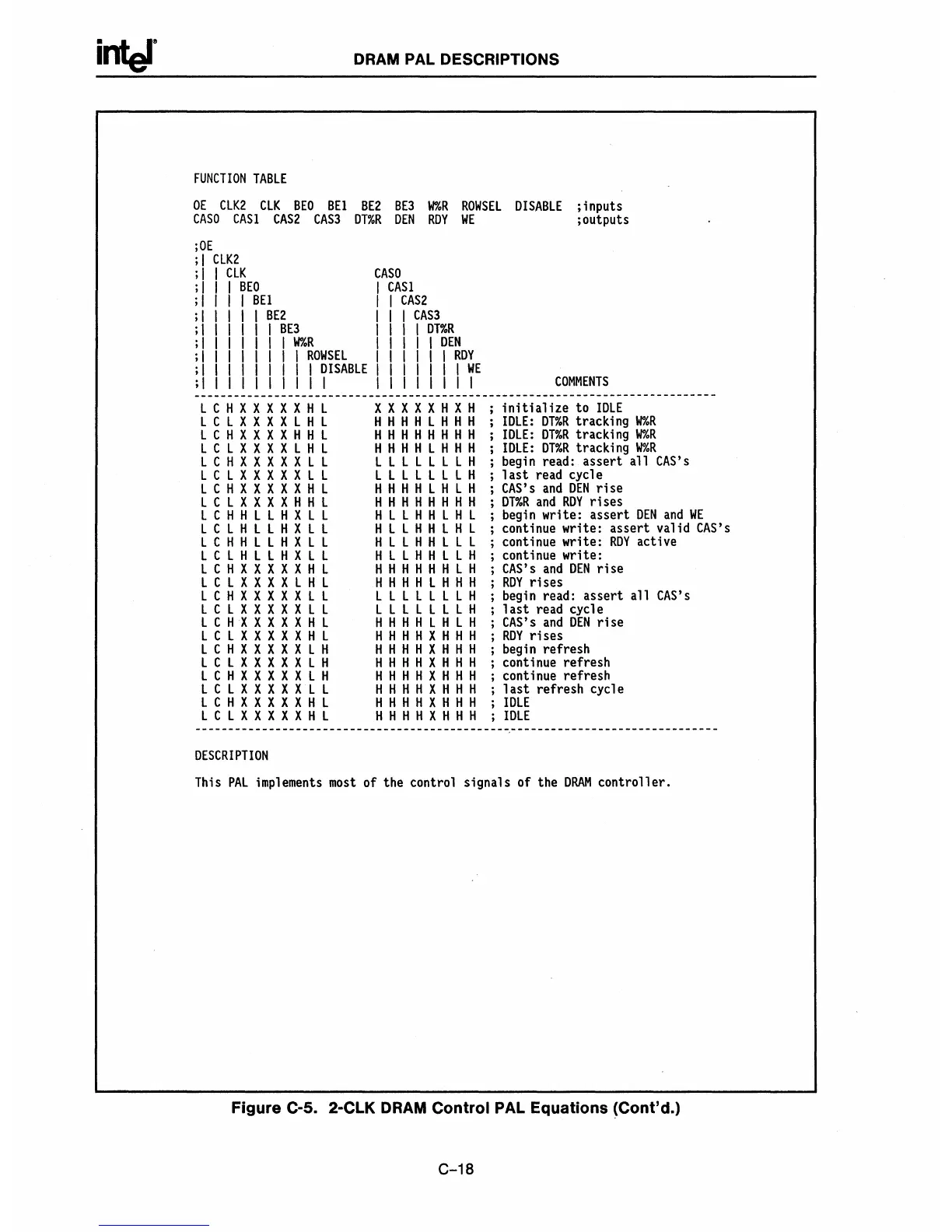

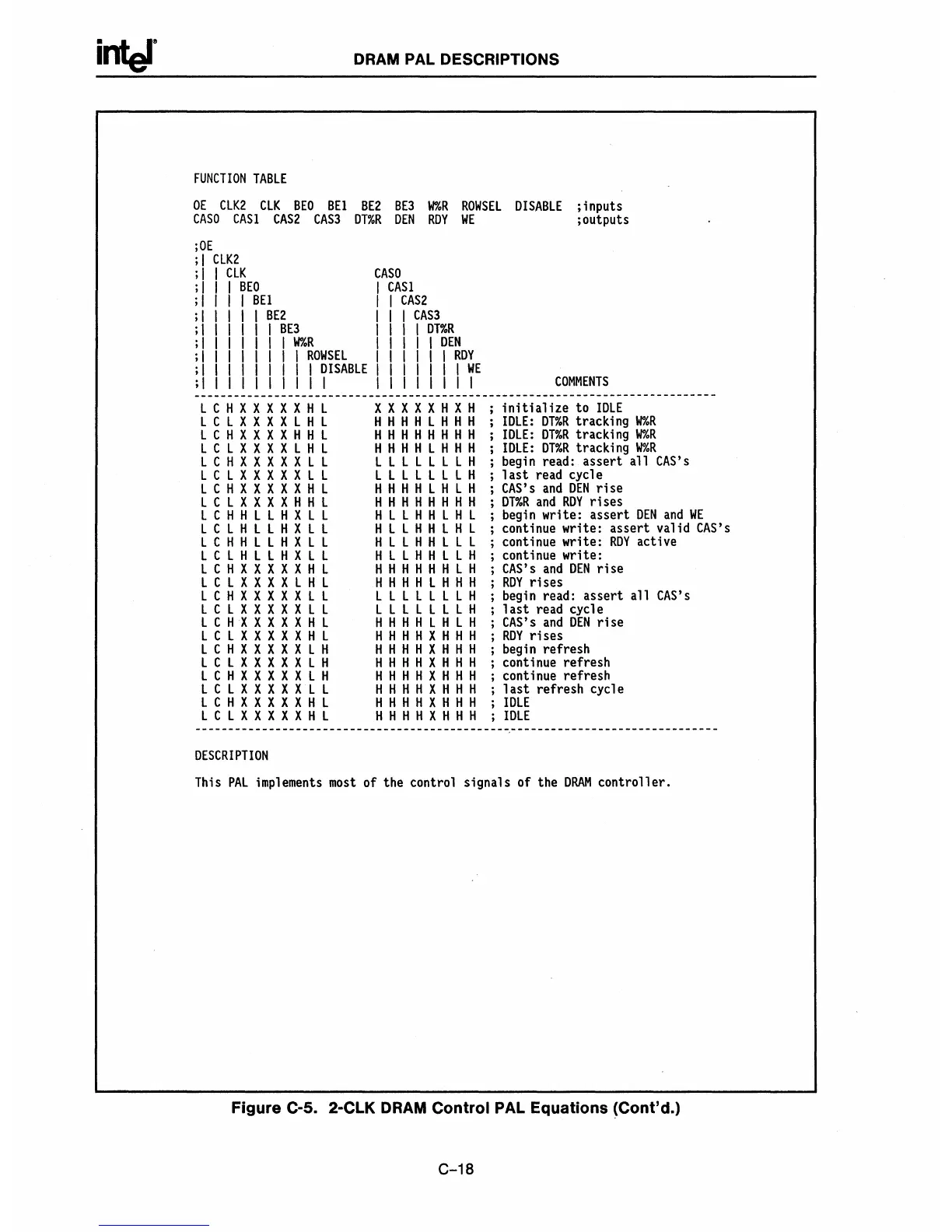

DRAM

PAL

DESCRIPTIONS

FUNCTION

TABLE

OE

CLK2

CLK

BEO

BEl

BE2

BE3

W%R

ROWSEL

DISABLE

;

inputs

CASO

CASl

CAS2

CAS3

DT%R

DEN

ROY

WE

; outputs

;OE

; 1

CLK2

; 1 1

CLK

CASO

; 1 1 1

BED

1

CASl

; 1 1

liBEl

1 1

CAS2

; 1 1 1 1 1

BE2

1 1 1

CAS3

; 1 1 1 1 1 1

BE3

1 1 1 1

DT%R

; 1 1 1 1 1 1 1

W%R

1 1 1 1 1

DEN

; 1 1 1 1 1 1 1 1

ROWSEL

1 1 1 1 1 1

ROY

; 1 1 1 1 1 1 1 1 1

DISABLE

1 1 1 1 1 1 1

WE

;1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

COMMENTS

LCHXXXXXHL

LCLXXXXLHL

L C H X X X X H H L

L

C L X X X X L H L

L

C H X X X X X L L

L

C L X X X X X L L

LCHXXXXXHL

LCLXXXXHHL

L C H H L L H X L L

L

C L H L L H X L L

L

C H H L L H X L L

L

C L H L L H X L L

LCHXXXXXHL

L C L X X X X L H L

L

C H X X X X X L L

L

C L X X X X X L L

L

C H X X X X X H L

L

C L X X X X X H L

L

C H X X X X X L H

L

C L X X X X X L H

L

C H X X X X X L H

L

C L X X X X X L L

L

C H X X X X X H L

LCLXXXXXHL

DESCRIPTION

x X X X X H X H ;

initialize

to

IDLE

H H H H L H H H ;

IDLE:

DT%R

tracking

W%R

H H H H H H H H ;

IDLE:

DT%R

tracking

W%R

H H H H L H H H ;

IDLE:

DT%R

tracking

W%R

L L L L L L L H ; begin read:

assert

all

CAS's

L L L L L L L H ;

last

read

cycle

H H H H L H L H ;

CAS's

and

DEN

rise

H H H H H H H H ;

DT%R

and

ROY

ri

ses

H L L H H L H L ; begin

write:

assert

DEN

and

WE

H L L H H L H L ; continue

write:

assert

valid

CAS's

H L L H H L L L ; continue

write:

ROY

active

H L L H H L L H ; continue

write:

H H H H H H L H ;

CAS's

and

DEN

ri

se

H H H H L H H H ;

ROY

ri

ses

L L L L L L L H ; begin read:

assert

all

CAS's

L L L L L L L H ; 1 ast read cycl e

H H H H L H L H ;

CAS's

and

DEN

rise

H H H H X H H H ;

ROY

ri

ses

H H H H X H H H ; begi n

refresh

H H H H X H H H ; continue

refresh

H H H H X H H H ; continue

refresh

H H H H X H H H ;

last

refresh

cycle

H H H H X H H H ;

IDLE

H H H H X H H H ;

IDLE

This

PAL

implements

most

of

the

control

signals

of

the

DRAM

controller.

Figure

CoS.

2-CLK DRAM Control PAL Equations (Cont'd.)

C-1B

Loading...

Loading...