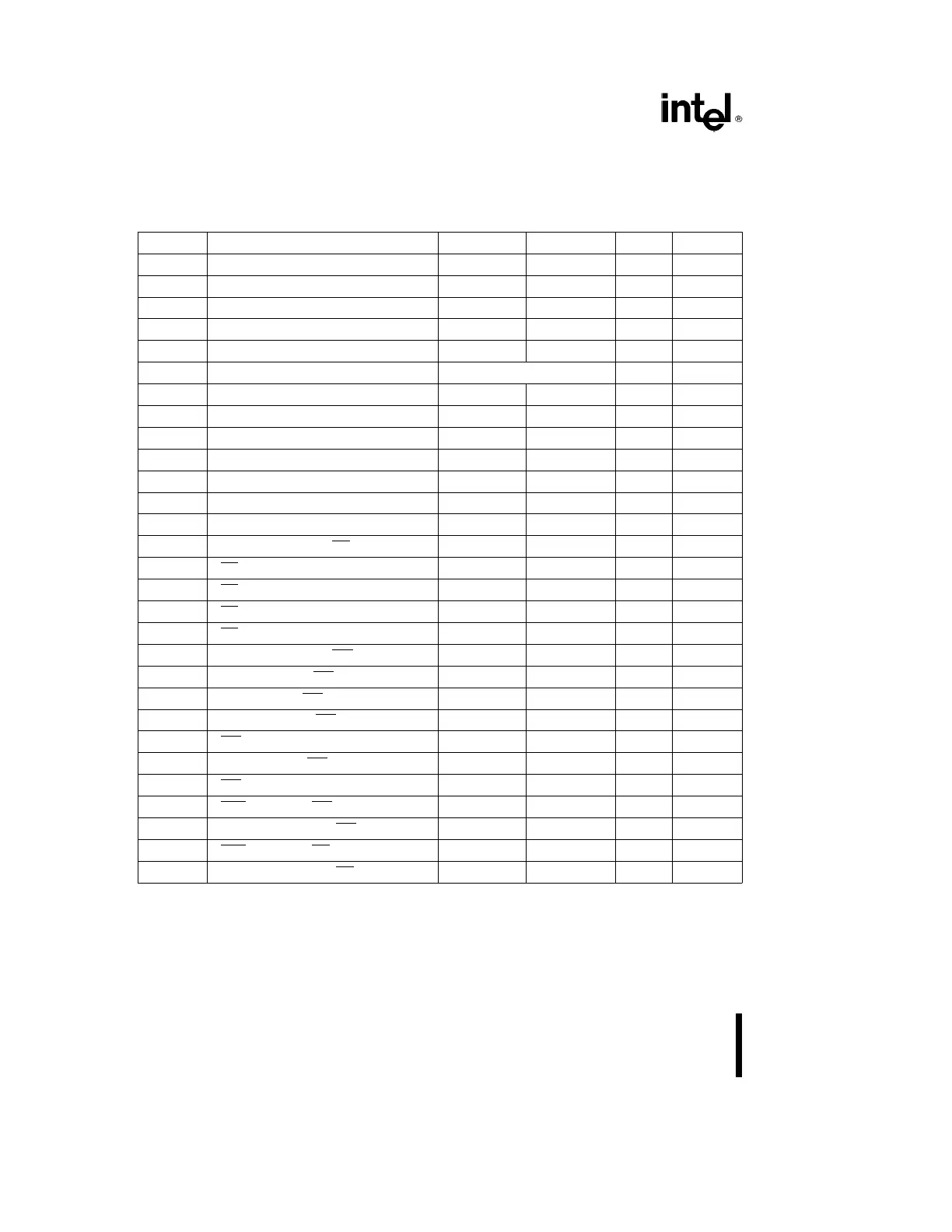

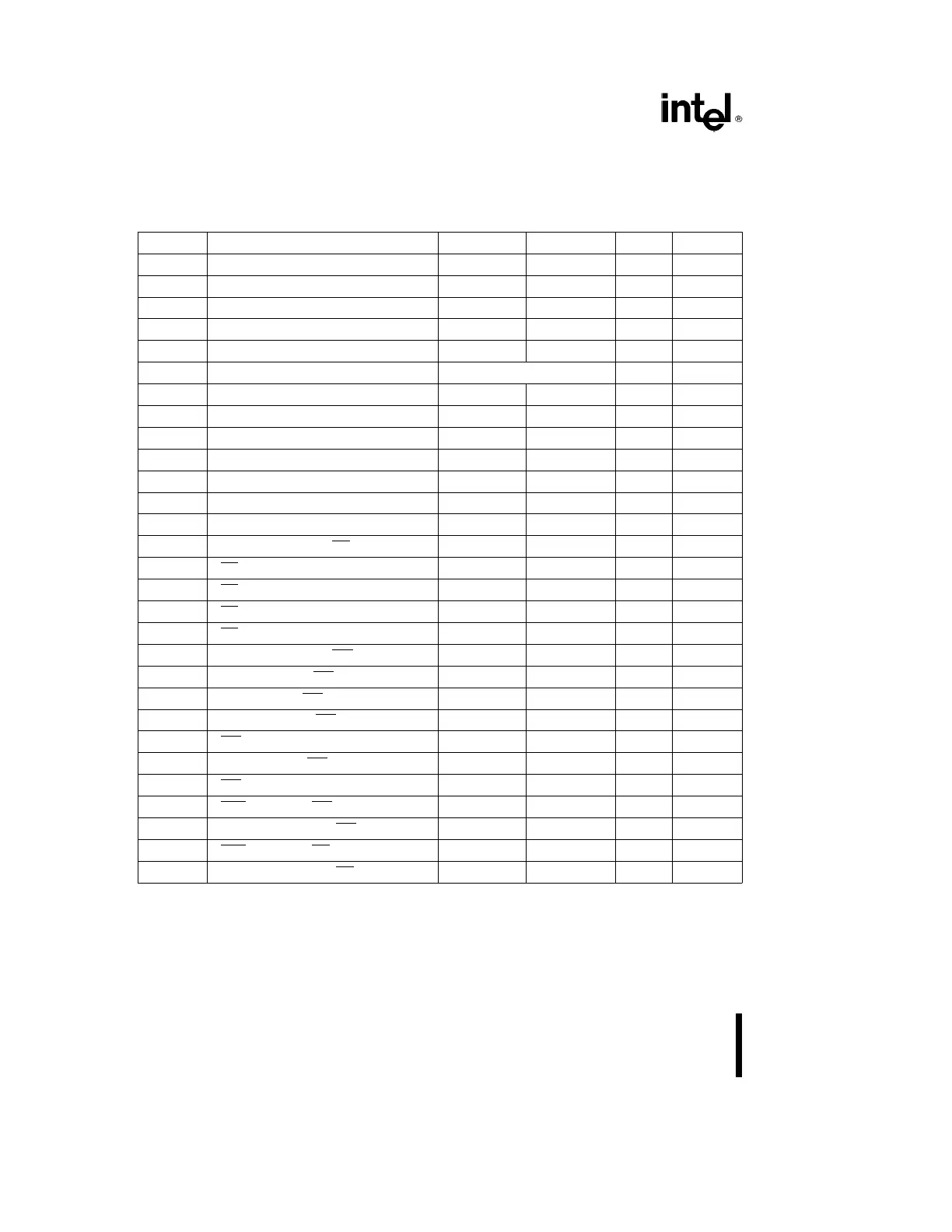

8XC196KC/8XC196KC20

AC CHARACTERISTICS (Continued)

For user over specified operating conditions.

Test Conditions: Capacitive load on all pins

e

100 pF, Rise and fall times

e

10 ns, F

OSC

e

16 MHz

The 80C196KC will meet these specifications:

Symbol Description Min Max Units Notes

F

XTAL

Frequency on XTAL1 (8XC196KC) 8 16 MHz (Note 1)

F

XTAL

Frequency on XTAL1 (8XC196KC20) 8 20 MHz (Note 1)

T

OSC

I/F

XTAL

(8XC196KC) 62.5 125 ns

T

OSC

I/F

XTAL

(8XC196KC20) 50 125 ns

T

XHCH

XTAL1 High to CLKOUT High or Low

a

20

a

110 ns

T

CLCL

CLKOUT Cycle Time 2 T

OSC

ns

T

CHCL

CLKOUT High Period T

OSC

b

10 T

OSC

a

15 ns

T

CLLH

CLKOUT Falling Edge to ALE Rising

b

5

a

15 ns

T

LLCH

ALE Falling Edge to CLKOUT Rising

b

20

a

15 ns

T

LHLH

ALE Cycle Time 4 T

OSC

ns (Note 4)

T

LHLL

ALE High Period T

OSC

b

10 T

OSC

a

10 ns

T

AVLL

Address Setup to ALE Falling Edge T

OSC

b

15

T

LLAX

Address Hold after ALE Falling Edge T

OSC

b

35 ns

T

LLRL

ALE Falling Edge to RD Falling Edge T

OSC

b

30 ns

T

RLCL

RD Low to CLKOUT Falling Edge

a

4

a

30 ns

T

RLRH

RD Low Period T

OSC

b

5 ns (Note 4)

T

RHLH

RD Rising Edge to ALE Rising Edge T

OSC

T

OSC

a

25 ns (Note 2)

T

RLAZ

RD Low to Address Float

a

5ns

T

LLWL

ALE Falling Edge to WR Falling Edge T

OSC

b

10 ns

T

CLWL

CLKOUT Low to WR Falling Edge 0

a

25 ns

T

QVWH

Data Stable to WR Rising Edge T

OSC

b

23 (Note 4)

T

CHWH

CLKOUT High to WR Rising Edge

b

5

a

15 ns

T

WLWH

WR Low Period T

OSC

b

20 ns (Note 4)

T

WHQX

Data Hold after WR Rising Edge T

OSC

b

25 ns

T

WHLH

WR Rising Edge to ALE Rising Edge T

OSC

b

10 T

OSC

a

15 ns (Note 2)

T

WHBX

BHE, INST after WR Rising Edge T

OSC

b

10 ns

T

WHAX

AD8– 15 HOLD after WR Rising T

OSC

b

30 ns (Note 3)

T

RHBX

BHE, INST after RD Rising Edge T

OSC

b

10 ns

T

RHAX

AD8– 15 HOLD after RD Rising T

OSC

b

25 ns (Note 3)

NOTES:

1. Testing performed at 8 MHz. However, the device is static by design and will typically operate below 1 Hz.

2. Assuming back-to-back bus cycles.

3. 8-Bit bus only.

4. If wait states are used, add 2 T

OSC

* N, where N

e

number of wait states.

12

Loading...

Loading...