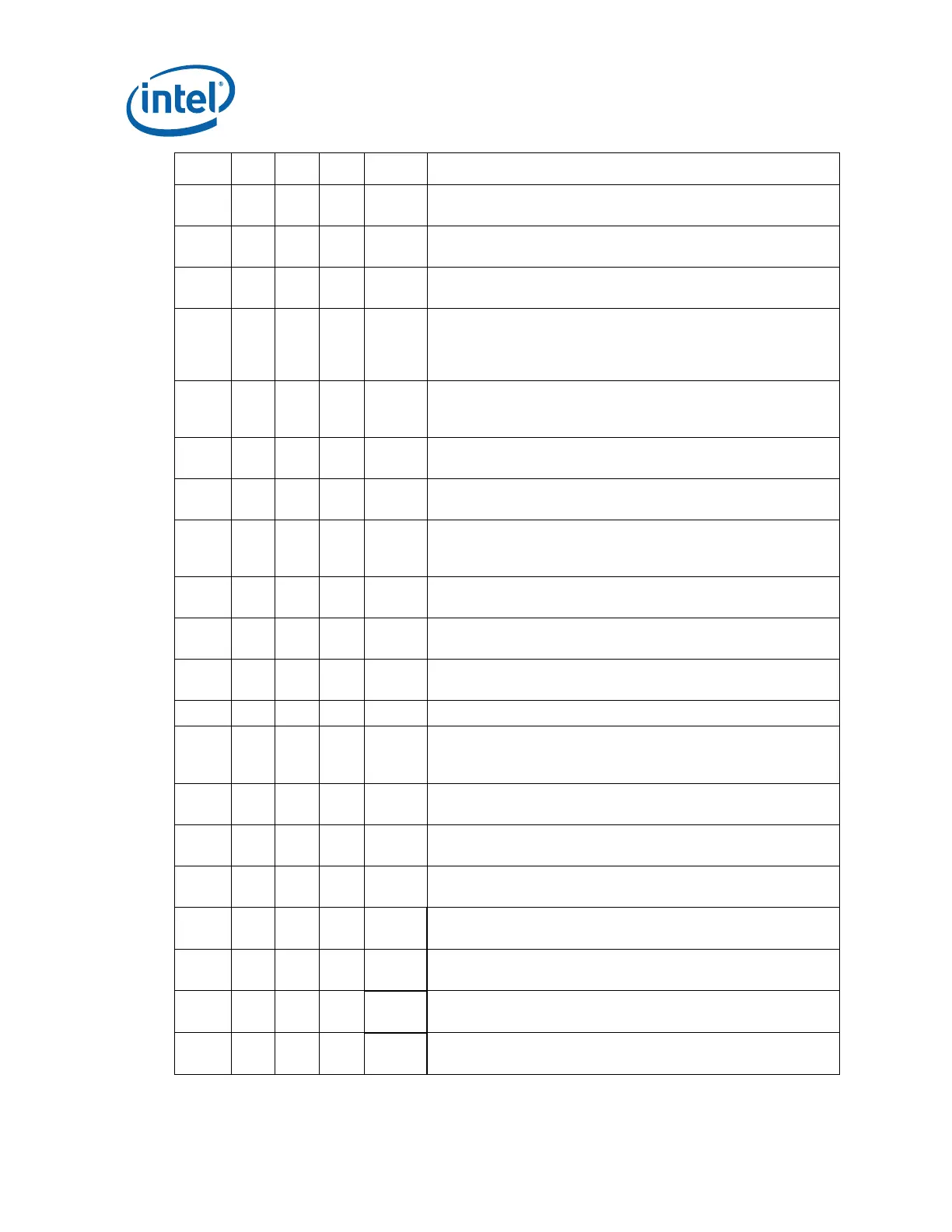

Summary Tables of Changes

10 Specification Update

NO B1 C1 D0 Plan ERRATA

AA10 X X X No Fix

BTS (Branch Trace Store) and PEBS(Precise Event Based

Sampling) May Update Memory outside the BTS/PEBS Buffer

AA11 X X X No Fix

Control Register 2 (CR2) Can be Updated during a REP

MOVS/STOS Instruction with Fast Strings Enabled

AA12 X X X No Fix

REP STOS/MOVS Instructions with RCX >=2^32 May Cause a

System Hang

AA13 X X X No Fix

A 64-Bit Value of Linear Instruction Pointer (LIP) May be

Reported Incorrectly in the Branch Trace Store (BTS) Memory

Record or in the Precise Event Based Sampling (PEBS) Memory

Record

AA14 X X X No Fix

Access to an Unsupported Address Range in Uniprocessor (UP)

or Dual-processor (DP) Systems Supporting Intel

®

Virtualization Technology May Not Trigger Appropriate Actions

AA15 X X Fixed

VM Exit Due to a MOV from CR8 May Cause an Unexpected

Memory Access

AA16 X X X

Plan

Fix

The Processor May Incorrectly Respond to Machine Checks

during VM Entry/Exit Transitions

AA17 X X Fixed

Power Down Requests May not be Serviced if a Power Down

Transition is Interrupted by an In-Target Probe Event in the

Presence of a Specific Type of VM Exit

AA18 X X Fixed

VM EXIT Due to TPR shadow Below Threshold May Improperly

Set and Cause "Blocking by STI" actions

AA19 X X X No Fix

Two Correctable L2 Cache Errors in Close Proximity May Cause

a System Hang

AA20 X X Fixed

A VM Exit due to SMI or INIT in Parallel with a Pending FP

Exception May Not Correctly Clear the Interruptibility State Bits

AA21 X X X No Fix Processor May Hang with a 25% or Less STPCLK# Duty Cycle

AA22 X X Fixed

Attempting to Use an LDT Entry when the LDTR Has Been

Loaded with an Unusable Segment May Cause Unexpected

Memory Accesses

AA23 X X X No Fix

Machine Check Exceptions May not Update Last-Exception

Record MSRs (LERs)

AA24 X X Fixed

VM Entry/Exit Writes to LSTAR/SYSCALL_FLAG MSR's May

Cause Incorrect Data to be Written to Bits [63:32]

AA25 X X X No Fix

Writing the Local Vector Table (LVT) when an Interrupt is

Pending May Cause an Unexpected Interrupt

AA26 X X Fixed

At a Bus Ratio of 13:1, RCNT and Address Parity May be

Incorrect

AA27 X X Fixed

The Execution of a VMPTRLD Instruction May Cause an

Unexpected Memory Access

AA28 X X Fixed

The Execution of VMPTRLD or VMREAD May Cause an

Unexpected Memory Access

AA29 X X Fixed

On a “Failed VM-entry” VM Exit, the VMCS Pointer May have

Incorrect Value

Loading...

Loading...