KD-S685/KD-S585

1-15

Description of major ICs

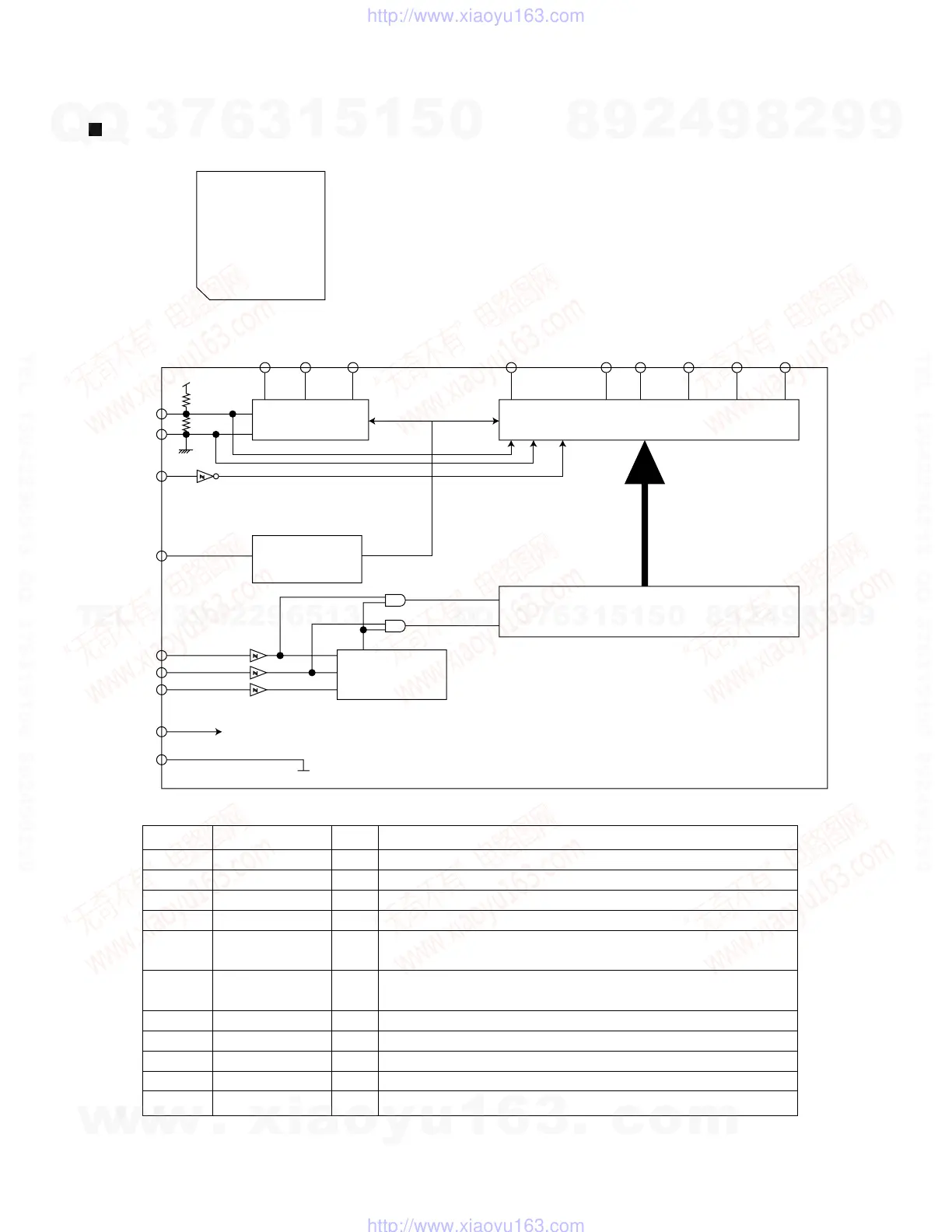

PT6523LQ (IC601) : LCD driver

1. Pin layout

2. Block digagram

3. Pin functions

1 ~ 16

48 ~ 33

32

~

17

49

~

64

COM1

VDD1

COMMON

DRIVER

CLOCK

GENERATOR

ADDRESS

DETECTOR

VDD2

VDD

VSS

INH

OSC

DI

CLK

CE

COM2 COM3

SEGMENT DRIVER & LATCH

SHIFT REGISTER

SG62 -------- SG5 SG4 SG3 SG2 SG1

Pin No.

1~52

53~55

56

57

58

59

60

61

62

63

64

I/O

O

O

-

I

I

I

-

I/O

I

I

I

Function

Segment output pin

Common driver output pin

Power supply

Display off control input pin

Used for 2/3 bias voltage when the bias voltages are

provided externally

Used for 1/3 bias voltage when the bias voltages are

provided externally

Ground pin

Oscillation Input/Output pin

Chip enable pin

Synchronization clock

Transfer data pin

Symbol

SG1~SEG52

COM1~COM3

VDD

INH

VDD1

VDD2

VSS

OSC

CE

CLK

DI

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...