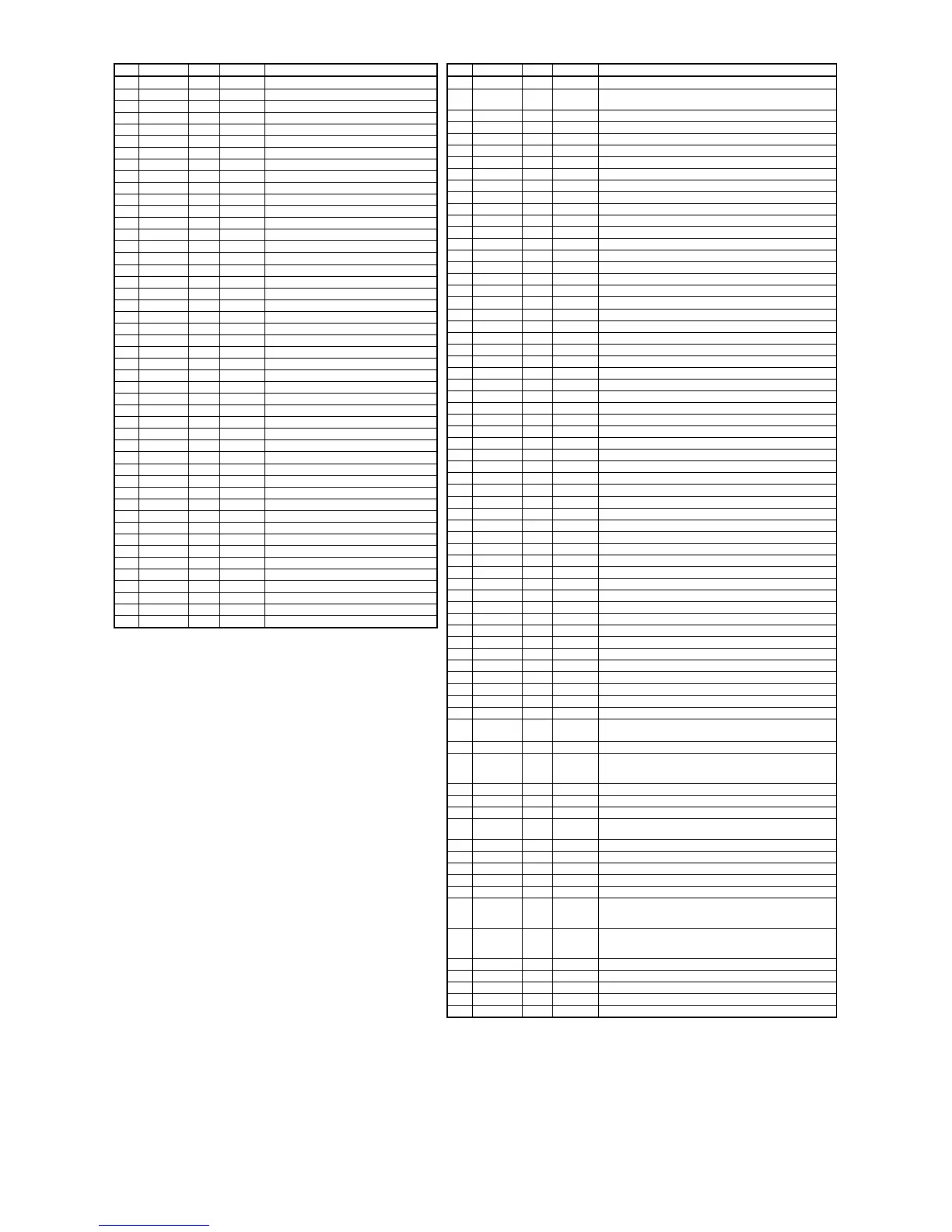

125

No. Name I/O

1

Attribute Functional Description

1 VSS P - Digital Ground

2 XTCK1 In CMOS Input pin, for testing only (Connect to Ground)

3 XSM In CMOS Input pin, for testing only (Connect to VDDE)

4 XTST In CMOS Input pin, for testing only (Connect to VDDE)

5 MST In CMOS Input pin, for testing only (Connect to Ground)

6 SMCK In CMOS Input pin, for testing only (Connect to VDDE)

7 DC9 In CMOS Input pin for color signal (MSB)

8 DC8 In CMOS Input pin for color signal

9 DC7 In CMOS Input pin for color signal

10 VDDI P - VDD for Core (2.5V)

11 VSS P - Digital Ground

12 DC6 In CMOS Input pin for color signal

13 DC5 In CMOS Input pin for color signal

14 DC4 In CMOS Input pin for color signal

15 DC3 In CMOS Input pin for color signal

16 VDDE P - VDD for I/O (3.3V)

17 DC2 In CMOS Input pin for color signal

18 DC1 In CMOS Input pin for color signal

19 DC0 In CMOS Input pin for color signal (LSB)

20 DY0 In CMOS Input pin for luminance signal (LSB)

21 VSS P - Digital Ground

22 DY1 In CMOS Input pin for luminance signal

23 DY2 In CMOS Input pin for luminance signal

24 DY3 In CMOS Input pin for luminance signal

25 DY4 In CMOS Input pin for luminance signal

26 DY5 In CMOS Input pin for luminance signal

27 DY6 In CMOS Input pin for luminance signal

28 DY7 In CMOS Input pin for luminance signal

29 DY8 In CMOS Input pin for luminance signal

30 DY9 In CMOS Input pin for luminance signal (MSB)

31 VSS P - Digital Ground

32 DI0 In CMOS Input pin for through data (LSB)

33 DI1 In CMOS Input pin for through data

34 DI2 In CMOS Input pin for through data

35 DI3 In CMOS Input pin for through data

36 DI4 In CMOS Input pin for through data

37 DI5 In CMOS Input pin for through data

38 DI6 In CMOS Input pin for through data

39 DI7 In CMOS Input pin for through data

40 VDDI P - VDD for Core (2.5V)

41 VSS P - Digital Ground

42 DI8 In CMOS Input pin for through data

43 DI9 In CMOS Input pin for through data (MSB)

44 DH In Schmitt Input pin for horizontal synchronization signal

45 DV In Schmitt Input pin for vertical synchronization signal

46 VDDE P - VDD for I/O (3.3V)

47 F1 In CMOS Input pin for field identification signal

1

“In”: input pin, “Out”: output pin, “Inout”: input/output pin, “P”: power supply or ground pin.

2

Neither Pull-up nor Pull down is done at the input pins. Be sure not set to Open.

3

The SDA pin becomes an input pin at Reset. Otherwise it works normally.

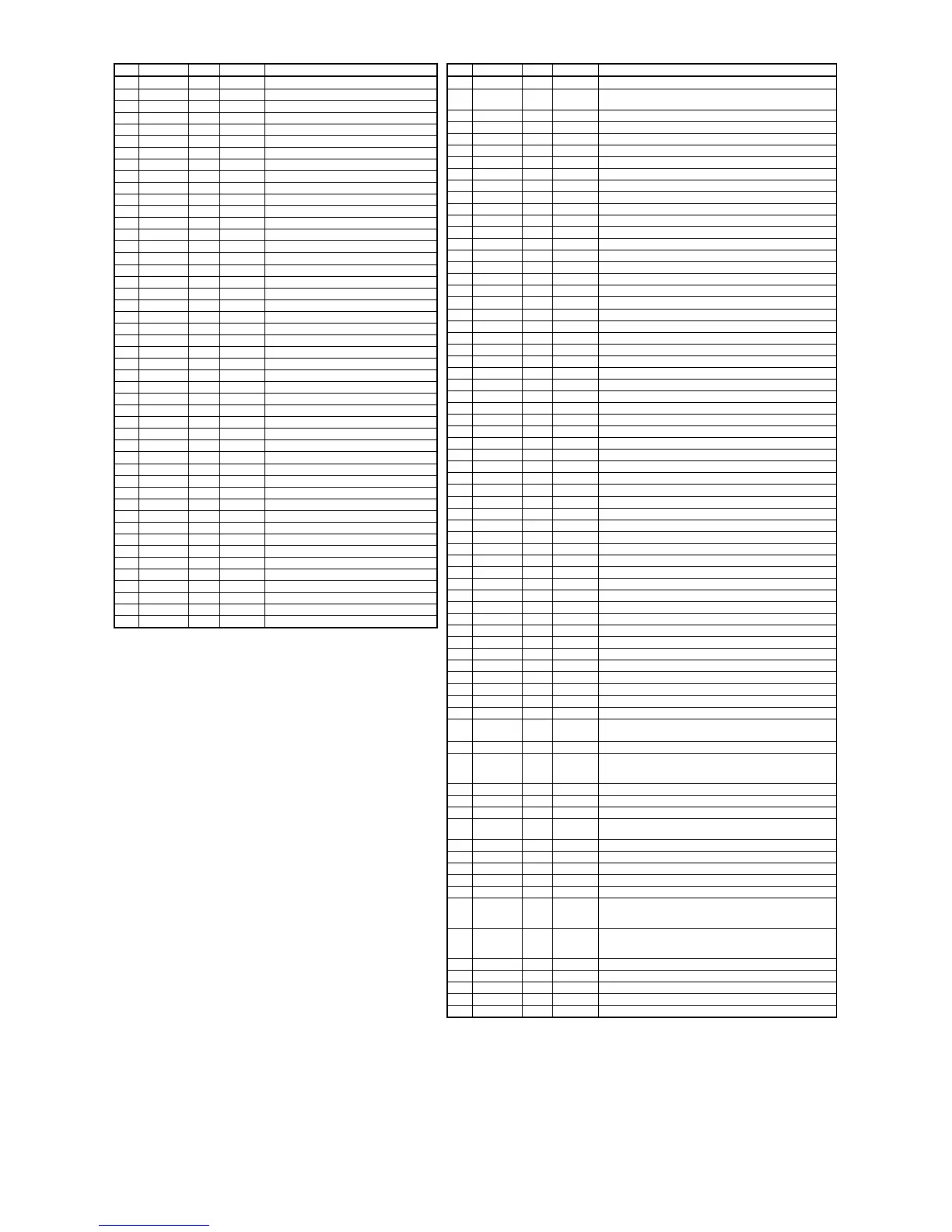

No. Name I/O

1

Attribute Functional Description

48 ALSB In CMOS Setting pin for I

2

C slave address

49 SDA Inout

Schmitt,

4mA

Input/ output pin for I

2

C data

50 SCL In Schmitt Input pin for I

2

C clock

51 VSS P - Digital Ground

52 NRST In Schmitt Input pin for system reset (Low Active)

53 TEST0 In CMOS Input pin, for testing only (Connect to Ground)

54 TEST1 In CMOS Input pin, for testing only (Connect to Ground)

55 TEST2 In CMOS Input pin, for testing only (Connect to Ground)

56 TEST3 In CMOS Input pin, for testing only (Connect to Ground)

57 QB0 Out 4mA Output pin for image data B (LSB)

58 QB1 Out 4mA Output pin for image data B

59 OVDDE1 P - VDD for I/O (3.3V)

60 VDDI P - VDD for Core (2.5V)

61 VSS P - Digital Ground

62 QB2 Out 4mA Output pin for image data B

63 QB3 Out 4mA Output pin for image data B

64 QB4 Out 4mA Output pin for image data B

65 QB5 Out 4mA Output pin for image data B

66 QB6 Out 4mA Output pin for image data B

67 QB7 Out 4mA Output pin for image data B

68 QB8 Out 4mA Output pin for image data B

69 QB9 Out 4mA Output pin for image data B (MSB)

70 VDDI P - VDD for Core (2.5V)

71 VSS P - Digital Ground

72 QG0 Out 4mA Output pin for image data G (LSB)

73 QG1 Out 4mA Output pin for image data G

74 QG2 Out 4mA Output pin for image data G

75 QG3 Out 4mA Output pin for image data G

76 VDDE P - VDD for I/O (3.3V)

77 QG4 Out 4mA Output pin for image data G

78 QG5 Out 4mA Output pin for image data G

79 QG6 Out 4mA Output pin for image data G

80 QG7 Out 4mA Output pin for image data G

81 VSS P - Digital ground

82 QG8 Out 4mA Output pin for image data G

83 QG9 Out 4mA Output pin for image data G (MSB)

84 QR0 Out 4mA Output pin for image data R (LSB)

85 QR1 Out 4mA Output pin for image data R

86 QR2 Out 4mA Output pin for image data R

87 QR3 Out 4mA Output pin for image data R

88 QR4 Out 4mA Output pin for image data R

89 QR5 Out 4mA Output pin for image data R

90 QR6 Out 4mA Output pin for image data R

91 VSS P - Digital Ground

92 OVDDE2 P - VDD for I/O (3.3V)

93 QR7 Out 4mA Output pin for image data R

94 QR8 Out 4mA Output pin for image data R

95 QR9 Out 4mA Output pin for image data R (MSB)

96 QV Out 4mA Output pin for vertical synchronization signal

97 QH Out 4mA Output pin for horizontal synchronization signal

98 QDE Out 4mA Output pin for data enable signal

99 QCLK Out 8mA Output pin for pixel clock

100 VDDI P - VDD for Core (2.5V)

101 VSS P - Digital Ground

102 EXCLK In CMOS Input pin for pixel clock for use of external PLL.

Be sure to connect this to Ground before using built-in PLL.

103 OVDDE3 P - VDD for I/O (3.3V)

104 PH1 Out 2mA

Output pin #1 for signals for phase comparison of external PLL

(Reference)

Be sure to set this to N.C. before using built-in PLL.

105 N.C. - - Pin for separation of power supply. Set this to N.C.

106 AVS1 P - Analog Ground exclusive for PLL

107 AVD1 P - Analog VDD exclusive for PLL (3.3V)

108 CPO Out Analog

Output pin for charge pump for built-in PLL.

Connect this to VCI via loop filter.

109 N.C. - - Pin for separation of power supply. Set this to N.C.

110 VCI In Analog VCO input pin for built-in PLL

111 AVS2 P - Analog Ground exclusive for PLL

112 AVD2 P - Analog VDD exclusive for PLL (3.3V)

113 N.C. - - Pin for separation of power supply. Set this to N.C.

114 PH2 Out 2mA

Output pin #2 for signals for phase comparison of external PLL

(Feedback)

Be sure to set this to N.C. before using built-in PLL.

115 PLLEN In CMOS

Selection pin for built-in PLL/External PLL

Connect this to VDDE before using built-in PLL. Connect this to

Ground before using external PLL.

116 OVDDE4 P - VDD for I/O (3.3V)

117 DCLK In CMOS Input pin for 27MHz clock

118 OVSS1 P - Digital Ground

119 DCLKP In CMOS Setting pin for polarity of DCLK

120 VDDI P - VDD for Core (2.5V)

Loading...

Loading...