LOGIC

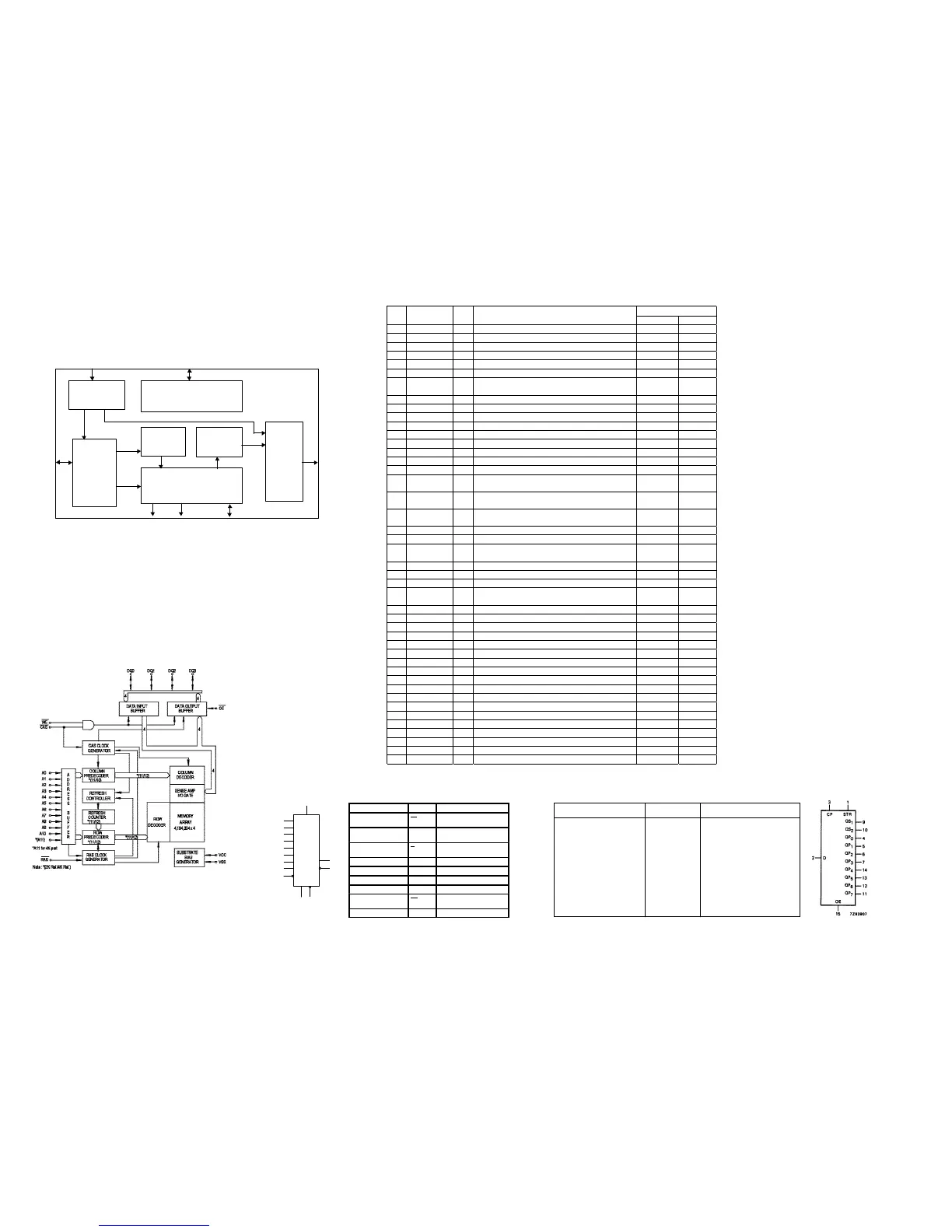

Pin PIN NAME I/O FUNCTION

HL

1 VCC -- POWER SUPPLY -- --

2 XQOK Ipu SUB CODE-Q OK SIGNAL FROM CPU -- OK

3 XWRE Ipu WRITE ENABLE SIGNAL FROM CPU -- PERMIT

4 XEMP O READ INHIBIT SIGNAL TO CPU -- INHIBIT

5 XWIH O WRITE INHIBIT SIGNAL TO CPU -- INHIBIT

6 XCAS2 O DRAM CAS2 CONTROL -- --

7 CHDT

O

DATA COMPARATIVE MONITOR SIGNAL

OUTPUT TO CPU

COMPARE

--

8 A10 O DRAM ADDRESS 10 -- --

9 CLK I 16.9344MHz CLOCK INPUT -- --

10 GND -- GROUND -- --

11 DATI Ics AUDIO DATA INPUT -- --

12 LRCI Ics AUDIO L/R CLOCK INPUT Lch Rch

13 BCKI Ics AUDIO BIT CLOCK INPUT -- --

14 BCKO O AUDIO BIT CLOCK OUTPUT -- --

15 LRCO O AUDIO L/R CLOCK OUTPUT Lch Rch

16 DATO O AUDIO DATA OUTPUT -- --

17 XROF Ics RAM OVERFLOW FROM SIGNAL PROCESSOR IC --

OVER

FLOW

18 RFCK Ipu

FRAME CLOCK FROM SIGNAL PROCESSOR IC,

DERIVED FROM THE CRYSTAL ACCURACY

-- --

19 SCOR I

SUB CODE SYNC DETECT SIGNAL FROM

SIGNAL PROCESSOR IC

-- --

20 XRST Ics SYSTEM RESET -- RESET

21 SDTO O SERIAL DATA OUTPUT TO CPU -- --

22 XSOE Ipu

SERIAL DATA OUTPUT PERMISSION SIGNAL

INPUT FROM CPU

--

PERMIT

23 TEST Ipd TEST MODE -- --

24 XLT Ics LATCH INPUT FROM CPU -- --

25 SDTI Ics SERIAL DATA INPUT FROM CPU -- --

26 SCK Ics

SERIAL DATA TRANSFER CLOCK INPUT FROM

CPU

-- --

27 XCAS1/XOE O DRAM CAS1/OE CONTROL -- --

28 XCAS0 O DRAM CAS0 CONTROL -- --

29 D2 I/O DRAM DATA 2 -- --

30 D3 I/O DRAM DATA 3 -- --

31 D0 I/O DRAM DATA 0 -- --

32 D1 I/O DRAM DATA 1 -- --

33 XWE O DRAM WE CONTROL -- --

34 XRAS O DRAM RAS CONTROL -- --

35 A9 O DRAM ADDRESS 9

36 A8 O DRAM ADDRESS 8

37 A7 O DRAM ADDRESS 7

38 A6 O DRAM ADDRESS 6

39 A5 O DRAM ADDRESS 5

40 A4 O DRAM ADDRESS 4

41 A0 O DRAM ADDRESS 0

42 A1 O DRAM ADDRESS 1

43 A2 O DRAM ADDRESS 2

44 A3 O DRAM ADDRESS 3

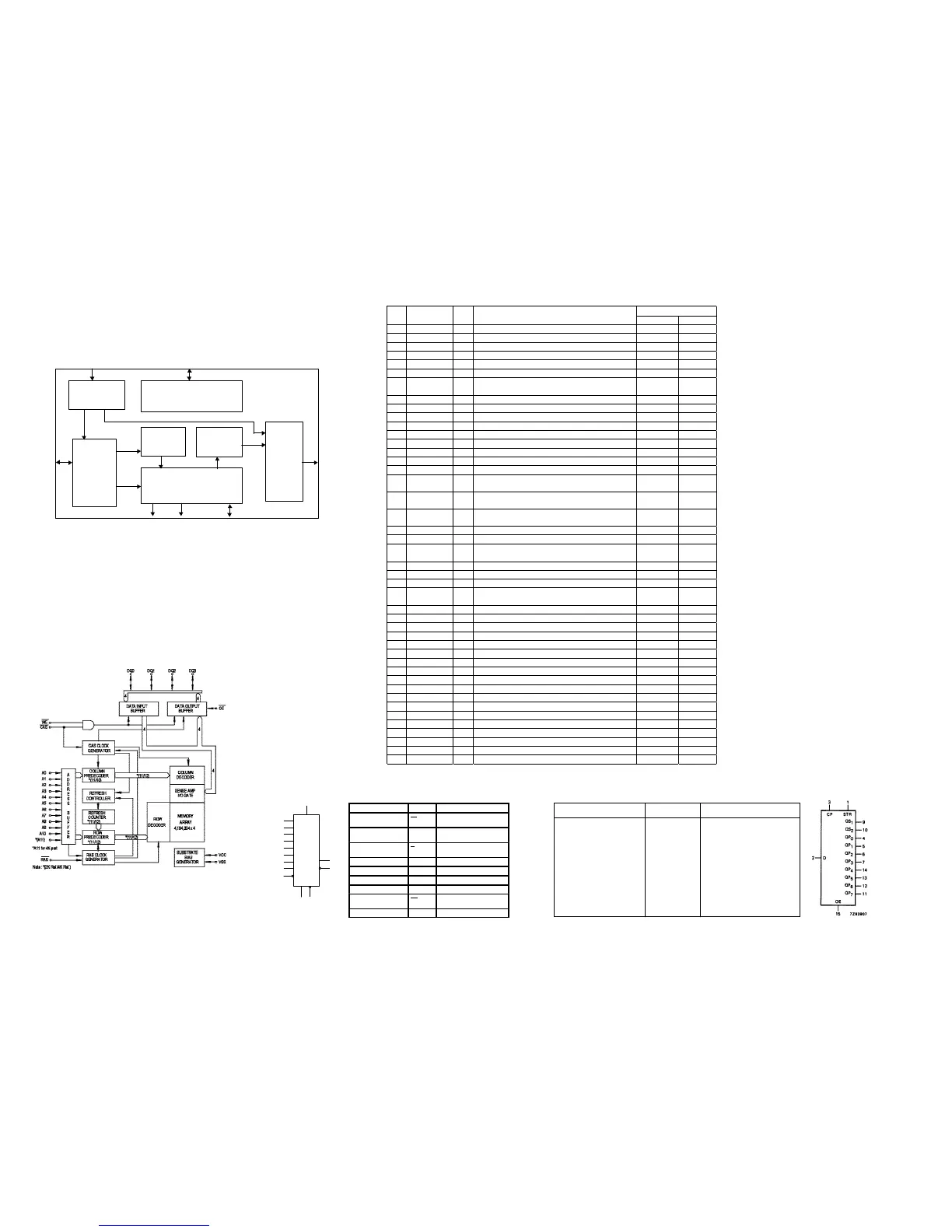

9

10

Q

7

CE

CP

PL

D

7

D

6

D

5

D

4

D

3

D

2

D

0

D

S

D

1

1

215

6

5

4

3

14

13

12

11

Q

7

7

PIN NUMBER SYMBOL FUNCTION

1

PL

Asynchronous parallel load

input (active LOW)

2 CP

Clock input (LOW to

HIGH, edge-triggered)

7 Q

7

Complementary output from

the last stage

8 GND Ground (0 V)

9 Q

7

Serial output from last stage

10 D

S

Serial data input

11, 12, 13, 14, 3, 4, 5, 6 D

0

to D

7

Parallel data inputs

15 CE

Clock enable input

(active LOW)

16 V

CC

Positive supply voltage

QU57 QU58 : 74HC165

PIN NO. SYMBOL NAME AND FUNCTION

1 STR strobe input

2 D serial input

3 CP clock input

4, 5, 6, 7,14, 13, 12, 11 QP

0

to QP

7

parallel outputs

8 GND ground (0 V)

9, 10 QS

1

,Q S

2

serial outputs

15 OE output enable input

16 V

CC

positive supply voltage

Loading...

Loading...