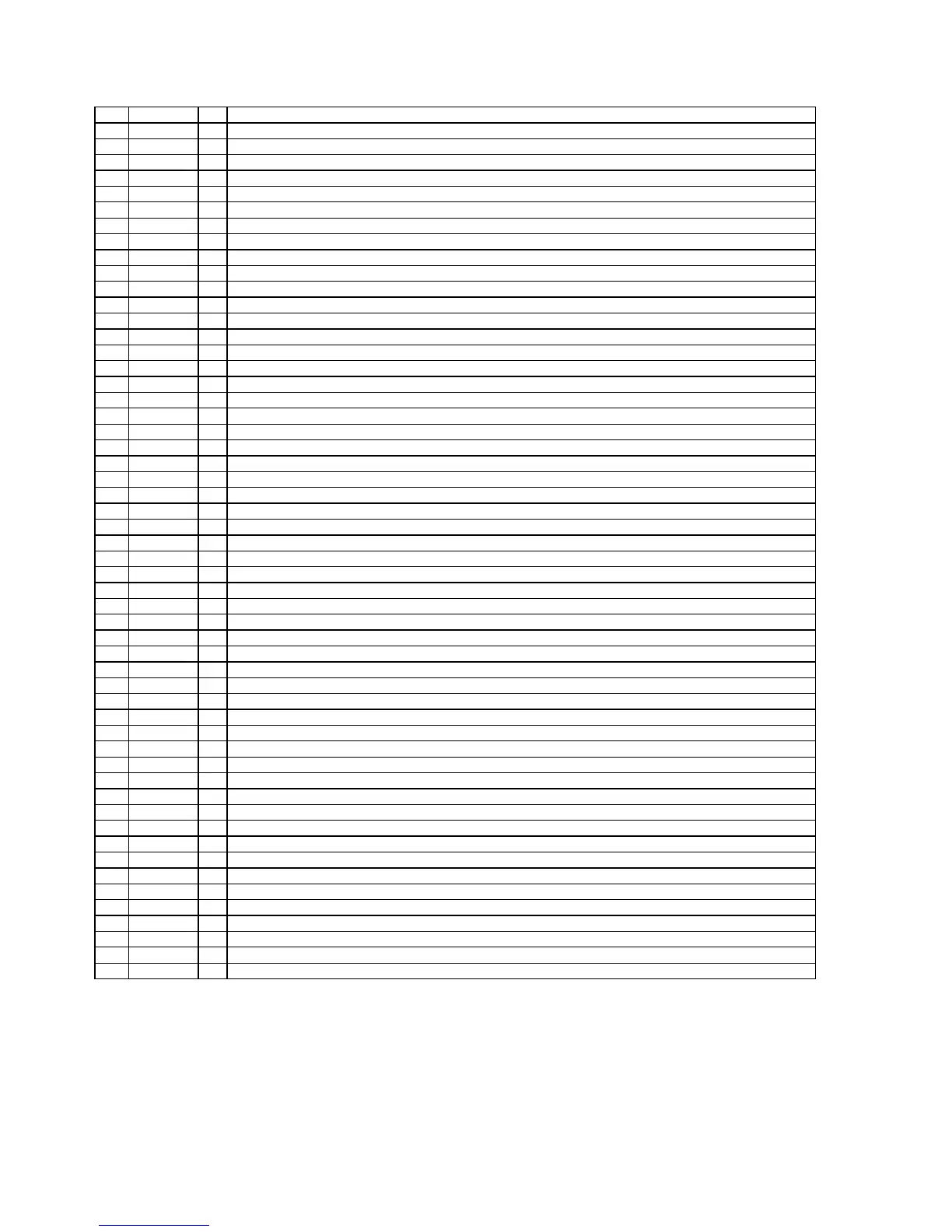

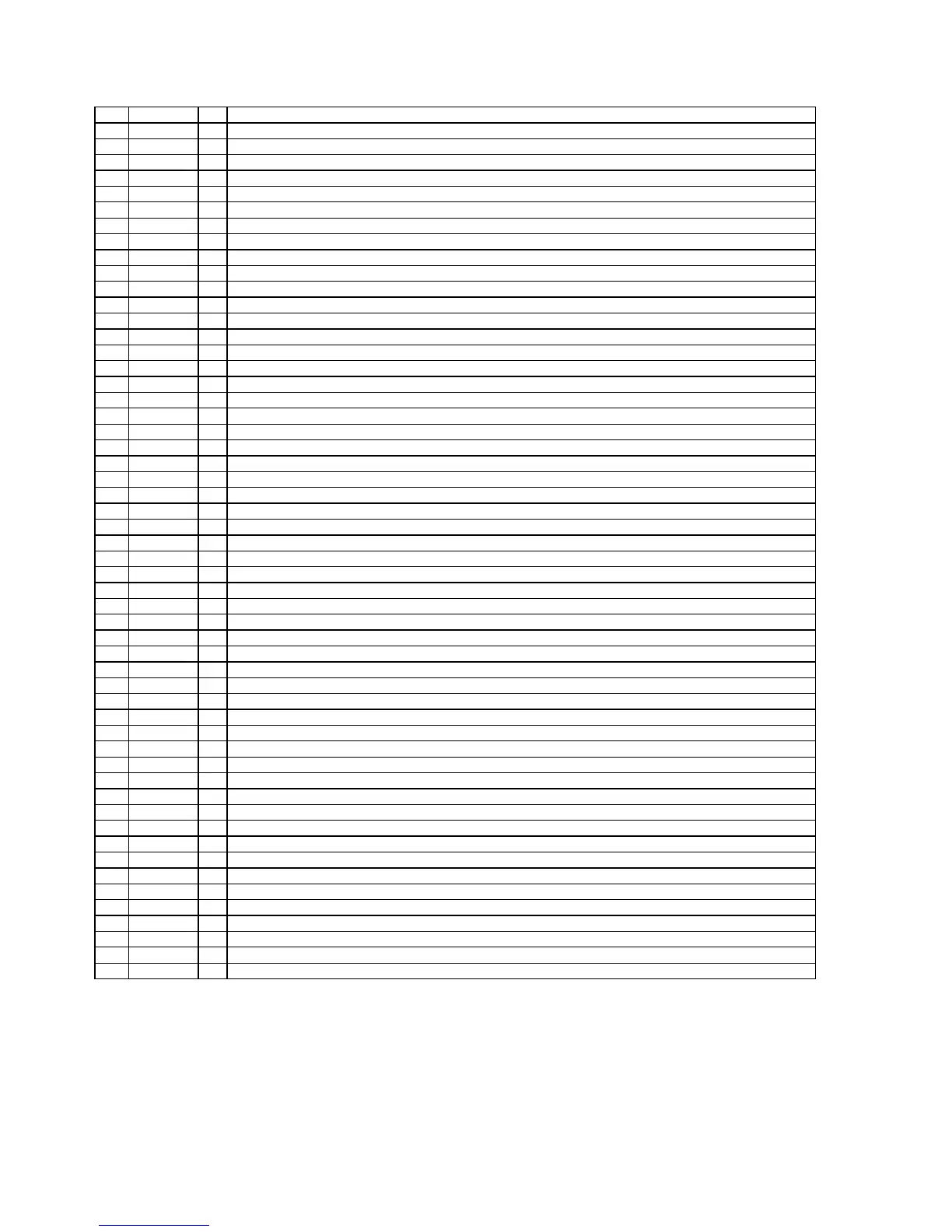

3-9

No. Pin Name I/O Functions

123 WCK I Operation clock for PSP physical disc mark detection.

124 WAVDD - +2.5V Power. A/D Power supply for PSP physical disc mark detection.

125 WAVDD - +2.5V Power. A/D Power supply for PSP physical disc mark detection.

126 WARFI Ai Analog RF signal input terminal for PSP physical disc mark detection.

127 WAVRB Ai A/D bottom reference terminal for PSP physical disc mark detection.

128 WAVSS - A/D Ground terminal for PSP physical disc mark detection.

129 WAVSS - A/D Ground terminal for PSP physical disc mark detection.

130 VSIO - Ground for I/O.

131 DQ7 I/O SDRAM data input/output terminal. (MSB)

132 DQ6 I/O SDRAM data input/output terminal.

133 DQ5 I/O SDRAM data input/output terminal.

134 DQ4 I/O SDRAM data input/output terminal.

135 VDIO - +3.3V Power for I/O.

136 DQ3 I/O SDRAM data input/output terminal.

137 DQ2 I/O SDRAM data input/output terminal.

138 DQ1 I/O SDRAM data input/output terminal.

139 DQ0 I/O SDRAM data input/output terminal. (LSB)

140 VSIO - Ground for I/O.

141 DCLK O Clock output terminal for SDRAM.

142 DCKE O Clock enable output terminal for SDRAM.

143 XWE O Write enable output terminal for SDRAM.

144 XCAS O Column address strobe output terminal for SDRAM.

145 XRAS O Row address strobe output terminal for SDRAM.

146 VDIO - +3.3V Power for I/O.

147 TESTO O Output terminal for TEST. (open)

148 A11 O Address output terminal for SDRAM. (MSB)

149 A10 O Address output terminal for SDRAM.

150 VSC - Ground for CORE.

151 A9 O Address output terminal for SDRAM.

152 A8 O Address output terminal for SDRAM.

153 VDC - +2.5V Power for CORE.

154 A7 O Address output terminal for SDRAM.

155 A6 O Address output terminal for SDRAM.

156 A5 O Address output terminal for SDRAM.

157 A4 O Address output terminal for SDRAM.

158 VSIO - Ground for I/O.

159 A3 O Address output terminal for SDRAM.

160 A2 O Address output terminal for SDRAM.

161 A1 O Address output terminal for SDRAM.

162 A0 O Address output terminal for SDRAM. (LSB)

163 VDIO - +3.3V Power for I/O.

164 XSRQ O Output terminal of the Data Request signal inputted a front-end processor.

165 XSHD I Input terminal of the header Flag outputted from a front-end processor.

166 SDCK I Input terminal of the data conveyance Clock outputted from a front-end processor.

167 XASK I Input terminal of the data valid Flag outputted from a front-end processor.

168 SDEF I Input terminal of the error Flag outputted from a front-end processor.

169 SD0 I Input terminal of the stream Data outputted from a front-end processor.

170 SD1 I Input terminal of the stream Data outputted from a front-end processor.

171 SD2 I Input terminal of the stream Data outputted from a front-end processor.

172 SD3 I Input terminal of the stream Data outputted from a front-end processor.

173 SD4 I Input terminal of the stream Data outputted from a front-end processor.

174 SD5 I Input terminal of the stream Data outputted from a front-end processor.

175 SD6 I Input terminal of the stream Data outputted from a front-end processor.

176 SD7 I Input terminal of the stream Data outputted from a front-end processor.

Ipu: Pull-up input Ipd: Pull-down input Ai: Analog input

IC401 : CXD2753R

Loading...

Loading...