IC Data Sheets

EN 53QM15.2E LA 8.

2015-Sep-30

back to

div.table

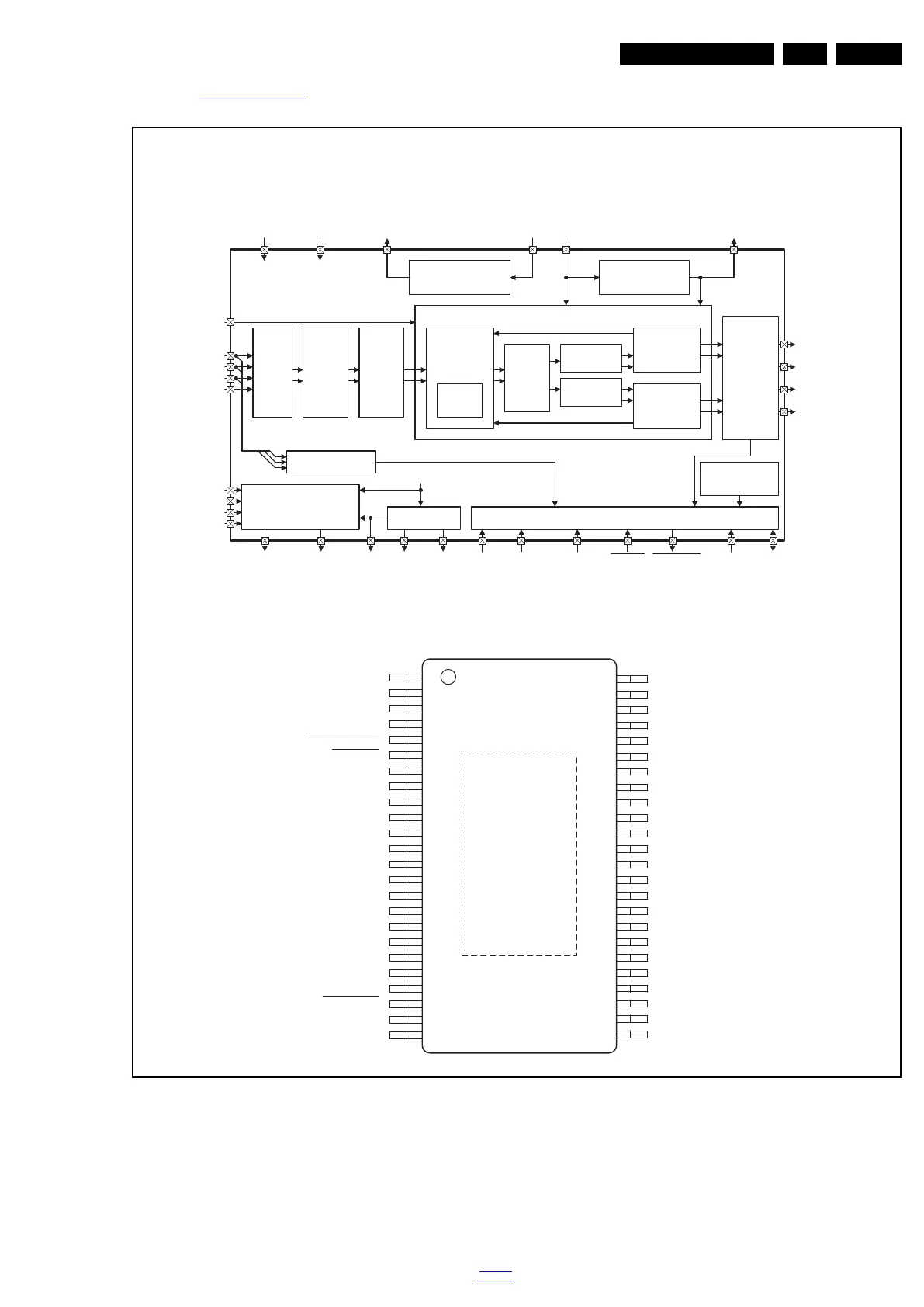

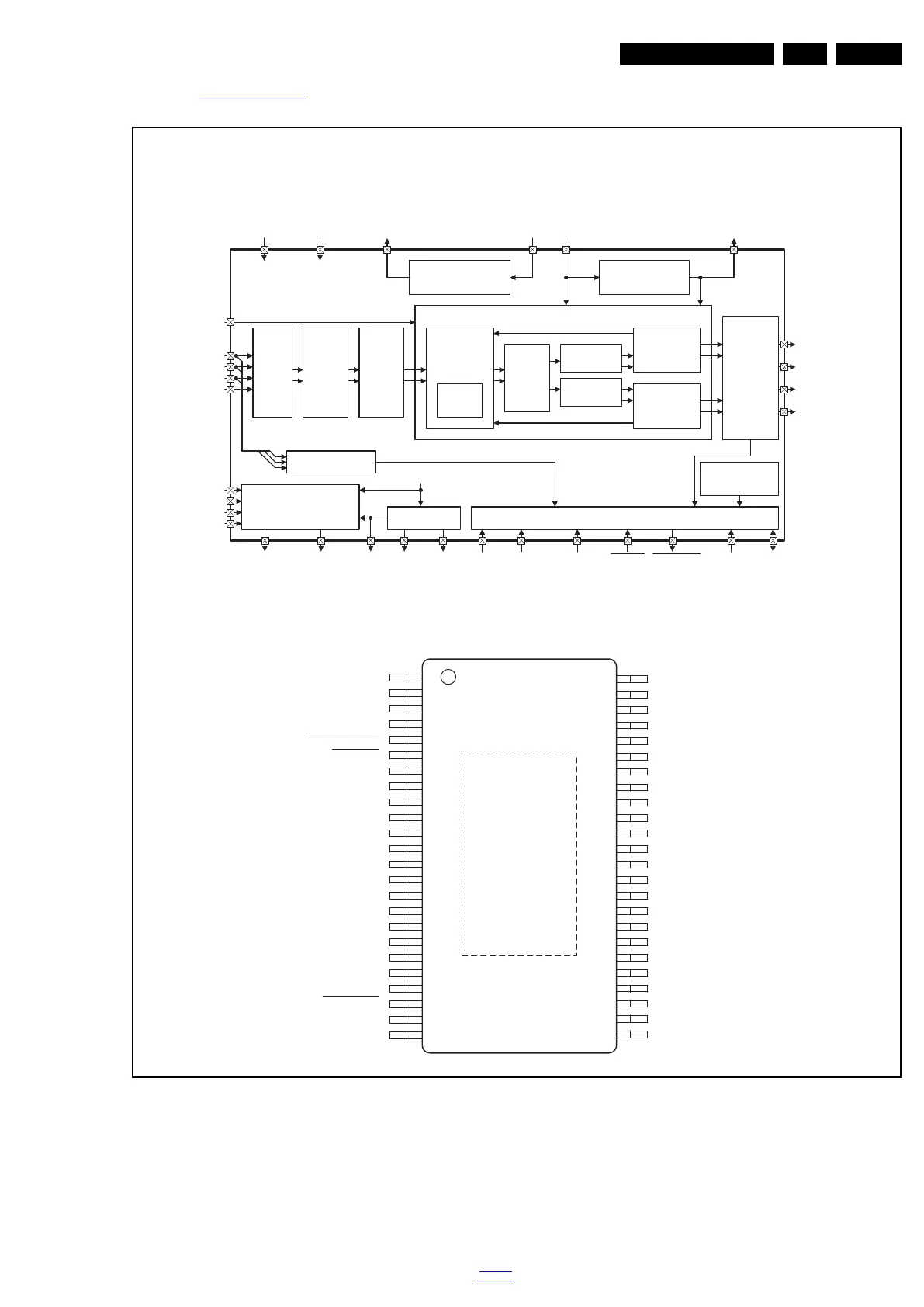

8.5 Diagram 10-6-6 DDR3x1, B06, TAS5760LDDCAR (IC U601)

Figure 8-6 Internal block diagram and pin configuration

19880_304.eps

Block diagram

Pinning information

PowerPAD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SFT_CLIP

ANA_REG

VCOM

ANA_REF

SPK_FAULT

SPK_SD

FREQ/SDA

PBTL/SCL

DVDD

SPK_GAIN0

SPK_GAIN1

PK_SLEEP/ADR

MCLK

SCLK

SDIN

LRCK

DGND

DR_INA-

DR_INA+

DR_OUTA

DRGND

DR_MUTE

DRVSS

DR_CN

GVDD_REG

GGND

AVDD

PVDD

PVDD

BSTRPA+

SPK_OUTA+

PGND

SPK_OUTA-

BSTRPA-

BSTRPB-

SPK_OUTB-

PGND

SPK_OUTB+

BSTRPB+

PVDD

PVDD

DR_INB-

DR_INB+

DR_OUTB

DR_UVE

DRGND

DRVDD

DR_CP

Clock Monitoring

Digital to

PWM

Conversion

Digital

Boost

&

Volume

Control

Soft

Clipper

Analog

Gain

Full Bridge

Power Stage

B

Serial

Audio

Port

DirectPath

TM

Ground

Centered Headphone /

Line Driver

Charge Pump Internal Control Registers and State Machines

Internal Reference

Regulators

Over-

Current

Protection

Full Bridge

Power Stage

A

Gate

Drives

Gate

Drives

Digital

Clipper

Die

Temp. Monitor

Internal Gate

Drive Regulator

Closed Loop Class D Amplifier

DR_INB+

DR_INB-

DR_INA+

DR_INA-

FT_CLIP

SPK_OUTB+

SPK_OUTB

SPK_OUTA+

SPK_OUTA

SCLK

SDIN

MCLK

LRCK

DDVAGER_ANADDVRDDDVD GVDD_REGPVDD

Internal

Voltage

Supplies

DRVDD

DR_OUTA DR_OUTB

DRVDD

DRVSS DR_CP

PBTL/

SCL

SPK_GAIN1

SPK_FAULT

SPK_SLEEP/

ADR

SPK_GAIN0

SPK_SD

FREQ/

SDA

DR_CN

Loading...

Loading...